Altera FPGA管脚弱上拉电阻详细设置方法

Posted yf869778412

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Altera FPGA管脚弱上拉电阻详细设置方法相关的知识,希望对你有一定的参考价值。

Altera FPGA管脚弱上拉电阻的软件设置方法

在使用 Altera 的 FPGA 时候, 由于系统需求, 需要在管脚的内部加上上拉电阻。 Quartus II 软件中在 Assignment Editor 中可以设置。具体过程如下:

1、在菜单 Assignments 中选择 Assignment Editor:

2、在弹出的界面里选择I/O Features:

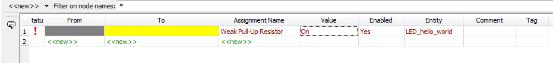

3、选择assignment name为弱上拉,value为on。

注意:目前自己知道在弱上拉时,value的值为on,value的值会根据assignment name选择不同而不同,例如下图。

4、查找需要上拉的端口:

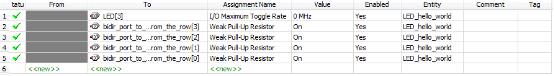

经过上面步骤后,如图:

前5步结果:

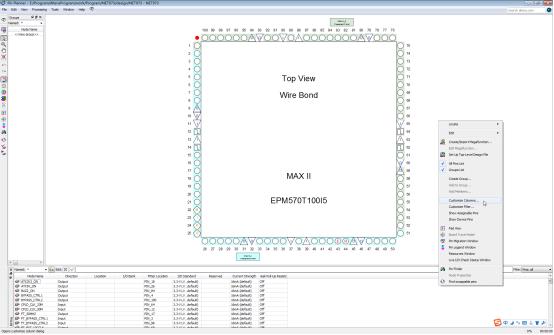

第6步结果:

备注:该窗口

有助于选择将要上拉的管脚。

5、保存然后再重新编译,设置完成。在.qsf中可以看到对应的端口已经上拉。

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sw1_n

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sw2_n

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to sw3_n

转载:https://wenku.baidu.com/view/a8d57d292e3f5727a4e9624d.html

另外一种方法:

以上是关于Altera FPGA管脚弱上拉电阻详细设置方法的主要内容,如果未能解决你的问题,请参考以下文章

Altera特殊管脚的使用(适用全系列Altera FPGA,MSEL区别除外)

[转]Altera特殊管脚的使用(适用全系列Altera FPGA,MSEL区别除外)-来自altera论坛

FPGA EP3C16F484C芯片 上电后管脚输出一个200ms左右的高脉冲, 怎样消除? 在quartus II 哪设置吗?

我想问一下 我的FPGA开发板晶振 是50m(外部时钟) 我想用50m作为我fpga设计电路的时钟 是直接把这个外部