如何评估zynq7000的功耗

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了如何评估zynq7000的功耗相关的知识,希望对你有一定的参考价值。

Zynq系列是赛灵思公司(Xilinx)推出的行业第一个可扩展处理平台,旨在为视频监视、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理与计算性能水平。该系列四款新型器件得到了工具和IP 提供商生态系统的支持,将完整的 ARM® Cortex™-A9 MPCore 处理器片上系统 (SoC) 与 28nm 低功耗可编程逻辑紧密集成在一起,可以帮助系统架构师和嵌入式软件开发人员扩展、定制、优化系统,并实现系统级的差异化。实际上,Zynq就是两大功能块:双核Arm的SoC和FPGA。根据Xilinx提供的手册,PS: 处理系统 (Processing System) , 就是与FPGA无关的ARM的SOC的部分。PL: 可编程逻辑 (Progarmmable Logic), 就是FPGA部分。这有点像xilinx以前推出的powerPC+FPGA平台。下图为官方文档中介绍的ZYNQ内部结构。

从图中可以看到,ZYNQ的绝大多数外设都是PL逻辑部分相连,比如说GPIO,IIS,XADC等等,所以如果我们要使用这些外设的话必须在PL逻辑部分对其进行配置。OK,下面我们就以一个简单的例子来看看如何使用PL和PS进行交互。在下面的例子中,我们通过设置8个开关来对应点亮8个LED灯。

首先打开XPS,由于XILINX内部已经帮我们做好了GPIO部分的IP核,所以我们只需要直接使用即可(如果要用自己的ip核,则可以使用ISE先把IP核写好再导入进来)。新建立一个工程,选择“Create New Project Using Base System Builder”,

填好项目工程文件的路径,其它不需要更改,直接点OK

由于我们用的就是ZEDBOARD,所以在这里我们选择的是ZYNQ开发板,直接点击NEXT,

该界面表示当前工程里已经默认把GPIO和4位的led包含进去了,由于我们这里和光放的ZYNQ开发板还有点差别,所以就不需要这些默认设置了,直接选中点击REMOVE,最后点击FINISH完成工程的建立。

双击图中所示的AXI General Purpose IO,添加该IP核到ZYNQ中,注意在Width中选择8,表示当前的GPIO的宽度为8,当然如果你需要更宽也可以进行其它设置,但最多不能超过32 位。我们这里的SW开关和LED都为8个,所以我们把宽度设置为8.一路点击OK按钮,把该IP核加入到工程中。

由于我们有SW开关和LED两个外设并且一个为输入一个为输出,所以还需要按照同样的方法再添加一个GPIO核。完成添加后看右边的BUS INTERFACES,可以看到GPIO 0和GPIO1均添加到了系统中。

点击PORT栏,进入到端口设置部分,在这里我们把一个GPIO设置为输出,它与8个LED灯相连,另外一个设置为输入,它与8个SW开关相连。完成设置后的结果如下图所示

下面就是编辑约束文件,给定义的端口分配管脚了,

双击project栏中的UCF,打开约束编辑(在这里有个问题,难道ISE14.2中没有专门的约束编辑器吗?),输入以下内容

上面表示8个LED等,下面表示8个SW按键,注意,在DS中,8个SW按键是连接到VCC_ADJ上的,所以我们这里使用LVCMOS18电平标准。完成这些设置后,依次点击Generate BitStream和Export Design按钮,完成流配置文件的生成和导出到SDK中。

上面就是PL部分的配置了,下面我们就根据PL的配置来进行PS部分的编程。打开SDK工具,新建工程(具体如何新建可以参考ZedBoard_CTT_v14.1文档,该文档在ZEDBOARD.org网站上有下载)后更改其中的main函数为以下形式

点击编译,成功生成ELF文件后即可进行下载,当然在下载ELF文件前还要先把FPGA的配置下载进去。

总结一下,zynq虽然是一个新的东西,但它的基本开发流程和开发原理和xilinx以往的产品基本一样,ISE,XPS,SDK等等的使用方法也基本相同,所不同的是,ZYNQ系列中包含了两个ARM核,极大的提高了系统的性能。

参考技术A 您好,很高兴能帮助您,

Zynq系列是赛灵思公司(Xilinx)推出的行业第一个可扩展处理平台,旨在为视频监视、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理与计算性能水平。该系列四款新型器件得到了工具和IP 提供商生态系统的支持,将完整的 ARM® Cortex™-A9 MPCore 处理器片上系统 (SoC) 与 28nm 低功耗可编程逻辑紧密集成在一起,可以帮助系统架构师和嵌入式软件开发人员扩展、定制、优化系统,并实现系统级的差异化。

实际上,Zynq就是两大功能块:双核Arm的SoC和FPGA。根据Xilinx提供的手册,PS: 处理系统 (Processing System) , 就是与FPGA无关的ARM的SOC的部分。PL: 可编程逻辑 (Progarmmable Logic), 就是FPGA部分。这有点像xilinx以前推出的powerPC+FPGA平台。下图为官方文档中介绍的ZYNQ内部结构。

从图中可以看到,ZYNQ的绝大多数外设都是PL逻辑部分相连,比如说GPIO,IIS,XADC等等,所以如果我们要使用这些外设的话必须在PL逻辑部分对其进行配置。OK,下面我们就以一个简单的例子来看看如何使用PL和PS进行交互。在下面的例子中,我们通过设置8个开关来对应点亮8个LED灯。

首先打开XPS,由于XILINX内部已经帮我们做好了GPIO部分的IP核,所以我们只需要直接使用即可(如果要用自己的ip核,则可以使用ISE先把IP核写好再导入进来)。新建立一个工程,选择“Create New Project Using Base System Builder”,

填好项目工程文件的路径,其它不需要更改,直接点OK

由于我们用的就是ZEDBOARD,所以在这里我们选择的是ZYNQ开发板,直接点击NEXT,

该界面表示当前工程里已经默认把GPIO和4位的led包含进去了,由于我们这里和光放的ZYNQ开发板还有点差别,所以就不需要这些默认设置了,直接选中点击REMOVE,最后点击FINISH完成工程的建立。

双击图中所示的AXI General Purpose IO,添加该IP核到ZYNQ中,注意在Width中选择8,表示当前的GPIO的宽度为8,当然如果你需要更宽也可以进行其它设置,但最多不能超过32 位。我们这里的SW开关和LED都为8个,所以我们把宽度设置为8.一路点击OK按钮,把该IP核加入到工程中。

由于我们有SW开关和LED两个外设并且一个为输入一个为输出,所以还需要按照同样的方法再添加一个GPIO核。完成添加后看右边的BUS INTERFACES,可以看到GPIO 0和GPIO1均添加到了系统中。

点击PORT栏,进入到端口设置部分,在这里我们把一个GPIO设置为输出,它与8个LED灯相连,另外一个设置为输入,它与8个SW开关相连。完成设置后的结果如下图所示

下面就是编辑约束文件,给定义的端口分配管脚了,

双击project栏中的UCF,打开约束编辑(在这里有个问题,难道ISE14.2中没有专门的约束编辑器吗?),输入以下内容

上面表示8个LED等,下面表示8个SW按键,注意,在DS中,8个SW按键是连接到VCC_ADJ上的,所以我们这里使用LVCMOS18电平标准。完成这些设置后,依次点击Generate BitStream和Export Design按钮,完成流配置文件的生成和导出到SDK中。

上面就是PL部分的配置了,下面我们就根据PL的配置来进行PS部分的编程。打开SDK工具,新建工程(具体如何新建可以参考ZedBoard_CTT_v14.1文档,该文档在ZEDBOARD.org网站上有下载)后更改其中的main函数为以下形式

点击编译,成功生成ELF文件后即可进行下载,当然在下载ELF文件前还要先把FPGA的配置下载进去。

总结一下,zynq虽然是一个新的东西,但它的基本开发流程和开发原理和xilinx以往的产品基本一样,ISE,XPS,SDK等等的使用方法也基本相同,所不同的是,ZYNQ系列中包含了两个ARM核,极大的提高了系统的性能。

你的采纳是我前进的动力,还有不懂的地方,请你继续“追问”!

如你还有别的问题,可另外向我求助;答题不易,互相理解,互相帮助!本回答被提问者和网友采纳

基于Zynq平台的EtherCAT主站方案实现

作者:陈秋苑 谢晓锋 陈海焕 广州虹科电子科技有限公司

摘 要:EtherCAT 是开放的实时以太网通讯协议,由德国倍福自动化有限公司研发。EtherCAT 具有高性能、低成本、容易使用等特点,目前在工业自动化领域有着广泛的应用。Zynq-7000 是赛灵思公司(Xilinx)推出的行业第一个全可编程 SoC 产品, 它将双核 ARM Cortex-A9 处理器,低功耗可编程逻辑以及常用的外设紧密集成在一起。ZedBoard 是基于 XC7Z020 器件的低成本开发板,此板可以运行基于 Linux,Android,WinCE 或其他嵌入式 OS/ RTOS 的设计。

KPA EtherCAT 主站是一套质量稳定、知名度和性价比较高的 EtherCAT 协议栈,有较大参考价值。本文将介绍 KPA EtherCAT 主站在 Zynq 平台的移植与测试。

目录

第一节 EtherCAT 简介

第二节 KPA EtherCAT 软件包简介和使用

第三节 KPA EtherCAT 主站简介和移植

第四节 EtherCAT 主站程序测试

第五节 EtherCAT 测试程序分析

第六节 主站开发包申请试用

1、EtherCAT 简介

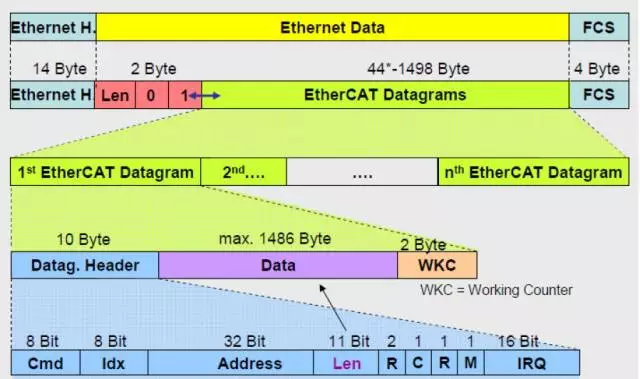

EtherCAT(以太网控制自动化技技)是一种用于确定性以太网的高性能工业通信协议,它扩展了 IEEE 802.3 以太网标准,使得数据传输中具有可预测性定时及高精度同步等特点。这个开放性标 准作为 IEC 61158 的组成部分,常用于机械设计及运动控制等应用中。EtherCAT 采用标准的 IEEE802-3 以太网帧,帧结构如图 1。EtherCAT 协议直接用标准以太网的帧格式传输数据,并不修改其基本结构。

图 1: EtherCAT 数据帧

EtherCAT 实现了 CANopen 协议,在 CANopen 中周期性的数据通过 PDO(过程数据对象)来传输,PDO 优先级较高,可用于实时传输。非周期性的数据比如配置参数和对象字典等则通过 SDO(服务数据对象)来传输。

每个 PDO 都包含单个或多个从设备的地址,这种数据加地址的结构(附带用于校验的传输计数位)组成了 EtherCAT 的报文。每个 Ethernet 帧可能包含数个报文,而一个周期中可能需要多帧来传送所需的所有报文。

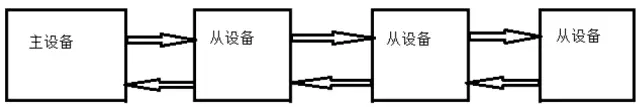

传统的以太网通信解决方案从站先接受以太网数据包,然后解释和复制过程数据,最后转发数据。而EtherCAT 以太网帧在特殊的硬件模块的帮助下可以实现在传输的同时被处理。每个从节点都有 FMMU(现场总线存储管理单元),FMMU 会对经过的数据包进行地址分析,发现是本节点的 数据就会读取,同时报文转发给下一个设备。同样在报文通过的时候也可以插入需要传输的数据。读取/插入/转发数据的整个过程,报文只有几纳秒的延迟。如图 2 所示,设想以太网的帧就像行驶中的火车,EtherCAT 报文是每节火车车厢,PDO 数据的比特就是车厢内的乘客,这些数据可以被提取并插入到合适的从设备中。整辆火车不停止地穿越所有从设备,在末端从设备处又掉头,重新反向穿越所有从设备。(注:EtherCAT不仅支持主从通讯,也支持从从通讯即S2S)

图 2: EtherCAT 数据传输

2、EtherCAT 主从站软硬件简介

2.1KPA EtherCAT 主站软件介绍

KPA EtherCAT主站软件根据功能不同,提供了Basic,Standard,Premium以及Extension四个版本主站协议栈,因此除了支持ETG1500定义了Class A和Class B两种主站类型外,KPA还支持一些拓展功能比如:Data- and Frame-Logger(记录数据和报文)、Access Rights(设置不同的访问权限)Multi Master(多主站,冗余)、Cable Redundancy (线缆冗余)、Hot-Connect(热插拔)、其他。

提供了基于多种不同硬件平台和OS的现成开发包,支持SoC(ARM+FPGA)/ARM/X86 /PowerPC等主流硬件平台,支持Linux(Xenomai/RT-preempt)/ Windows(INtime/RTX)/ QNX/ Ucos/ Vxworks等。几乎满足目前所有用户主站开发要求的一款主站方案。

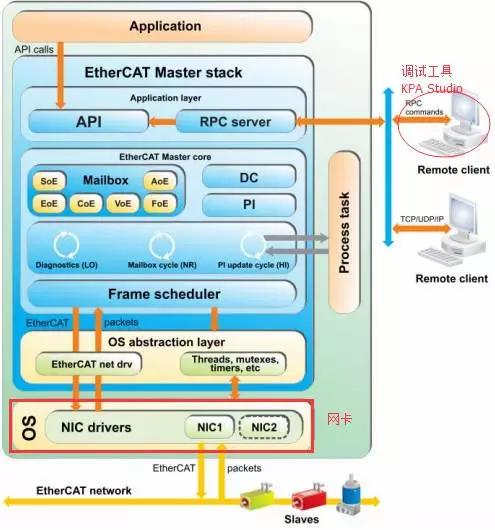

KPA主站协议栈采用模块化的架构,可以实现每个特殊的项目应用。它使得主站可以自由扩展以适应不同大小的应用程序、可以移植不同的操作系统和各种各样的硬件平台。每个模块可以单独定制化或者二次开发,而且不会破坏其他模块的完整性。主站结构如图3

图 3: KPA EtherCAT主站构架

KPA主要功能模块为:

1) 应用层:应用层负责与各种不同的编程/配置环境交互,负责与不同的应用或设备交互。确保在应用或过程任务端顺利访问主站功能函数;与主站通过Remote Procedure Calls服务交互,提供了TCP/IP以及UDP连接,比如:通过UDP与从站设备进行mailbox相关的通讯。

2) Mailbox Module:EtherCAT主站核心mailbox模块利用不同的协议处理服务数据对象(SDP),数据传输以及数据交换。支持CoE,FoE,EoE,SoE,VoE,AoE等邮箱服务。

3) Process Image Module过程映像模块:Process Image简称PI,它的地址是由EtherCAT network information (ENI) 文件提出的,ENI文件可由配置工具KPA Studio自动生成。从控制/过程任务访问过程映像是由主站接口执行的。

4) Distribution Clock分布时钟模块:使得所有的EtherCAT设备(包括主站和从站)总是能够共享相同的EtherCAT系统时间。这是通过补偿编译和漂移时间来实现的。

5) Frame Schedule Module帧调度模块:不同PDO采用不同的扫描周期。在配置工具KPA Studio里,用户可以单独定义每个从站的扫描速率。帧调度表模块管理EtherCAT帧速率,转发它们到EtherCAT网络驱动。

6) OSAL操作系统抽象层模块:包含与操作系统相关的功能函数的包装,比如处理线程、计时器、互斥量等;包括网络适配驱动器模块:从底层的网络实现提取主站堆栈的core核心

2.2KPA EtherCAT 主站硬件介绍

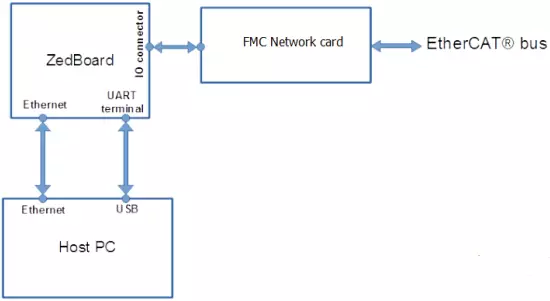

主站硬件主要由三部分组成见图4:PC端、Zedboard主站开发板以及外扩的FMC网卡。PC通过串口终端来实现操作系统指令输入,PC端上的EtherCAT网络诊断配置工具KPA EtherCAT Studio通过RPC服务连接Zedboard主站板,可以实现对主站和从站的配置,扫描生成网络配置文件。Zedboard作为EtherCAT主站板具体可参考 http://zedboard.org/product/zedboard 。

图 4:硬件架构图

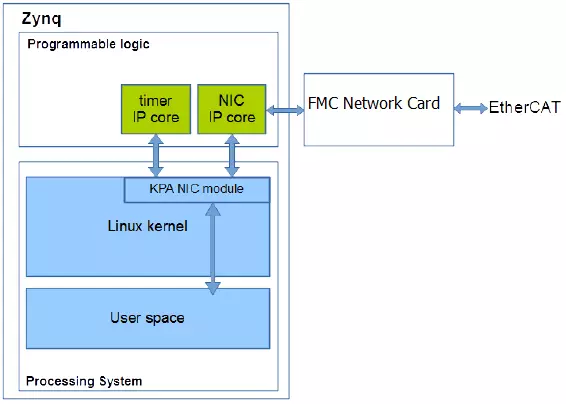

图 5:硬件内部架构

另外,KPA利用主站板的FPGA资源,独立外扩网卡,而不是使用主站板ARM上的网卡驱动,主站开发包中提供的Timer IP Core和NIC IPCore,利用逻辑单元PL,构建针对EtherCAT优化的MAC,提供了针对EtherCAT优化的NIC驱动,IP Core提供了Shift Sending Time设置,从端口降低有操作系统引起的数据帧抖动,从而优化了数据在收发时的抖动的问题。

3、KPA EtherCAT 主站移植

本方案基于Zynq平台的EtherCAT主站实现,系统采用改进后的实时linux系统,即在标准的linux操作系统内核中嵌套进一个微小、实时内核,改造成具有双内核的异构系统,所有实时任务都运行在微内核上,非实时的Linux 则作为实时内核的一项优先级最低的任务来托管所有的非实时任务,采用Linux3.8.13和Xenomai2.6.3,下面介绍怎么搭建Zedboard主站。

3.1Vivado 与 Xilinx SDK 工具安装

我们主要用到SDK里的交叉编译器,以及用它来生成FSBL与BOOT.BIN文件。

我分别在ubuntu和windows上都安装了xilinx的SDK。其中windows上的xilinx SDK不需要单独安装,等在安装Vivado的时候勾选下就可以了。 Ubuntu上的xilinx SDK安装文件网址是 http://www.xilinx.com/support/download/index.html/content/xilinx/en/down...

3.2Vivado 的下载安装

Vivado主要是用来配置xilinx的FPGA外设的,后面生成bitstream文件时需要用,以及我们更改SOC里的外设引脚配置以及配置管脚等等时是需要用到。Vivado的下载地址

http://www.xilinx.com/support/download/index.html/content/xilinx/en/down...

3.3给 Linux 内核代码打 Xenomai 实时补丁

zedboard上运行的linux内核可不是普通的linux内核源码,而是打了xenomai补丁的实时嵌入式操作系统。需要先给linux源码打上xenomai补丁后方可编译

Linux源码下载: https://github.com/Xilinx/linux-xlnx.git

Xenomai安装包下载: http://download.gna.org/xenomai/stable/xenomai-2.6.3.tar.bz2

给linux内核代码打xenomai实时补丁,可以参看xilinx的官方文档《Xenomai for Zynq》: http://www.wiki.xilinx.com/Xenomai+for+Zynq

3.4Linux 内核编译

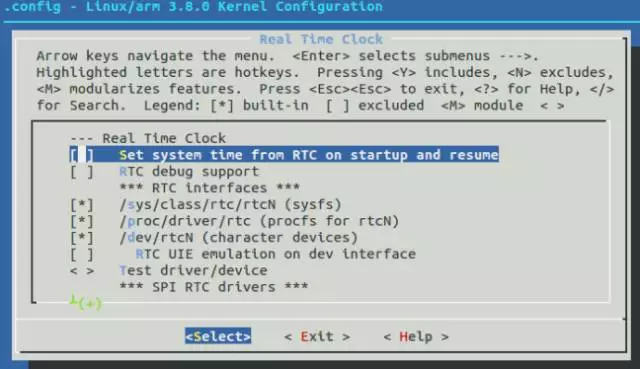

当xenomai补丁打好后,即可开始编译linux内核

图 6:Uboot编译

具体的ubuntu编译方法和编译kernel大同小异,可以参考这篇文章: http://www.wiki.xilinx.com/Build+U-Boot

3.5下载源代码

Uboot的源码下载地址是: https://github.com/Xilinx/u-boot-xlnx.git

3.6编译 U-Boot

命令是$make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi- zynq_zed

可以看看u-boot源码文件夹目录下的boards.cfg文件。里面有各种平台的配置表。将编译好的u-boot文件改名为u-boot.elf文件。我们生存boot.bin时要用它

3.7文件系统编译

现在直接用的xilinx和KPA官方提供给我的文件系统“uramdisk.image.gz”。

参考文档: http://www.wiki.xilinx.com/Build+and+Modify+a+Rootfs

从xilinx网上下载arm_ramdisk.image.gz文件。下载地址如下。

http://www.wiki.xilinx.com/file/view/arm_ramdisk.image.gz/419243558/arm_...

这个文件是xilinx提供给我们做模板用的。可以把它解压开,然后在它基础上改改,再打包,就能用的。

3.8设备树编译

设备树的编译方法参考文档, http://www.wiki.xilinx.com/Build+Device+Tree+Blob 。

3.9KPA NIC 模块

直接用的KPA的“kpa_mac.ko文件”。

KPA这部分不用去动,现在也不用改,这部分文件放在我们SD卡的第二分区了即可。然后设备树上加上mac的配置部分即可。

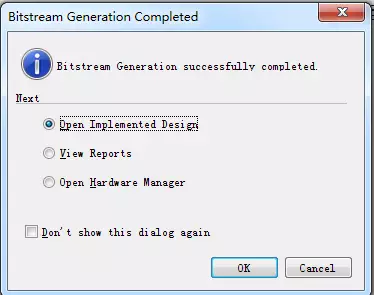

3.10Vivado 生成 bitstream 文件

基于kpa给的Vivado工程“zedboard_redundancy”和两个ipcore,来产生bitstream文件。

图 7:生成bitstream文件

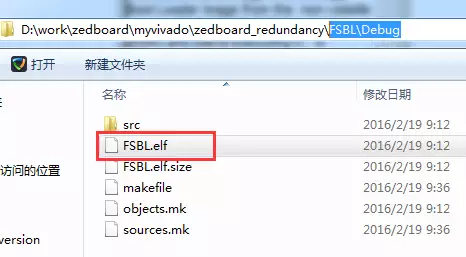

3.11Xilinx SDK 生成 FSBL

图 8:生成的FSBL

3.12制作 BOOT.BIN 文件

利用xilinx SDK,看到,BOOT.BIN文件其实是将U-boot,Vivado生成的Bitstream文件,SDK生成的FSBL文件以及SDK自动生成的的boot.bif四合一打包生成的一个启动文件。BOOT.BIN下一节会放到SD卡中,作用主要是初始化zedboard硬件和加载linux内核。

图 9:生成BOOT.BIN文件

3.13烧录 SD 卡

在ubuntu环境下,将一张4G的SD卡格式化为两分区,第一分区1.1G为FAT格式;第二分区为2.9G为Ext4格式。

图 10:SD卡分区

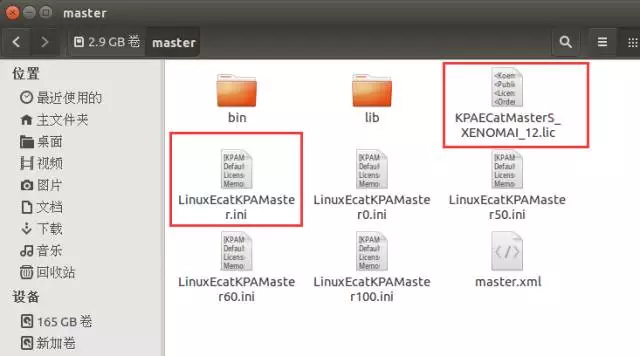

然后将前面准备的BOOT.BIN文件,设备树文件devicetree.dtb,文件系统文件uramdisk.image.gz文件,linux内核镜像uImage这四个文件拷贝到第一分区。不难看出第一分区全部是和操作系统相关的文件。第二分区里则是三个文件,全由KPA提供Master: KPA的EtherCat主站相关的所有文件;

图 11:SD卡中Master内容

Xenomai:xenomai依赖的一些库文件,这个可以官网下载xenomai对应的版本如2.6.3。然后在根目录下make后会生成这个库文件。

Mod:该文件夹下则主要是kpa_mac.ko,也就是KPA提供的那个网卡驱动。

如下图:

图 12:SD卡中Xenomai文件

到此SD卡也做成了。SD卡插到板子上既可以运行了。

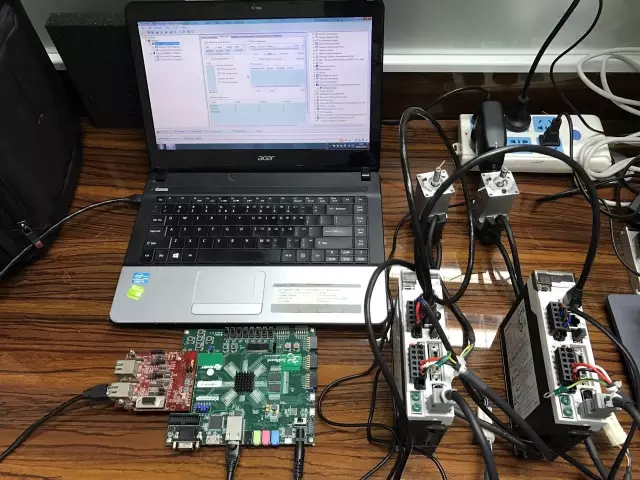

4、EtherCAT 主站程序测试

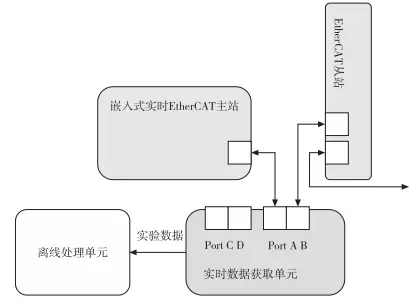

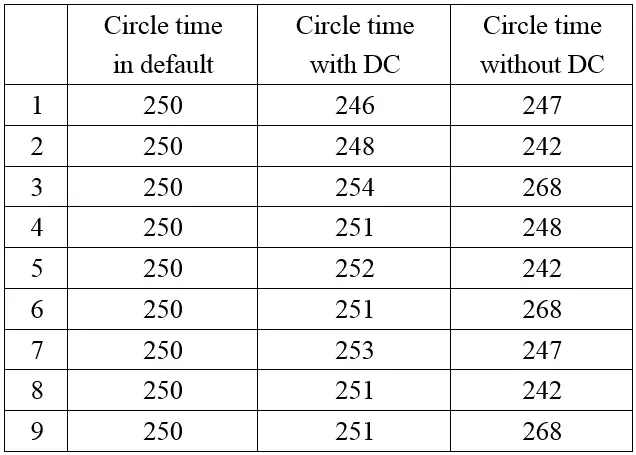

实验平台包括三个组成部分:待测试的EtherCAT系统、实时数据获取单元和离线的实验数据分析单元,如下图所示。主站为构建的嵌入式实时EtherCAT 主站,从站为两套松下交流伺服驱动器MADHT系列。测试的内容为在周期时间为250us下,带DC功能和不带DC功能的测试数据对比。

4.1实时数据获取单元

实时数据获取单元采用的是虹科的网络分析仪Profishark 100M或Profishark 1G,两个网口为标准的100M/1Gbps 以太网接口。支持单独捕获上行和下行数据,并且可以将捕获的数据包供Wireshark /Profishark Manager等软件进行数据分析。此外,它捕获数据包时间戳的分辨率可以达到5ns,保证了实验数据的精确性,如下图:

图 13:实时数据单元示意图

4.2离线数据分析单元

离线数据分析单元是由PC 机运行开源软件Wireshark 实现的,在实验的最后,所有捕获的的实验数据都会交给离线数据单元进行处理和分析。

图 14:EtherCAT网络实验图

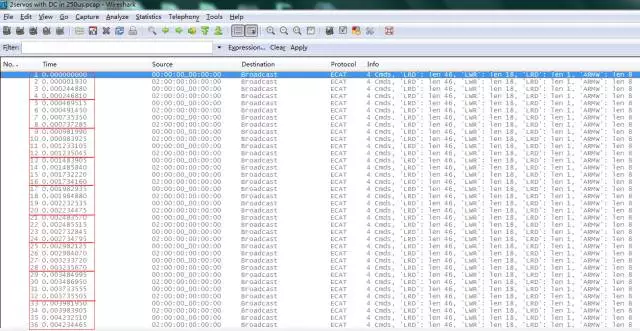

利用wireshark分别抓取数据(带DC)

图 15:基于Wireshark的EtherCAT数据帧(含DC)

利用wireshark分别抓取数据(不带DC):

图 16:基于Wireshark的EtherCAT数据帧(含DC)

表 1:EtherCAT数据测试结果 单位:us(统计至个位)

总结:

可以看出,基于Zynq平台的主站设计方案circle time完全可以做到250us级别,带两轴从站的情况下加DC功能,基本没有抖动存在,但是不带DC的话,周期时间不稳定,抖动也相对较大。

5、EtherCAT 测试程序分析

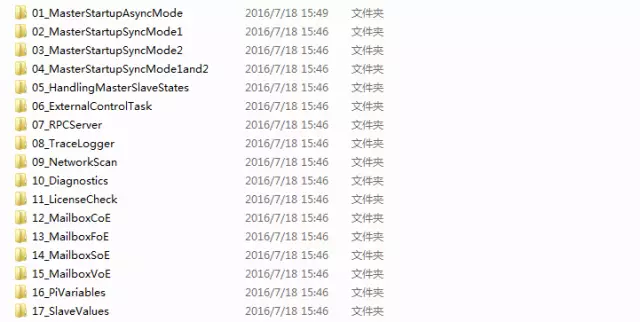

KPA EtherCAT主站协议栈提供了多种功能的程序模板如下,包括ETG协议规定的几种模式,写应用时,可以在这些代码模板上进行编程测试,本文作者基于01异步模式进行测试程序的分析。

图 17:KPA开发包的功能模块(部分)

5.1利用 KPA Studio 扫描网络

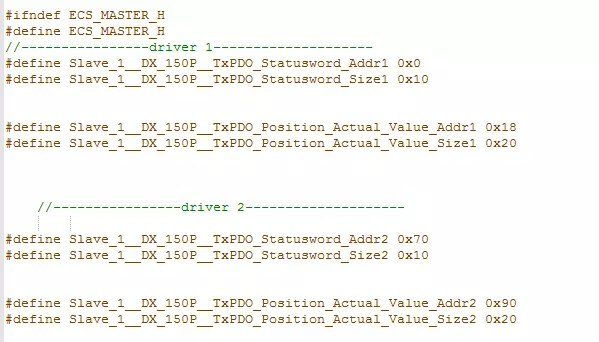

先扫描从站信息,利用KPA Studio导出从从站信息的头文件,定义了从站地址,数据长度。

图 18:KPA Studio扫描从站头文件

5.2Main 函数重要部分介绍

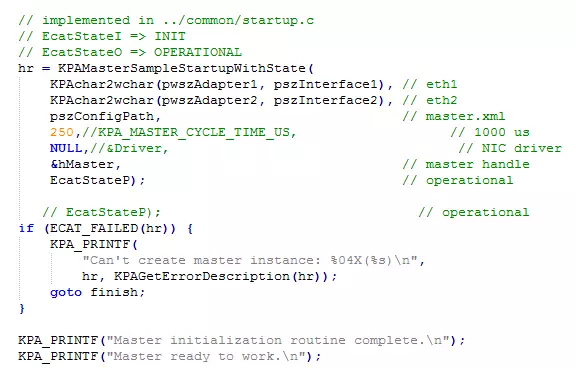

(1)main函数里面,首先主站初始化。包括获取网卡,指定网络配置文件路径,设置周期时间,等操作

图 19:Main函数中的主站初始化部分

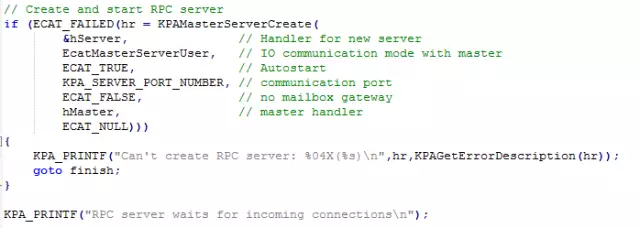

(2)加载PRC服务功能,方便利用KPA Studio进行调试

图 20:加载RPC远程调试功能

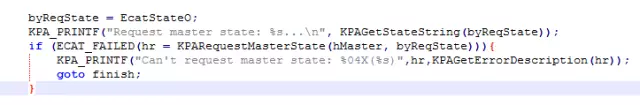

(3)切换主站状态

图 21:切换主站状态

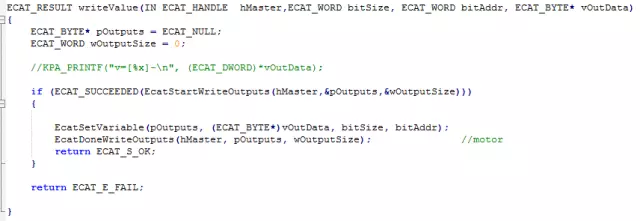

(4)设置控制字,进行PI数据的读写,从而控制从站

图 22:读写PI

其中数据的读取都要遵循先调用EcatStartReadInputs/EcatDoneWriteOutputs 函数,获取输入输出PI,中间再调用EcatSetVariable进行数据的交互,最后再调用EcatDoneWriteOutputs获取数据读写的应答,结束读写。

6、主站开发包申请试用

从KPA官网https://koenig-pa.de/进入,点击“Customer Portal”进入注册页面。注册后可以登录并点击“Quote”,“Request for Quotation”,填写完公司信息后点击“Add Product”,这时会出来很多不同的硬件平台和操作系统列表,选择带MDK Trail字样且价格为0的产品。

注意:注册请用真实的公司名称、地址和联系方式,注册信息也也发一份给本土供应商,中国区内发给广州虹科电子科技有限公司:[email protected]和[email protected]。KPA一般在五个工作日内与本土供应商核对并完成审核,然后注册用户可以免费获取试用的开发包和KPA Studio调试软件(3个月有效期)。

以上是关于如何评估zynq7000的功耗的主要内容,如果未能解决你的问题,请参考以下文章

zynq7000 中断系统及在UCOSIII中的中断处理接口