Zynq Ultrascale+ MPSOC硬件开发之与Zynq7000芯片资源对比说明及开发资料介绍

Posted PIN凡不凡

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Zynq Ultrascale+ MPSOC硬件开发之与Zynq7000芯片资源对比说明及开发资料介绍相关的知识,希望对你有一定的参考价值。

Zynq Ultrascale+ MPSOC硬件开发之与Zynq7000芯片资源对比说明及开发资料介绍

官网关于Zynq Ultrascale+ MPSOC和Zynq7000两种器件对比介绍,Zynq Ultrascale+ MPSOC(后边简称MPSOC)的APU处理器升级为Cortex-A53(ARM v8架构),增加实时处理内核RPU(Cortex-R5F),增加有GPU(Arm Mali™-400 MP2),增加视频的硬解码器,制程提高到16nm,可面向AI/ML、视频处理、辅助驾驶等热门应用。文末有ZCU系列开发板资料的下载方式。

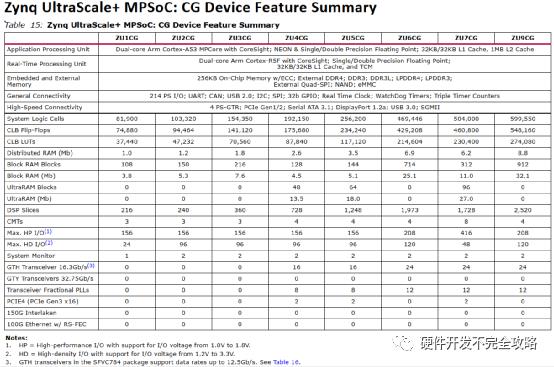

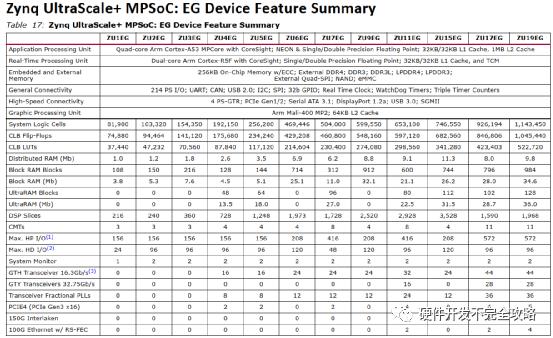

器件主要分为三个系列CG/EG/EV等,主要资源也不一样,如下图所示

MPSOC同时还增加有多种高速外部接口,主要如下:

1)高速Serdes接口(除PS-GTR)PCIe可支持16.0GT/s (Gen4);

2)PS侧增加有GTR高速接口,支持PCIe 5.0GT/s (Gen 2)、USB 3.0 、SGMII ;

3)内置有硬核支持150Gb/s Interlaken 和100Gb/s Ethernet (100G MAC/PCS) ;

4)PS侧增加eMMC控制器;

5)PS侧增加有SATA ,数据速率有1.5Gb/s, 3.0Gb/s, or 6.0Gb/s ;

6)MPSOC内未集成有ADC部分功能电路。

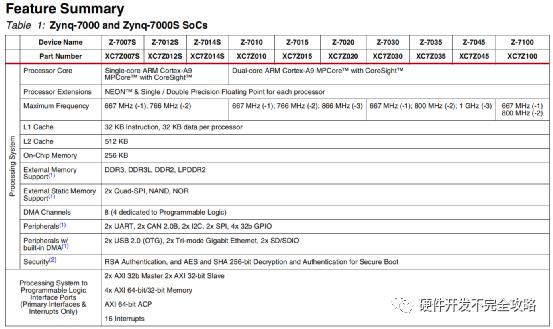

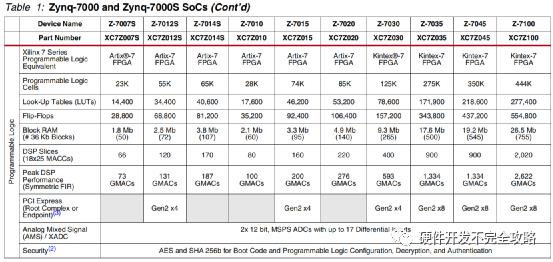

Zynq7000系列特性表如下

MPSOC CG系列特性表如下

MPSOC EG系列特性表如下

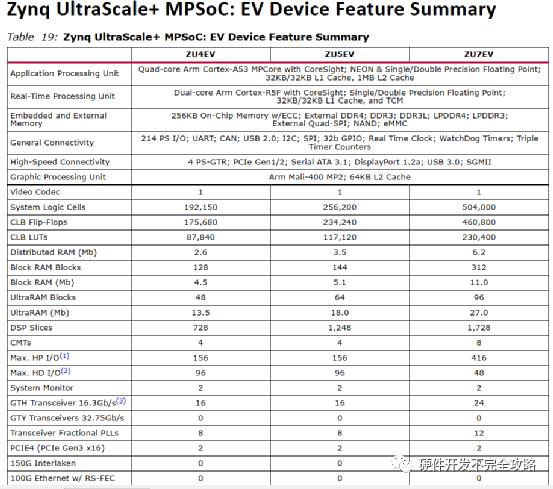

MPSOC EV系列特性表如下

MPSOC官方开发板有三种分别为ZCU104/106/102

在Xinlinx官网可下载到这些开发板的PCB、原理图、BOM单、约束文件(XDC)以及板卡硬件设计指导书等,对于硬件设计有很大的参考价值。后边也会针对板上的一些高速信号的接口设计进行分享,包括核心硬件原理图设计(高速硬件接口),PCB layout设计,SI/PI设计及仿真等,并总结硬件设计中的难点和易错点(坑),欢迎持续关注微信公众号“硬件开发不完全攻略”,后台回复“ZCU开发板”可下载ZCU102和ZCU106开发板资料,资源截图如下(以ZCU106为例)

以上是关于Zynq Ultrascale+ MPSOC硬件开发之与Zynq7000芯片资源对比说明及开发资料介绍的主要内容,如果未能解决你的问题,请参考以下文章

关于Xilinx ZYNQ Ultrascale+ MPSoC使用原生PS端DP接口实现Live模式输出的经验分享

关于Xilinx ZYNQ Ultrascale+ MPSoC使用原生PS端DP接口实现Live模式输出的经验分享

Xilinx Zynq UltraScale+ MPSoC 介绍

Zynq UltraScale+ MPSoC device tree 中 CCF中 clock output数字映射表

Xilinx推出低功耗-小容量-小封装ZYNQ Ultrascale+ MPSoC,特别适合用于ZYNQ-7000升级换代