基于FPGA的百兆以太网RGMII接口设计(读书笔记)

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于FPGA的百兆以太网RGMII接口设计(读书笔记)相关的知识,希望对你有一定的参考价值。

参考技术A 这篇文章的整体架构就是先介绍了百兆以太网的背景,百兆以太网又成为快速以太网。再介绍了用FPGA来实现的优点。接着介绍整体的方法和实验,具体介绍了各个模块的作用,并用视频传输作为测试工具,测试结果。百兆以太网应用场景广,适用于突发通信和继续传送大型数据文件,互换操作性好,具有广泛的软硬件支持。

FPGA是使用逻辑处理专用硬件,无需操作系统,各条处理路径均是并发平行的,因此不同的操作过程不会争夺相同的处理资源,意味着处理速度非常快。FPGA的芯片是Altera的Cyclone IV,PHY芯片是88E1111。

介绍了FPGA芯片EP4CE115F29C7N的功能,并列举了两个方案一是单物理芯片,二是物理层加MAC层继承与同一芯片。本文采用的是第一个方案,采用的芯片是88E1111,并采用的模式是RGMII模式。

系统的整体框架分为上行和下行两个通道,数据通过PHY芯片进入 FPGA,在FPGA中进行数据处理,再送出到PHY芯片传输出去。

preamble_complete模块对前导码进行处理。

4bits_to_8bits将4bits的数据拼接为8bits。

data_processing进行IP和MAC地址替换等操作。

8bits_to_4bits模块将数据拆分成4bits送到PHY芯片输出。

要将88E1111设置为RGMII借口模式,从芯片手册中看到,HWCFG_MODE[3:0]决定了MAC层的接口模式,而HWCFG_MODE[3:0]的值由CONFIG[6:0]来进行映射,因此需要CONFIG4=011,CONFIG5=XX1。并将HWCFG_MODE[3:0]设置为1011,如图所示

说好了配置方法,然后再硬件电路实现

本文的时钟由外部晶振输入的50MHZ作为参考时钟,系统需要的时钟有

1、12.5MHZ以8bit为单位的数据的参考时钟

2、25MHZ以4bit为单位的数据的参考时钟

3、125MHZ时钟来处理数据

4、90°相移之后的25MZH作为参考时钟去产生输出参考时钟CTX_CLK。

这四个时钟都由PLL产生

这是收发时序图。

这个模块主要解决的问题就是前导码的问题,

接收端遇到的问题,首先由于前同步码不是8的整数倍,在拼接成8位时,会产生错位。

如过前导码同步是5_55_55_55_55_55_55,接着是arp的目的地址为FF_FF_FF_FF_FF_FF。那么组成8位就是55_55_55_55_55_55_55_FD,就定位不到5D。

还有一个问题就是在实际观察中,前同步码会有半个周期的0xF。

解决的方法就是使用状态机

分为两个作用,对两组4bits的数据拼接成8bits。

对参考时钟进行转换,从25MHZ转换为12.5MHZ。

拼接部分的RTL图如图

对时钟进行转换只需要通过异步FIFO,以25MHZ写入拼接后的数据,以12.5MHZ读出拼接数据即可。

这模块是核心模块,实现PORT,IP和MAC地址的过滤。使用的时钟是125MHZ,这样的处理速度更快,遇到的问题就是如何将12.5MHZ的时钟转换为125MZH,再将处理完后的时钟转换为12.5MHZ输出数据。

有三个难点:

1、数据长度的不确定性

2、相邻两个数据包间隔不确定性

3、如何保证转换后数据网络的有效性,即使data信号和DV信号的时序关系

这里采用两级FIFO解决,第一个FIFO用来存储数据,同时记录数据长度,将写完后的数据长度写入第二个FIFO,当第二个FIFO非空时,读出数据的长度,这样就做到了data和DV信号的同步。同理需要讲125MHZ转换为12.5MHZ时,再使用上述模块。

需要将8bits拆分为4bits,输出的参考时钟为25MHZ再进行相移。采用DDIO IP核来实现。该IP核如图

如图输入datain_h为1,输入datain_l为0,输出的信号就是参考时钟相移了90°。

小梅哥FPGA进阶学习之旅基于Altera FPGA 的DDR2+千兆以太网电路设计

DDR2电路设计

在高速大数据的应用中,高速大容量缓存是必不可少的硬件。当前在FPGA系统中使用较为广泛的高速大容量存储器有经典速度较低的单数据速率的SDRAM存储器,以及速度较高的双速率DDR、DDR2、DDR3型SDRAM存储器,DDR系列的存储器都需要FPGA芯片有对应的硬件电路结构支持。对于Altera Cyclone IV系列的FPGA,其最高支持到DDR2存储器(不支持DDR3存储器,到了Cyclone V系列的FPGA才支持DDR3存储器)。芯航线AC6102开发板作为一个高速应用型开发板,为了保证系统的存储带宽和容量,电路上设计了一组32位的DDR2存储器,接口时钟速率可达200MHz,等效数据速率为400MHz,整体系统带宽为32bit*400M = 12.8Gb/s。

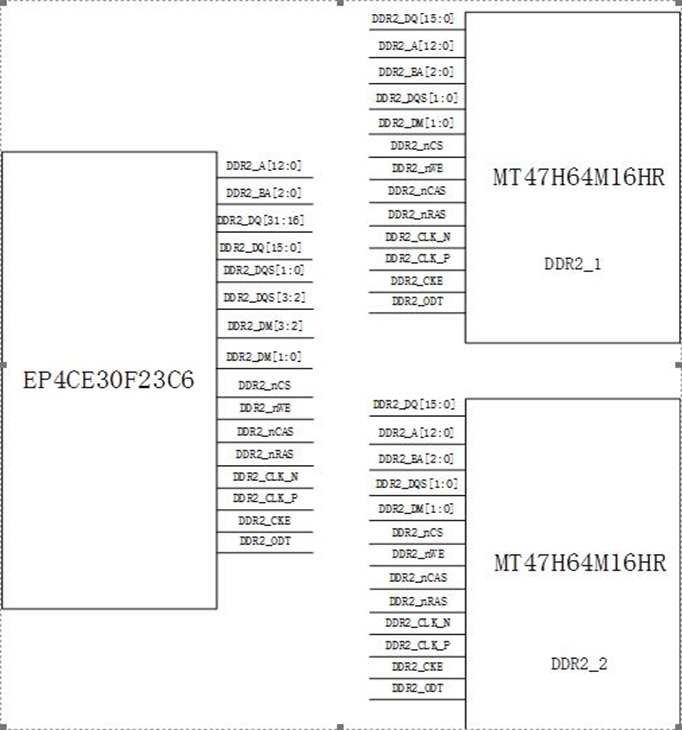

DDR2与FPGA连接方式

每片DDR2存储器的容量为1Gb,两片DDR2芯片组合,得到总容量为2Gb。单DDR2存储器为16bit,两片存储器共用控制线和地址线,数据线并列,即组成了32位的2Gb存储模组。

如下图所示:

- 两片DDR2的CS、WE、CAS、RAS、CLK、CKE、ODT、Addr、BankAddr连接在一起

- DDR2_1的16位数据线DQ[15:0]作为32位DDR2存储电路的低16位数据线连接到FPGA,即DDR2_DQ[15:0]

- DDR2_2的16位数据线DQ[15:0]作为32位DDR2存储电路的高16位数据线连接到FPGA,即DDR2_DQ[31:16]

- DDR2_1的2位DQS和DM分别连接到FPGA上,作为32位DDR2存储电路的DQS[1:0]和DM[1:0]

- DDR2_2的2位DQS和DM分别连接到FPGA上,作为32位DDR2存储电路的DQS[3:2]和DM[3:2]

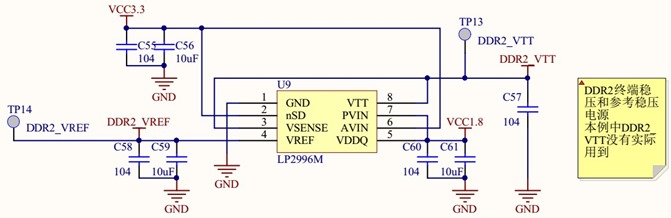

DDR2供电设计

DDR2电路使用1.8V供电,为了保证DDR2能够有充足的能量运行,使用了本板供电芯片TPS650243的一路DCDC输出作为DDR2的1.8V供电,

另外,DDR2的参考电源是否稳定也直接决定了DDR2工作的稳定性,DDR2的参考电源电压为工作电压的一半,即0.9V。在一般低成本的设计方案中,可以使用两个1%精度相同阻值的电阻分压得到该电压。AC6102上为了保证DDR2的工作绝对可靠,选择了使用专用的DDR系列存储器供电芯片LP2996M,该电源能够得到精准且稳定的DDRx芯片工作电压的一半的输出作为DDR2参考源(VREF),且能够提供DDRx系列的终端稳压供电(VTT),VTT是在DDR2需要并联终端电阻的时候,为终端电阻供电提供电源,只有在多于2片DDR2芯片并联使用的时候才考虑需要并联终端电阻,本设计仅使用2片DDR2芯片,因此实际实际不需要用到该芯片的VTT输出。

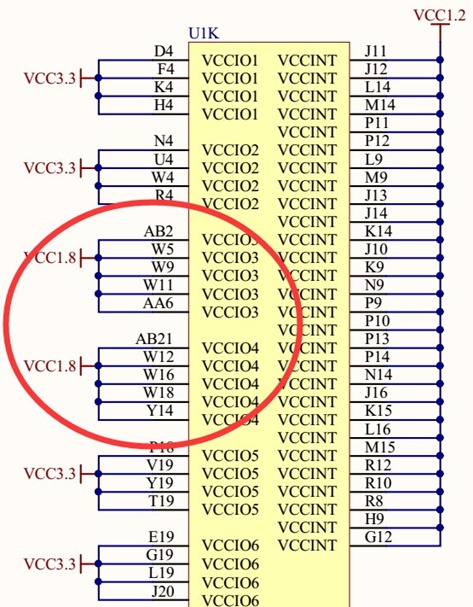

FPGA接DDR2时引脚分配策略

DDR2作为高速大容量存储器,其接口时钟速率高达200M,且为DDR模式,实际接口数据速率为400M。如此高的接口速率下,FPGA的管脚分配也有相当的讲究,根据Altera Cyclone IV系列器件手册的相关说明,当IO口配置在单端模式时,速度等级为C8的器件,上下两个BANK最高能支持167兆的IO速率,而左右两个BANK最高只能支持到133.3M,所以,对于DDR2,需要将引脚分布在BANK3+4或者BANK7+8。当然,如果使用C6的器件,BANK3、4、7、8(即上下bank)的速度可以达到200M、而BANK1、2、5、6(即左右Bank)只能达到166.7M。

即DDR2的引脚分配需要满足以下条件:

- 希望速度高,尽量分配在BANK3+BANK4或者BANK7+BANK8

- 数据总线按照8位或16位分组,对于256脚的这种器件,由于每个BANK的引脚数量有限,因此建议低8位和高8位分别分配在同一个Bank中,同时,对应的DQS和DM也应该和DQ数据分组对应分配在相应的BANK中。对于484脚或者引脚更多的器件,则每16位数据线及对应的DQS和DM分配在同一个BANK中

- DDR2的IO电平为1.8V,所以FPGA上接DDR2的BANK,其IO供电电压应为1.8V

- 上述提到,DDR2的IO电平味儿1.8V,因此FPGA对应Bank的IO供电电压页应该为1.8V,AC6102上,DDR2与FPGA的BANK3和BANK4连接,因此将FPGA芯片的对应IO BANK供电设置为1.8V,如下图所示:

通过本节介绍,我们了解了FPGA 连接DDR2芯片的电路原理和注意事项,大家可以根据自己的需求,结合我们提供的原理图,设计自己的软硬件系统。如有特殊需求,可联系我们以获取帮助。

千兆以太网电路设计

以太网接口作为一种互联型接口,当下应用非常的广泛。从家用宽带,到服务器数据交换,再到工业控制,各个地方都能看到以太网的身影。FPGA系统使用以太网,则主要用于高速远距离的数据传输,如LED大屏显示、监控系统等。以太网数据链路,也由早期的电话线传输,到后来的专用双绞线,发展到光纤,高频无线电,以及现在比较新颖的LIFI。

以太网与FPGA连接

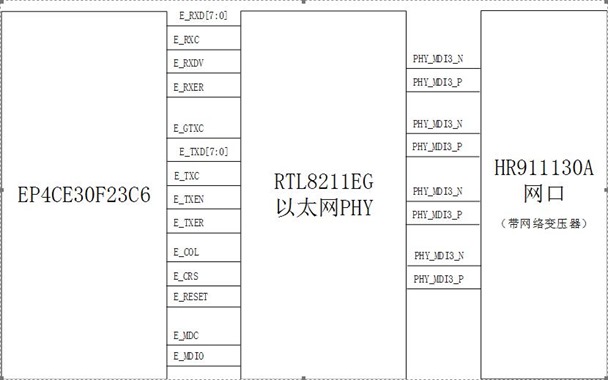

AC6102开发板上,提供了一个千兆以太网接口,该接口由千兆以太网PHY和网络变压器接口组成。当需要发送以太网数据时,FPGA把数据发送给PHY芯片,PHY芯片将数据编码后,通过网络变压器将数据加载到网线上。数据经由网络传递到接收方。远端发送过来的数据,经由网线传递给网络变压器,网络变压器的输出连接到PHY芯片上,PHY芯片对信号进行解码后,得到实际的数据,然后将数据传递给FPGA芯片。FPGA实现千兆以太网数据传输的功能框图如下所示:

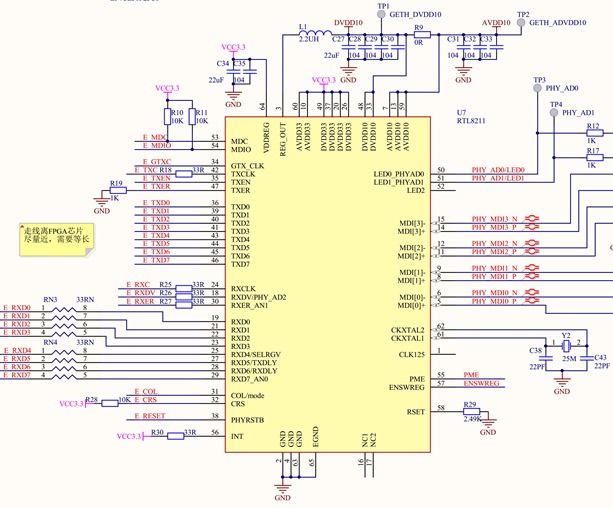

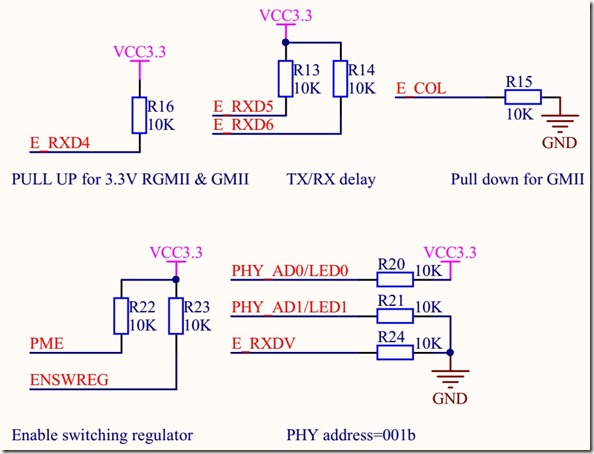

模式配置

RTL8211是一款支持GMII、RGMII、MII接口的以太网物理层收发器,能够工作在100M Base或1000M Base模式。接口可设置为GMII、RGMII、MII接口。并提供了若干引脚用于配置工作模式。

AC6102默认使用GMII接口,实现该配置的方法是将对应的配置引脚E_COL(对,就是这个引脚,芯片在上电时会检测该引脚的状态,并根据该引脚的状态确定工作模式,正常工作时又是正常的COL功能)通过10K的电阻接到GND。

以太网物理层芯片都有一个器件地址,该地址可通过外部引脚设置,上图中,R20、R21、R24通过连接到VCC或者GND,决定了芯片的器件地址为001b。当然,这些状态也仅在芯片上电时刻被读取,当芯片正常工作后,这些引脚就又恢复了普通功能。

与FPGA引脚连接

以上是关于基于FPGA的百兆以太网RGMII接口设计(读书笔记)的主要内容,如果未能解决你的问题,请参考以下文章