FPGA设计千兆以太网MAC——以太网协议及设计规划

Posted moluoqishi

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA设计千兆以太网MAC——以太网协议及设计规划相关的知识,希望对你有一定的参考价值。

上篇该系列博文中通过MDIO接口实现了PHY芯片的状态检测,验证其已处于1000M 全双工工作模式。在设计MAC逻辑之前,要先清楚MAC与PHY之间的接口以及以太网协议细节,这样才能保证网络的兼容性。本文内容多来自Xilinx官方文档pg051 tri-mode-eth-mac.

1.GMII接口

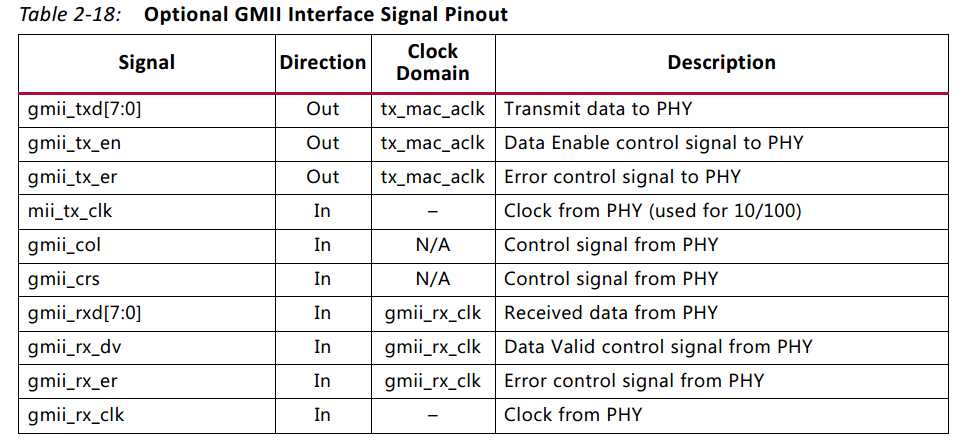

此处使用较简单的GMII接口,接口列表及说明如下:

TX方向时钟tx_mac_aclk由FPGA给出,RX方向时钟gmii_rx_clk由PHY芯片经过内部CDR模块从接收数据中恢复出来,时钟频率均为125MHz。TX和RX方向基本均由三个信号组成:d en/dv er。

2.以太网协议规范

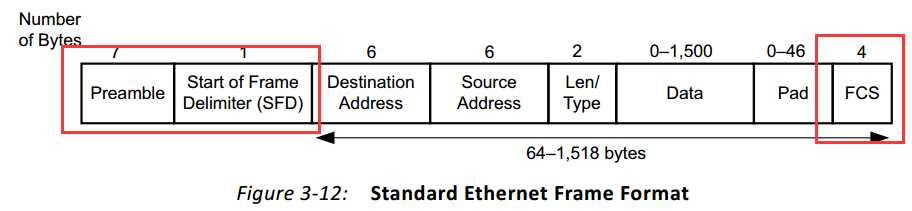

MAC层的功能就是“成帧解帧”,接下来查看以太网数据帧结构和规则。

前导码、帧头符以及FCS在TX方向被MAC添加,在RX方向被剔除。接收端MAC逻辑会将SFD作为接收帧起始时刻。

关于长度/类型字段之前有所提及,Ethernet II帧长度/类型域解释为上层协议类型(字段值大于等于1536,即十六进制的0x0600),而IEEE802.3同样位置是长度字段(字段值小于等于1500,即十六进制的0x05DC)。若为EthernetII帧,接收端MAC不做处理。若为IEEE802.3帧,MAC则检测帧长度是否与该字段匹配,并在必要时去除pad域。

Pad域用来确保前导码和SFD之后的部分长度在64byte以上,也就是保证pad+data≥46byte。当data≥46byte时,不需要pad域。

FCS采用CRC32,多项式为:

![]()

接收端MAC会检测每个帧的FCS值,如果接收FCS错误,则MAC指示给上层用户接收到一个错误帧。

IEEE 802.3-2008规定,以太网帧间隔为96-bit时间以上。对于千兆网来说,t = Tbit*96 = (1/1000*1000*1000)*96s = 96ns。

3.流量控制高级话题

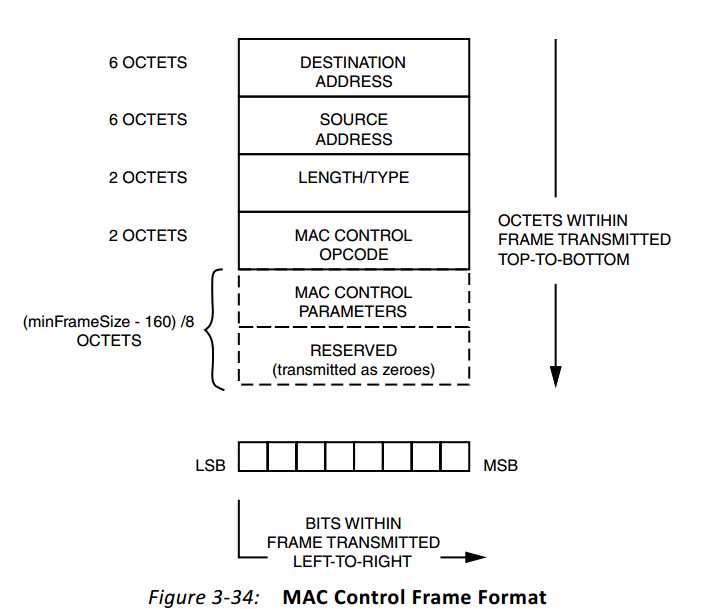

当收发两端的时钟频率出现细微偏差,持续一段时间后会导致频率较慢的一方缓存溢出。此时较慢一方需要告诉另一方暂停一段时间发送数据包以减轻自身缓存压力。“告诉”这一动作通过发送指定控制帧完成。

其中mac control parameters代表对方暂停的时间单位个数,在千兆网中若该数据为1则表示对方需暂停发送数据包512ns。当一方缓存即将溢出,则发送暂停帧。若此时正在发送数据帧,则等待当前帧发送完成。接收方收到pause帧后,依次检测目的地址及类型域,若目的地址为多播地址(01-80-c2-00-00-01)且符合pause帧操作码,则提取控制参数数值并通过拉低发送侧rdy信号来暂停发送。

4.系统设计

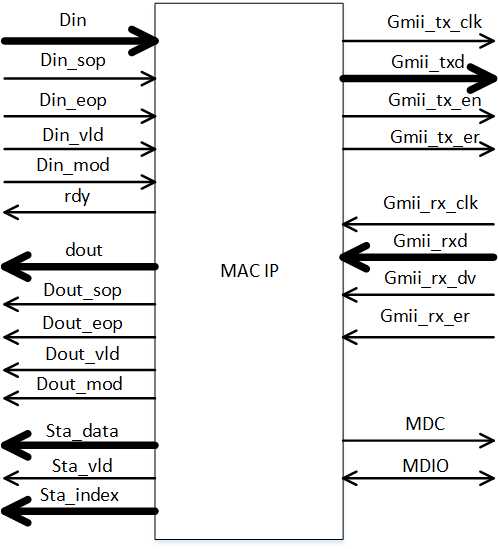

先定义MAC接口:用户侧包括发送数据通道,接收数据通道以及事件统计通道。PHY芯片侧同样有发送通道 接收通道和MDIO管理通道。用户侧数据位宽32bit,PHY芯片侧位宽8bit。

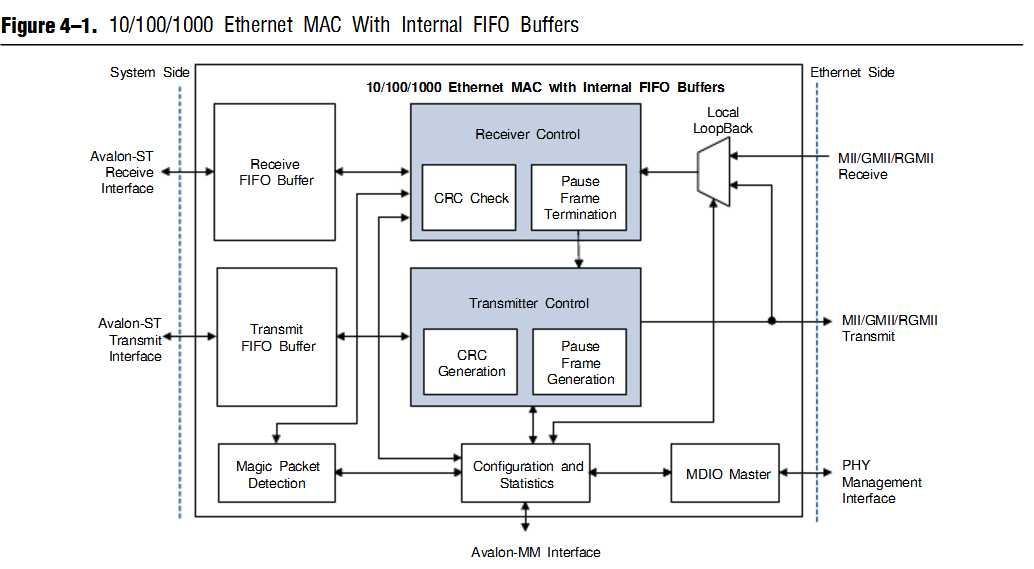

MAC内部设计结构可以参照Altera的以太网MAC IP核,可见内部主要由发送和接收处理逻辑、缓存部分、配置与统计以及MDIO控制模块五部分组成。

模块划分和接口定义完成后,开始写RTL代码。后续以缓存及位宽转换模块为例,依次进行代码编写 自动对比仿真 时序约束与STA 在线调试等步骤。

以上是关于FPGA设计千兆以太网MAC——以太网协议及设计规划的主要内容,如果未能解决你的问题,请参考以下文章