基于龙芯+国产FPGA 的VPX以太网交换板设计

Posted 深圳信迈科技DSP+ARM+FPGA

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于龙芯+国产FPGA 的VPX以太网交换板设计相关的知识,希望对你有一定的参考价值。

调试与测试是本系统设计实现的重要环节。单板调试主要包括各单元电路和接口 的调试,主要通过查看信号波形和运行软件对每个功能进行测试。本章将设计一系列 的调试和测试方案来验证电路设计的正确性。 6.1 电路板静态检查 经过原理图设计、印制板设计、制造、印制板电装等工序,最终形成的电路板如 下图所示。图 6.1 为交换系统母板的 TOP 层,图 6.2 为电源子板和 CPU 子板的 TOP 层,这两块板螺装在交换系统母板的 BOTTOM 层上。

在进行电路板的调试及测试前,需要对电路板进行静态检查,主要是根据印制板 标识,通过万用表分别测量个输出电压对 GND 是否开路状态。

6.2

调试环境

以太网交换板的调试分为单板硬件调试、软件调试及整机联调,需要的调试仪器

和工具如表

6.1

所示:

6.2

调试环境

以太网交换板的调试分为单板硬件调试、软件调试及整机联调,需要的调试仪器

和工具如表

6.1

所示:

单板硬件调试需要使用示波器、万用表、单板电源;软件调试需要国微

FPGA

下

载线缆、龙芯开发主机;整机联调需要信息处理设备机箱、

AC/DC

电压等。示波器

用来测试关键信号(如时钟)的波形,万用表用于检测电路连接故障和电压,单板电

源用于给单板供电。

FPGA

下载线缆用于国产

FPGA

的调试与程序下载等,龙芯开发

主机用于软件程序烧写;信息处理设备机箱用于千兆电口和光口、指示灯、

Serdes

接

口的调试及整机性能测试;

AC/DC

电源用于给整机供电。

单板硬件调试需要使用示波器、万用表、单板电源;软件调试需要国微

FPGA

下

载线缆、龙芯开发主机;整机联调需要信息处理设备机箱、

AC/DC

电压等。示波器

用来测试关键信号(如时钟)的波形,万用表用于检测电路连接故障和电压,单板电

源用于给单板供电。

FPGA

下载线缆用于国产

FPGA

的调试与程序下载等,龙芯开发

主机用于软件程序烧写;信息处理设备机箱用于千兆电口和光口、指示灯、

Serdes

接

口的调试及整机性能测试;

AC/DC

电源用于给整机供电。

6.3

单板调试

6.3.1

电源调试

电源电路调试时单板调试的第一步,如果电源工作异常,将会导致系统无法正常

工作,甚至导致电路板损坏。首先对照明细表,检查芯片外围电路调压电阻是否正确、

电容极性是否反接,然后给印制板加电,测试

IPMC

模块的

3.3V

及

1.5V

是否正常。

根据电源系统的设计方案,其输出使能由

IPMC

模块的

FPGA

来控制,所以待

IPMC

模块的

3.3V

及

1.5V

正常后,通过

FPGA

下载线缆将

FPGA

程序烧写到

IPMC FPGA

中。然后再测量

IPMC FPGA

输出信号中针对电源子板各电源模块的输出使能信号是

否正常,输出使能正常后,再测量电源子板的输出

5V

、

3.3V

、

2.5V

、

1.5V

、

1.2V

、

1.02V

、

1.0V

是否正常。对于低电压

1.02V

、

1.0V

,还需要用示波器测量其纹波,看

是否满足要求。

6.3.2

晶振、复位电路调试

数字电路依赖晶振来工作,所以电路调试前需要用示波器对各晶振输出做初步的

检查,观察波形及频率。电源子板电压正常后,通过

FPGA

下载线缆将

FPGA

程序

烧写到

Main FPGA

中,通过指示灯判断

FPGA 是否运转正常。本设计的复位电路通

FPGA

实现,一般情况下,只要

FPGA

运转正常、

FPGA

逻辑正确,复位输出就没

有问题,所以本设计复位电路调试初步通过

FPGA

运行指示灯来判断,待后续进行芯

片功能调试时,针对其异常情况再反过来查找复位电路是否有问题。

另外,本设计

AD9517

的输出通过

FPGA

配置实现,

FPGA

运转正常后,通过示

波器测量

AD9517

的输出时钟频率和电平是否满足要求。

6.3.3

调试串口和网口的调试

为了单板调试的便利,以太网交换板在空间紧张的情况下仍预留了调试串口和网

口。通过龙芯开发主机将软件程序烧写到

CF

卡中,分别通过串口电缆和网线将调试

串口和网口与计算机互连,观察串口打印是否打印、键入命令是否正常及计算机本地

连接是否正常。

其他电路的调试必须依托软件进行,如

SERDES

接口,需要芯片正常工作后在

整机中进行验证。

6.4

软硬件联调

以太网交换板的千兆以太网光口和电口、指示灯接口、

Serdes

接口均通过背板连

接器引接到前面板上,单板不具备测试条件,必须插到信息处理设备机箱中进行测试。

6.4.1

千兆电以太网口调试

首先通过专用以太网线缆将信息处理设备的千兆以太网电口与计算机网口互连,

计算机网卡“连接速率和双工模式”配置为自动侦测,设备加电后,计算机本地连接

显示为“

1G

”速率。依次更改计算机网卡模式为“

10M

全双工”、“

100M

全双工”,

计算机本地连接均能正常识别,上述操作验证了以太网

PHY

芯片工作正常、机箱接

线正确。接下来通过串口键入端口状态查看命令“

show port mac-link

”,结果如下图

所示,端口

22-24

均为“

UP

”状态,验证了交换芯片与以太网

PHY

芯片之间的互连

正常。

6.4.2

千兆光以太网口调试

将以太网光口

5

和光口

6

通过光纤互连,在串口键入端口状态查看命令“

show port

mac-link

”,结果对应的端口

13

和

14

状态为“

down

”,经查发现光模块的发送使能无

效,通过

FPGA

内部逻辑使能该管脚后,重复查看端口状态操作,端口

13

和

14

均为

“

up

”,结果如图

6.5

所示,验证了交换芯片与光模块之间的互联正常。用同样的方

法验证光口

7

和光口

8

。

6.4.3

Serdes

接口调试

以太网交换板的

Serdes

接口通过背板连接器与其他业务板互连互通,在信息处

理设备机箱业务槽(如

10

槽)中插入一块业务板,板卡正常启动后,在串口键入端

口状态查看命令“

show port mac-link

”,查看该

Serdes

接口对应的端口的状态为“

up

”。

6.4.4

指示灯接口测试

在进行光以太网接口和电以太网接口测试的过程中,观察机箱面板上对应的端口

的指示灯,如果由灭变亮,则验证了指示灯接口正常。

6.5

整机测试

6.5.1

千兆电以太网功能测试

根据技术要求,以太网交换板支持千兆电以太网接口。

测试仪器:支持千兆以太网的计算机

2

台,信息处理设备

1

台;

测试方法和步骤:

6.3

单板调试

6.3.1

电源调试

电源电路调试时单板调试的第一步,如果电源工作异常,将会导致系统无法正常

工作,甚至导致电路板损坏。首先对照明细表,检查芯片外围电路调压电阻是否正确、

电容极性是否反接,然后给印制板加电,测试

IPMC

模块的

3.3V

及

1.5V

是否正常。

根据电源系统的设计方案,其输出使能由

IPMC

模块的

FPGA

来控制,所以待

IPMC

模块的

3.3V

及

1.5V

正常后,通过

FPGA

下载线缆将

FPGA

程序烧写到

IPMC FPGA

中。然后再测量

IPMC FPGA

输出信号中针对电源子板各电源模块的输出使能信号是

否正常,输出使能正常后,再测量电源子板的输出

5V

、

3.3V

、

2.5V

、

1.5V

、

1.2V

、

1.02V

、

1.0V

是否正常。对于低电压

1.02V

、

1.0V

,还需要用示波器测量其纹波,看

是否满足要求。

6.3.2

晶振、复位电路调试

数字电路依赖晶振来工作,所以电路调试前需要用示波器对各晶振输出做初步的

检查,观察波形及频率。电源子板电压正常后,通过

FPGA

下载线缆将

FPGA

程序

烧写到

Main FPGA

中,通过指示灯判断

FPGA 是否运转正常。本设计的复位电路通

FPGA

实现,一般情况下,只要

FPGA

运转正常、

FPGA

逻辑正确,复位输出就没

有问题,所以本设计复位电路调试初步通过

FPGA

运行指示灯来判断,待后续进行芯

片功能调试时,针对其异常情况再反过来查找复位电路是否有问题。

另外,本设计

AD9517

的输出通过

FPGA

配置实现,

FPGA

运转正常后,通过示

波器测量

AD9517

的输出时钟频率和电平是否满足要求。

6.3.3

调试串口和网口的调试

为了单板调试的便利,以太网交换板在空间紧张的情况下仍预留了调试串口和网

口。通过龙芯开发主机将软件程序烧写到

CF

卡中,分别通过串口电缆和网线将调试

串口和网口与计算机互连,观察串口打印是否打印、键入命令是否正常及计算机本地

连接是否正常。

其他电路的调试必须依托软件进行,如

SERDES

接口,需要芯片正常工作后在

整机中进行验证。

6.4

软硬件联调

以太网交换板的千兆以太网光口和电口、指示灯接口、

Serdes

接口均通过背板连

接器引接到前面板上,单板不具备测试条件,必须插到信息处理设备机箱中进行测试。

6.4.1

千兆电以太网口调试

首先通过专用以太网线缆将信息处理设备的千兆以太网电口与计算机网口互连,

计算机网卡“连接速率和双工模式”配置为自动侦测,设备加电后,计算机本地连接

显示为“

1G

”速率。依次更改计算机网卡模式为“

10M

全双工”、“

100M

全双工”,

计算机本地连接均能正常识别,上述操作验证了以太网

PHY

芯片工作正常、机箱接

线正确。接下来通过串口键入端口状态查看命令“

show port mac-link

”,结果如下图

所示,端口

22-24

均为“

UP

”状态,验证了交换芯片与以太网

PHY

芯片之间的互连

正常。

6.4.2

千兆光以太网口调试

将以太网光口

5

和光口

6

通过光纤互连,在串口键入端口状态查看命令“

show port

mac-link

”,结果对应的端口

13

和

14

状态为“

down

”,经查发现光模块的发送使能无

效,通过

FPGA

内部逻辑使能该管脚后,重复查看端口状态操作,端口

13

和

14

均为

“

up

”,结果如图

6.5

所示,验证了交换芯片与光模块之间的互联正常。用同样的方

法验证光口

7

和光口

8

。

6.4.3

Serdes

接口调试

以太网交换板的

Serdes

接口通过背板连接器与其他业务板互连互通,在信息处

理设备机箱业务槽(如

10

槽)中插入一块业务板,板卡正常启动后,在串口键入端

口状态查看命令“

show port mac-link

”,查看该

Serdes

接口对应的端口的状态为“

up

”。

6.4.4

指示灯接口测试

在进行光以太网接口和电以太网接口测试的过程中,观察机箱面板上对应的端口

的指示灯,如果由灭变亮,则验证了指示灯接口正常。

6.5

整机测试

6.5.1

千兆电以太网功能测试

根据技术要求,以太网交换板支持千兆电以太网接口。

测试仪器:支持千兆以太网的计算机

2

台,信息处理设备

1

台;

测试方法和步骤:

(

1

) 如上图所示,将信息处理设备的千兆电以太网接口

1

连接

PC1

,千兆电以

太网接口

2

连接

PC2

;

(2) 通过

WEB

管理系统配置以太网口

1

和

2

的

IP

参数,如图

6.7

所示;

6.5.3

业务转发性能测试

以太网交换板的业务转发性能主要考核其以太网接口在

100%

带宽情况下的转发

时延及丢包率。本测试用例选择千兆电以太网口

1

和

2

,利用专用网络测试仪

TestCenter

进行测试和验证。

测试仪器:网络测试仪

TestCenter

,计算机

1

台,信息处理设备

1

台。

(

1

) 如上图所示,将信息处理设备的千兆电以太网接口

1

连接

PC1

,千兆电以

太网接口

2

连接

PC2

;

(2) 通过

WEB

管理系统配置以太网口

1

和

2

的

IP

参数,如图

6.7

所示;

6.5.3

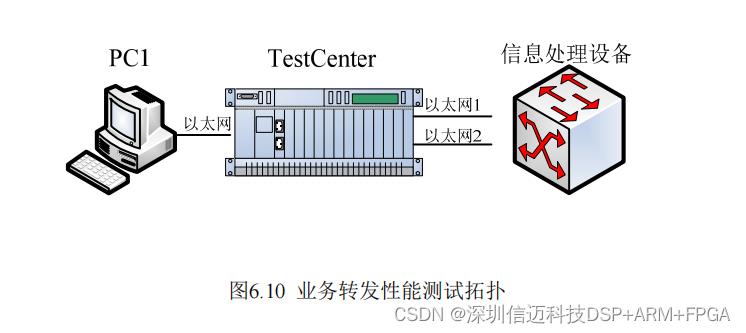

业务转发性能测试

以太网交换板的业务转发性能主要考核其以太网接口在

100%

带宽情况下的转发

时延及丢包率。本测试用例选择千兆电以太网口

1

和

2

,利用专用网络测试仪

TestCenter

进行测试和验证。

测试仪器:网络测试仪

TestCenter

,计算机

1

台,信息处理设备

1

台。

测试方法和步骤:

(

1

) 将信息处理设备的以太网接口

1

连接网络测试仪

port1

;

(2) 将信息处理设备的以太网接口

2

连接网络测试仪

port2

;

(3) 通过

WEB

管理系统设置信息处理设备以太网

1

和

2

的

IP

接口参数,如下

图所示。

测试方法和步骤:

(

1

) 将信息处理设备的以太网接口

1

连接网络测试仪

port1

;

(2) 将信息处理设备的以太网接口

2

连接网络测试仪

port2

;

(3) 通过

WEB

管理系统设置信息处理设备以太网

1

和

2

的

IP

接口参数,如下

图所示。

6.6 测试分析 在对以太网交换板进行测试的过程中,出现了两个比较难查的问题。下面对这两 个问题进行深入分析,并给出具体的解决方法。 6.6.1 以太网接口异常分析 在进行千兆电以太网接口测试的过程中,发现有时候两台计算机终端无法互相 ping 通,并且通断的概率是随机的,无固定规律,在排除了终端本身和测试线缆的问 题后,仔细查阅芯片手册,并对以太网板进行了大量的试验,最终定位该问题与交换 芯片与 PHY 芯片之间的配合相关。具体原因如下: 以太网交换板上电后, FPGA 对各芯片进行复位操作, CPU 复位完成后,开始对 交换芯片进行初始化,同时通过交换芯片的管理接口对 PHY 芯片进行相关配置,因 交换芯片需要配置的参数较多,导致其进入正常工作状态的时间晚于 PHY 芯片, PHY 芯片在进入正常工作状态后,会通过 SGMII 接口向交换芯片发送数据,导致正在初 始化过程中的交换芯片工作不稳定,概率随机。解决方案如下:在进行 FPGA 复位逻 辑设计时,将龙芯处理器、交换芯片、 PHY 芯片的复位信号关联起来,即首先对交 换芯片进行复位,然后对龙芯处理器进行复位,龙芯处理器初始化交换芯片完成后, 再通过 FPGA 对 PHY 芯片进行复位,然后再执行对 PHY 芯片的初始化,保证 PHY 芯片在进入正常工作状态时交换芯片的 SGMII 总线已准备好。按照上述逻辑对 FPGA 程序和 CPU 程序进行修改后,反复对接口进行测试和验证,未出现问题。 6.6.2 业务线速转发丢包分析 以太网交换板的业务转发性能是信息处理设备最重要的技术指标之一,在初始的 业务转发性能测试中,发现当测试数据带宽 100% 时会出现丢包,丢包率为 10 -6 。当 测试数据带宽下降为 98% 时不丢包,时延为 40us ,经过一系列的试验与分析,最终 定位该问题与交换芯片的接口时钟相关,具体原因如下: 交换芯片发送数据时参考本地时钟,接收数据时参考线路恢复时钟,而晶振本身 存在误差,当线路恢复时钟大于本地时钟时,即会造成接收端缓冲区溢出,从而出现 丢包现象。在业务转发性能测试中,作为测试仪,其本地时钟精度较高,我们默认测 试数据包发送时以标准的 25MHz 为参考,交换芯片从线路上将时钟恢复出来并以该 时钟为参考将数据存入接收缓冲区,经过三层交换,交换芯片又以本地时钟为参考将 数据发送到对应的端口。本设计交换芯片的时钟均源于时钟编程芯片 AD9517 的参考 时钟,该参考时钟由一个标称频率为 25MHz 的晶振产生,用安捷伦公司的计数器测 试发现,其实际频率为 24.999885MHz ,即发送时钟小于接收时钟,所以出现丢包。 经过筛选,将 AD9517 的参考时钟晶振更换为正偏的晶振,重新测试,丢包情况 得到解决,但有引发新的问题:晶振的筛选程序复杂,可操作性及可生产性差,为了 解决这一问题,有效区别于与标称频率为 25MHz 的晶振,我们定制了标称频率为 25.000625MHz 、频偏为± 25ppm 的晶振作为 AD9517 的参考时钟,既满足交换芯片 本身对参考时钟 25MHz 、频偏为± 50ppm 的基本要求,又保证交换芯片的发送时钟 频率总处于正偏范围内,降低发送时钟频率小于接收时钟频率的概率。经计数器测试, 定制的 25.000625MHz 的晶振其实际频率为 25.000460MHz ,重新进行性能测试,未 出现丢包,传输时延满足技术指标。 需要说明的是,虽然通过更换晶振规避了性能测试中的误码问题,但误码的根本 原因在于时钟不同源,要从根本上解决该问题,必须解决时钟同源问题。当信息处理 设备间通过以太网进行组网时,可以统一接收 GPS 传送的时钟信号,在本地锁相后 输出作为交换芯片的输入时钟,即所有交换芯片的输入时钟都以 GPS 时钟为参考, 从而实现时钟同源。以太网交换板在设计时已考虑了这些问题,目前硬件电路支持该 部分功能,需要进一步调试。 本文主要介绍以太网交换板的调试环境,单板调试、软硬件联调及整机测试方法 , 并选取两个典型的难题进行深入剖析,说明了国产芯片的开发难度,同时通过功能测 试和性能测试,基本验证了以太网交换板的设计满足使用要求。

信迈提供龙芯+国产FPGA软硬一体化解决方案。

以上是关于基于龙芯+国产FPGA 的VPX以太网交换板设计的主要内容,如果未能解决你的问题,请参考以下文章

基于2片Xilinx Kintex-7系列FPGA高性能VPX存储板