verilog hdl全加器的小问题(quartus)

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了verilog hdl全加器的小问题(quartus)相关的知识,希望对你有一定的参考价值。

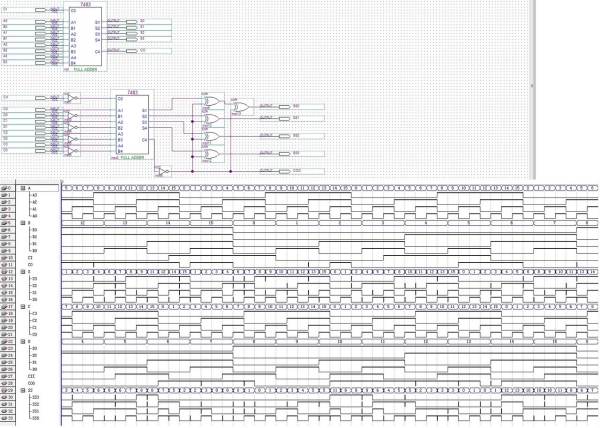

想问一下,我这个全加器仿真波形为什么会是这样,我很纳闷。跪求大神解答,为什么在 a,b都为0的时候,cout还是为1,还有,sum怎么凸起了一小部分,不懂啊

1. 你的这个模块式组合逻辑,你加入clk,变成时序逻辑,编译后在看看吧。

2. 对于现在的代码,看看Tech图,FPGA内部是如何实现你的代码的。

3. 结合你的芯片的速度参数手册,比较每个内部元件输入输出的波形与仿真软件的波形是否一致。

刚刚开始学习的这一阶段很关键,应多思考多做实验。想一想FPGA内部每个部分元件是做什么用的、其与代码有什么关系。多学习学习时序约束,深入实验一下SDRAM的时序约束方法与其现象。

希望能够帮助你。 参考技术A 根据布尔代数列出加法运算的真值表,在卡诺图归并过程中尽力往异或逻辑上凑。结果就是这样,如果看起来不一样,是可以等价转成这样的。

使用74LS83构成4位二进制全加\全减器。 具体要求:1)列出真值表; 2)画出逻辑图; 3)用Verilog HDL仿真

一定要有仿真程序,最好有输出波形,真值表什么的无所谓了。速度啊……

上面全加器A+B,进位输入CI,进位输出CO。下面全减器C-D,借位输入CII,进位输出COO。

求具体verilog程序,我邮箱是462647026@qq.com,程序、图像什么的全部都发下吧

追答已发.v 的是程序,.vwf是波形图

追问是基于门电路写程序,不是直接逻辑加减!我已经写出来了:

module ADD_SUB_4BITS(

A1,A2,A3,A4,

B1,B2,B3,B4,

S1,S2,S3,S4,

C4,

is_sub/*0:add,1:sub*/

);

input A1,A2,A3,A4,B1,B2,B3,B4,is_sub;

output S1,S2,S3,S4,C4; wire B1_2,B2_2,B3_2,B4_2;

IC_74LS83 IC_74LS83_inst1(..........................略,有字数限制

.....................

参考技术A 你老师也是普英哥么?感觉吧。。。他那个图有问题。。。是全加减器哦。。。不是分开的吧。。。。你们老师也是普英哥么?追问不认识

参考技术B 100分 大出血啊 参考技术C 课程设计吧,自己做吧,雷同会扣分的追问呵呵,这都被你发现了

参考技术D 、、光电的?追问物电的……少侠不会也是uestc吧

追答uestc飘过

以上是关于verilog hdl全加器的小问题(quartus)的主要内容,如果未能解决你的问题,请参考以下文章

使用74LS83构成4位二进制全加\全减器。 具体要求:1)列出真值表; 2)画出逻辑图; 3)用Verilog HDL仿真