Verilog HDL 编程

Posted T丶jl

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Verilog HDL 编程相关的知识,希望对你有一定的参考价值。

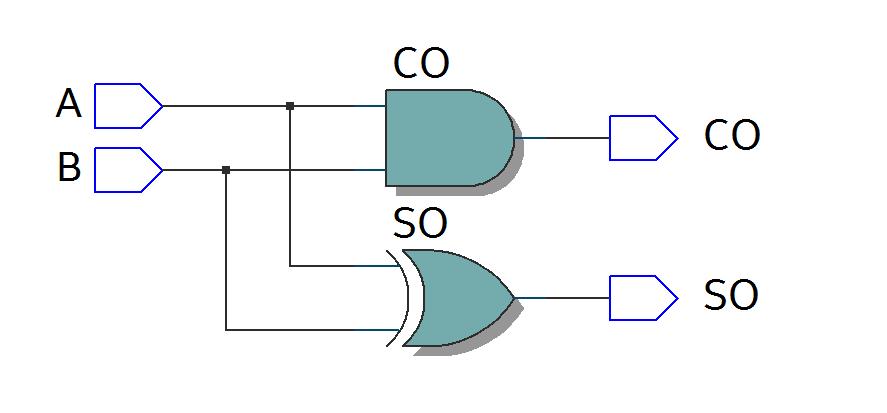

半加器:

P59:

1 module text (A,B,SO,CO); 2 3 input A,B; 4 output SO,CO; 5 assign SO = A ^ B; 6 assign CO = A & B; 7 8 endmodule

RTL电路:

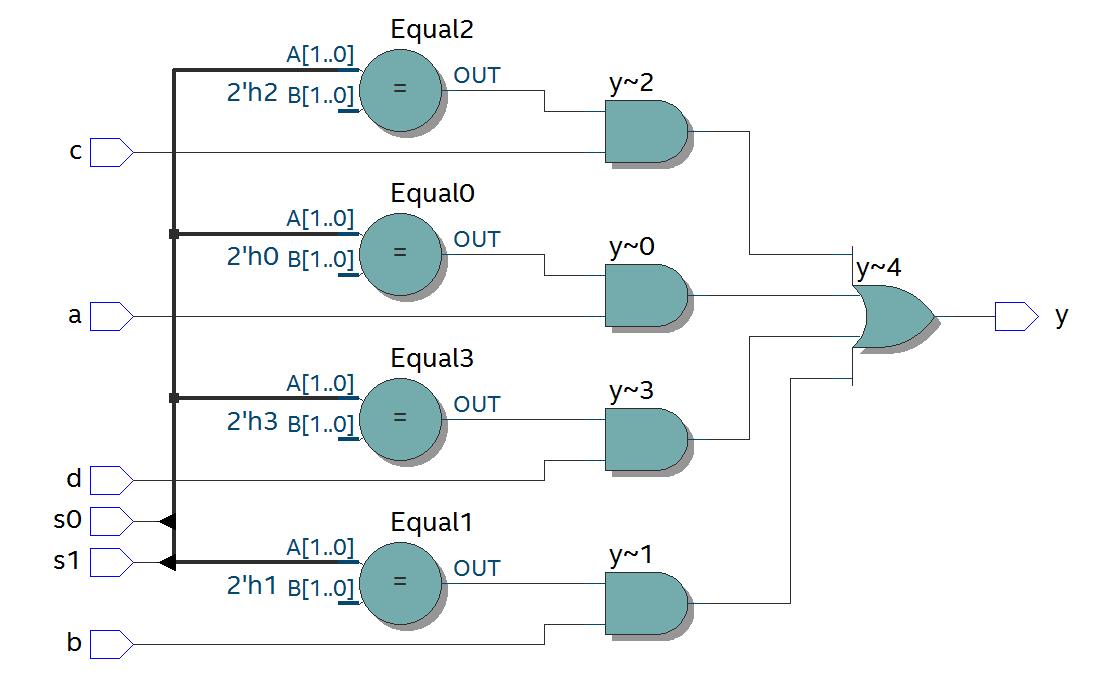

四选一多路选择器

P64:

1 module text (a,b,c,d,s1,s0,y); 2 3 input a,b,c,d,s1,s0; 4 output y; 5 reg y; 6 7 always @ (a,b,c,d,s1,s0,y) 8 begin : MUX41 //语句块开始 9 case({s1,s0}) 10 2\'b00: y<=a; 11 2\'b01: y<=b; 12 2\'b10: y<=c; 13 2\'b11: y<=d; 14 default: y<=a; 15 endcase 16 end 17 18 endmodule

RTL:

P69:

1 module text (a,b,c,d,s1,s0,y); 2 3 input a,b,c,d,s1,s0; 4 output y; 5 // reg y; assign变量类型为wire 6 wire [1:0] SEL; 7 wire AT,BT,CT,DT; 8 9 assign SEL = {s1,s0}; 10 assign AT = (SEL == 2\'d0); 11 assign BT = (SEL == 2\'d1); 12 assign CT = (SEL == 2\'d2); 13 assign DT = (SEL == 2\'d3); 14 15 assign y = (a&AT)|(b&BT)|(c&CT)|(d&DT); 16 17 endmodule

RTL:

以上是关于Verilog HDL 编程的主要内容,如果未能解决你的问题,请参考以下文章