四位全加器的verilog的代码比比皆是,这里上一个比较简单的:

/*

4位全加器全加器需要有输入输出,需要有下级向上进位的输入,

需要有向上一位进位的输出。大家看一下,这个模块已经包含全部的输入输出信息。

大家都知道,N位加法器得出来的出来的和最多是N+1位

因此可以清晰从下面代码中看到相关信息。

然后assign用的是阻塞赋值。相加即满足相关的需求。

*/

module adder4(cout,sum,ina,inb,cin);

output[3:0] sum;

output cout;

input[3:0] ina,inb;

input cin;

assign {cout,sum}=ina+inb+cin;

endmodule

在写testbeach文件之前,先普及一点testbeach的知识:

一般来讲,在数据类型声明时,和被测模块的输入端口相连的信号定义为reg类型,这样便于在initial语句和always语句块中对其进行赋值;和被测模块输出端口相连的信号定义为wire类型,便于进行检测。Testbench模块最重要的的任务就是利用各种合法的语句,产生适当的时序和数据,以完成测试,并达到覆盖率要求。

那么testbeach文件如下:

/*

File Name : test_adder4.v

Description : The testbench of the adder_4.v

Written By : LiMing

Data : 2011/04/18 20:13

modefied : 在仿真的时候,把延时从10ns改为5ns

: cout显示为2位

*/

//test_adder4 (top-level module)

`timescale 1ns/1ns

module test_adder4;

//Declare variables

wire[3:0] sum;

wire cout;

reg[3:0] ina,inb;

reg cin;

//Instantiate the module adder4

adder4 adder4_1(cout,sum,ina,inb,cin);

//Stimulate the inputs, Finish the stimulation at 90 time units

initial

begin

#0 ina = 4\'b0001; inb = 4\'b1010; cin = 1\'b0;

#5 ina = 4\'b0010; inb = 4\'b1010; cin = 1\'b1;

#5 ina = 4\'b0010; inb = 4\'b1110; cin = 1\'b0;

#5 ina = 4\'b0011; inb = 4\'b1100; cin = 1\'b1;

#5 ina = 4\'b0111; inb = 4\'b1001; cin = 1\'b0;

#5 ina = 4\'b0001; inb = 4\'b1100; cin = 1\'b1;

#5 ina = 4\'b0011; inb = 4\'b1100; cin = 1\'b0;

#5 ina = 4\'b0111; inb = 4\'b1111; cin = 1\'b1;

#5 $finish;

end

initial

$monitor("At time %t, ina(%b) + inb(%b) + cin(%b) = sum(%b)(%2d),cout(%b)",$time, ina, inb, cin, sum, sum, cout);

initial

begin

$dumpfile("test.vcd");

$dumpvars(0,test_adder4);

end

endmodule

由于是在windows的cmd下进行命令行的运行,所以有时候每次输入一个命令显得很费时间,所以我这里又写了一个(批处理文件)bat文件:go.bat

ECHO OFF ECHO ********************************* ECHO * Batch file ECHO ********************************* ECHO * ECHO ON iverilog -o test adder4.v test_adder4.v vvp -n test -lxt2 cp test.vcd test.lxt gtkwave test.lxt

(说明一下,我在windows下安装了gnuwin的软件,即能在windows下用gnu的一些小的实用的工具!)哈哈,这里就可以一键运行了,上面的一些命令的解释可以到我的“wndows下如何用Iverilog+GTKWave进行verilog的编译和查看仿真波形”的博文里去看看吧。。这里就不多说了。

G:\\Verilog HDL\\examples\\Verilog135\\01>go.bat G:\\Verilog HDL\\examples\\Verilog135\\01>ECHO OFF ********************************* * Batch file ********************************* * G:\\Verilog HDL\\examples\\Verilog135\\01>iverilog -o test adder4.v test_adder4.v G:\\Verilog HDL\\examples\\Verilog135\\01>vvp -n test -lxt2 LXT2 info: dumpfile test.vcd opened for output. At time 0, ina(0001) + inb(1010) + cin(0) = sum(1011)(11),cout(0) At time 5, ina(0010) + inb(1010) + cin(1) = sum(1101)(13),cout(0) At time 10, ina(0010) + inb(1110) + cin(0) = sum(0000)( 0),cout(1) At time 15, ina(0011) + inb(1100) + cin(1) = sum(0000)( 0),cout(1) At time 20, ina(0111) + inb(1001) + cin(0) = sum(0000)( 0),cout(1) At time 25, ina(0001) + inb(1100) + cin(1) = sum(1110)(14),cout(0) At time 30, ina(0011) + inb(1100) + cin(0) = sum(1111)(15),cout(0) At time 35, ina(0111) + inb(1111) + cin(1) = sum(0111)( 7),cout(1) G:\\Verilog HDL\\examples\\Verilog135\\01>cp test.vcd test.lxt G:\\Verilog HDL\\examples\\Verilog135\\01>gtkwave test.lxt

note:在monitor里面的(%2d)就是输出位宽为2的十进制数。其他同理哦!~~~

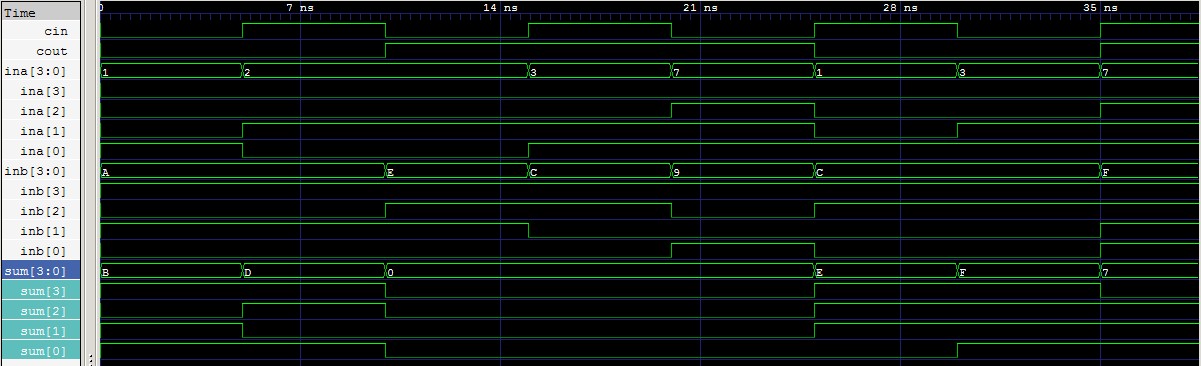

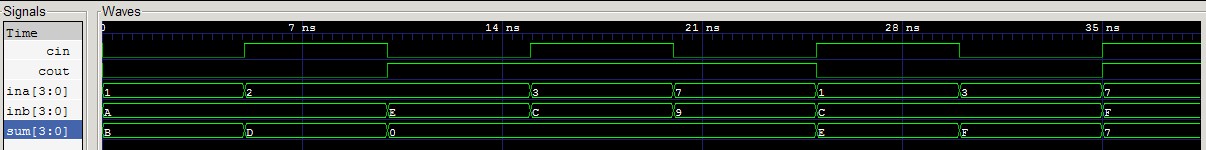

记下来来几张GTKWave的截图:

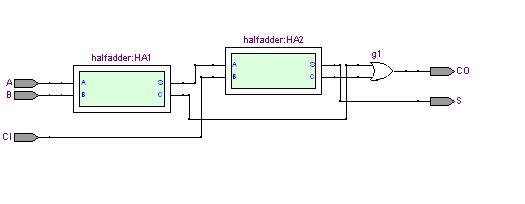

图一:

图二:

我想说就一般的练习,iverilog+GTKWave足以应付,感谢网上的牛人们!!

转载:https://www.cnblogs.com/CodeWorkerLiMing/archive/2012/04/18/2455945.html