DC综合的基本流程

Posted 罪途

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了DC综合的基本流程相关的知识,希望对你有一定的参考价值。

DC综合的基本流程(小白的心路历程)

一. 写在最前面

学了这么久的DC,发现还是没有入门,这次参考一下网上各位大神的文章,自己简单的做个小笔记,就当再系统的学习一遍。讲真的,本人比较菜,内容难免有些错误。这次算是记录一下自己的心路历程叭。愿以后的学习一切顺利,祝自己能找到一个好工作。

二. 什么是逻辑综合

synthesis = translation + logic optimization + gate mapping

- Translation :转换

把描述RTL级的HDL语言,在约束下转换成DC内部通用的门级描述电路(取决于DC自己的库),以GTECH或者没有映射的ddc形式展现,无任何的逻辑重组和优化。 - Logic optimization :逻辑优化

基于所施加的一定时序和面积的约束条件,把通用的门级描述电路进行优化,就是把路径调整一下,门给改一下等等。 - Gate mapping :门级映射

把优化了的通用门级描述电路用别家的工艺库把电路给映射出来,来构成实际电路,得到一个.ddc文件。这个.ddc文件可以包含许多丰富的信息,比如映射的门电路信息与网表、.v格式的网表、延时信息(sdf)、工作约束(sdc)等信息。(.ddc不能用文本编辑器打开)。.ddc包含的网表文件是实际意义的网表文件,而.v包含的网表文件是用来做后仿真的。

三. 启动DC

启动DC的方式大概是有三种:

- GUI:即图形化界面模式。

启动方式:$design_vision - DC Shell:即命令行模式。

启动方式:$dc_shell - Batch mode:即批处理模式(在启动的同时,并告知其需要执行哪些工作脚本)。

启动方式:$dc_shell -topo -f run.tcl | tee -i run.log

命令行和批处理模式是现在设计的主要操作方式。

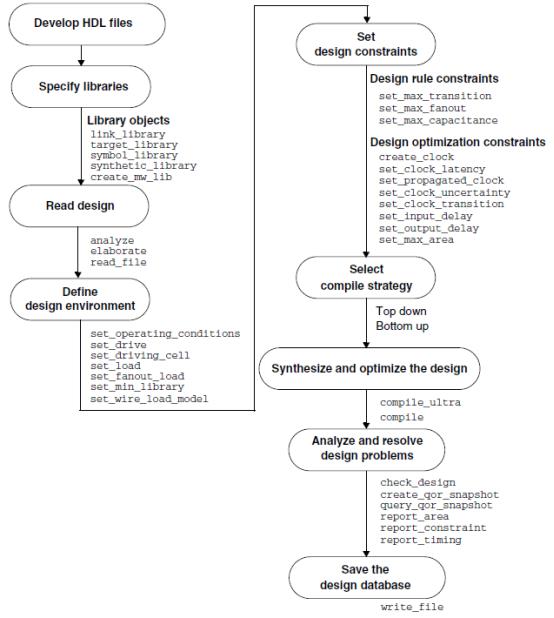

四. DC基本流程概述

a.准备数据

准备设计文件,DC 的设计输入文件一般为 HDL 文件。

b.指定库文件

需要指定的库文件包括:

链接库(link library) 、目标库(target library) 、符号库(symbol library)、综合库(synthetic library)

- Target library: 在逻辑优化与门级映射的时候提供生成网表的cell。

- Link library: 提供设计网表中的 cell,可以跟target_library使用同一个库,但是DC不用 link library中的 cell 来综合设计。当 DC 读入设计时,它自动读入由 link library 变量指定的库;Link时,则先自动搜寻其内存(*)中已经有的库,然后在搜寻Link library指定的库。

- 注:Link library 和Target library统称为technology library,technology library由半导体制造商提供,包含相关 cell 的信息及设计约束标准。

- Symbol library:提供 Design Vision(GUI)中设计实现的图形符号,若使用脚本模式则此库可不指定。

- Synthetic library:即为 Designware library,直译是综合库,但却常称之为IP库。默认的标准Designware由 DC软件商提供,无需指定。

- Create_mw_lib:在DC需要进行物理综合的时候,用以生成物理库。

c.读入设计

设计的读入过程是将设计文件载入内存,并将其转换为 DC 的中间格式,即GTECH 格式,GTECH 格式由“soft macros” 如 adders, comparators 等组成,这些组件来自synopsys的synthetic lib,每种组件具有多种结构。

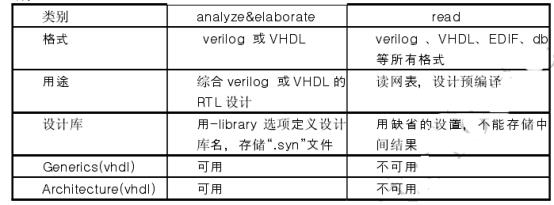

读入设计有两种实现方法实现方法:read 和 analyze & elaborate。

d.定义设计环境

定义对象包括PVT(工艺参数、电压、温度),端口属性(负载、驱动、扇出),wire-load 模型,设计环境将影响设计综合及优化结果。

e.定义约:

约束包括设计规则约束和优化约束。设计规则约束(design rule constraint)由工艺库决定,在设计编译过程中是必须要满足的,以使电路可以正常工作;优化约束则定义了 DC 要达到的时序和面积目标,这是由用户自行定义的。DC在不违反设计规则约束的前提下,将会遵循此约束进行综合设计。

f.选择编译策略:

对于层次化设计,DC 中有两种编译策略供选择,分别为top down和bottom up。在top down策略中,顶层设计和子设计在一起编译,此种策略不适合与大型设计,因为top down 编译策略中,所有设计必须同时驻内存,硬件资源耗费大。在bottom up策略中,子设计单独进行约束,当子设计成功通过后,将被设为dont_touch属性,防止在之后的综合过程中被修改,同等层次的子设计编译完成后,再编译其上层设计,直至顶层设计编译完成,因此Bottom up更适合大规模设计。

g.编译:

用Compile命令执行综合与优化过程,还可以利用一些参数来指导综合和优化过程。

h.分析及解决设计中存在的问题

DC可以生成一些报告以反映其综合结果,如:时序、面积、约束等,这些报告有助于分析和解决设计中存在的问题以改善综合结果。

i.存储设计数据

DC不会自动保存综合后的数据,因而在离开 DC 时需要对这些数据进行手动存储。

j.流程总结

大概的流程为:

准备好文件 —>启动DC —>读入设计前的检查—>读入设计—>约束设计—>综合—>综合后检查与优化—>保存优化后的设计

五. 小结

慢慢悠悠的来到青软已经两个月了,这两个月,学了也不知多少东西,各种方面,浅而杂。终不知自己到最后是到底学了些什么,到现在唯能剩下的也就只有版图叭,也就只有在版图之上留下过痕迹。对于数字后端,却连整个流程都尚未跑完过,属实有些丧。每日早上八点坐在教室,到晚上十一点多回到宿舍,看似如此上的学习时间,但也只有自己知道,到底学没学进去东西,看似努力了,但好似是些无用功叭,也并没有比别人突出多少,无奈。今日,难得凑假期机会写上一篇博客,在参考大神文章后,方将这篇博客补充完整,实际上却毫无自己的东西,无非是生搬硬造罢了。哎,暂且当作是在借此机会学习叭。五一假期结束,回校体测,又是一段时间的浑浑噩噩。

以上部分内容来自下面这位大神的博客:https://www.cnblogs.com/IClearner/

自己在上面进行了小修小补,并加上了自己的想法,以方便自己理解,若内容有误,欢迎指正。

以上是关于DC综合的基本流程的主要内容,如果未能解决你的问题,请参考以下文章