ASIC DC综合的理解

DC综合流程

输入设计文件+指定的工艺库文件+约束文件

经过DC的综合,输出满足期望的门级网表及综合报告

输入输出数据

输入文件:设计文件(verilog等)、工艺库(db)、约束文件

输出文件:网表(Netlist)、report

DC对输入数据的理解

设计对象

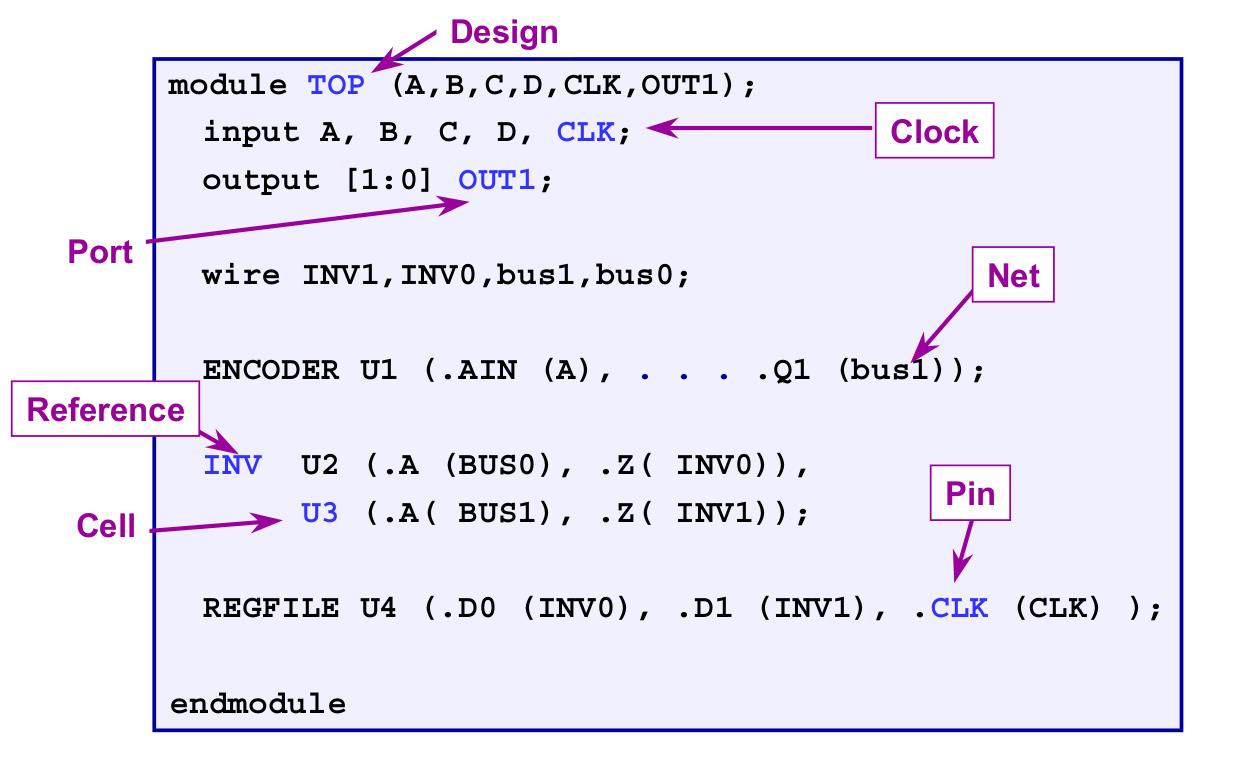

DC将读入的设计进行解析,分成不同的设计对象。

- DC将设计对象分为八种不同的类型:

设计(Design)

单元(Cell)

引用(Reference)

端口(Port)

连线(Net)

时钟(Clock)

库(Library)

工艺库

- 工艺库包括如下信息:

库类

库级属性

单元描述

环境描述比例因子

工作条件

时序范围模型

线载模型

- 可见:DC的综合是根据输入的约束文件,将设计转换到工艺库对应的门级网表

约束与优化

根据实际情况对design工作环境进行建模,包括PVT(工艺/电压/温度),clk,延时,驱动,负载等工作环境

摘录小记

DC综合是基于路径,每个路径上都有Cell和Net,所以基于路径的综合就是计算路径上的delay和rc(dc是使用互连线载模型进行估算)

DC综合是基于路径,每个路径上都有Cell和Net,而Cell延时是根据input_transition和out_load得出的,Net延时根据fanout_length,resistance,capacitance得出的。

DC中的约束,其实就是给Chip设计一个环境,比如驱动这个Chip输入端口Cell,或者这个Chip输出端口驱动了哪些单元或者端口接入了哪些负载,以及这个芯片的工艺、电压、温度等。

参考资料

[1]. Design Compiler manual

[2]. EETOP资料