VIVADO时序分析练习

时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习VIVADO软件时序分析的笔记,小编这里使用的是18.1版本的VIVADO。

这次的练习选择的是ZYNQ的芯片,原本工程是工作在100MHz的时钟,但是作为练习,我们可以把时钟调到一个极限的程度来进行优化。

首先,打开一个工程,更改一下时钟频率,使得工程能够有一些时序问题,我们再通过时序分析的方法对它进行优化。我们这里把原本的100M时钟改成了200M时钟,具体步骤如下:

-

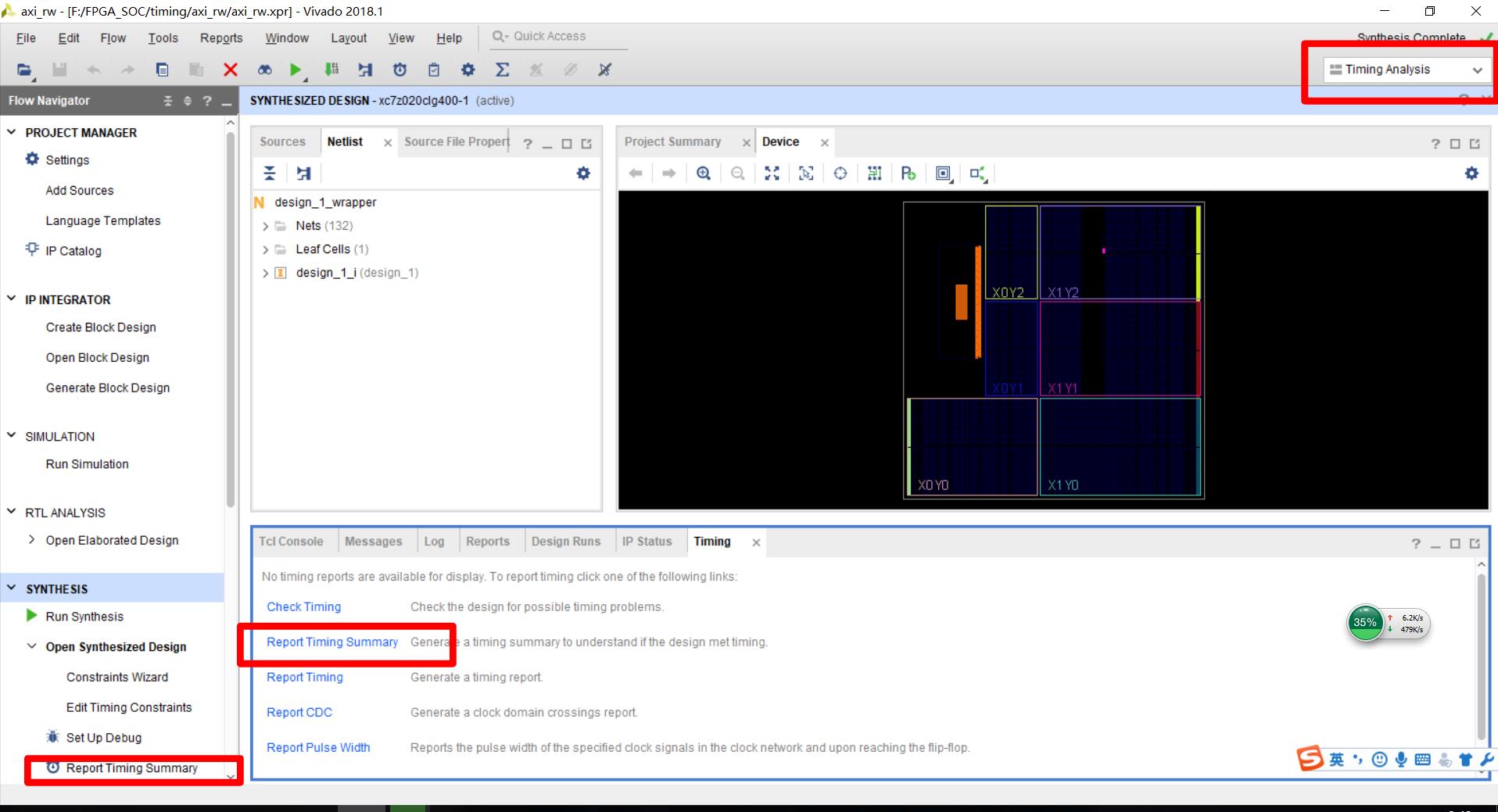

一:更改时钟之后进行综合,并打开timing analysis

-

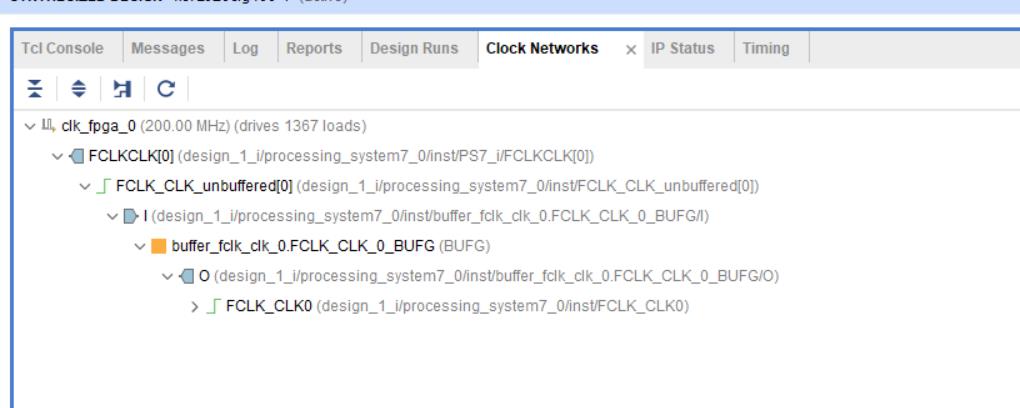

二:通过report clock可以查看全局时钟树的情况

-

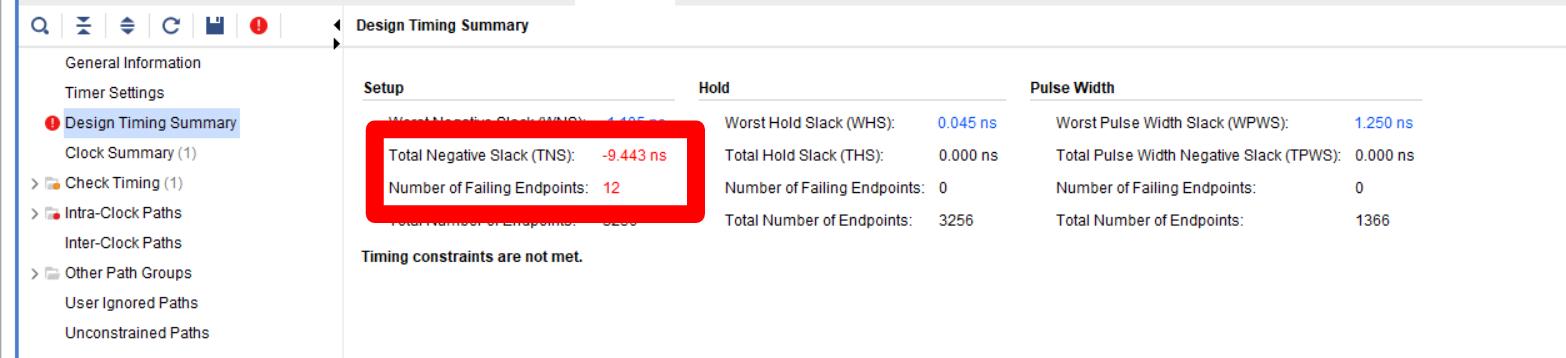

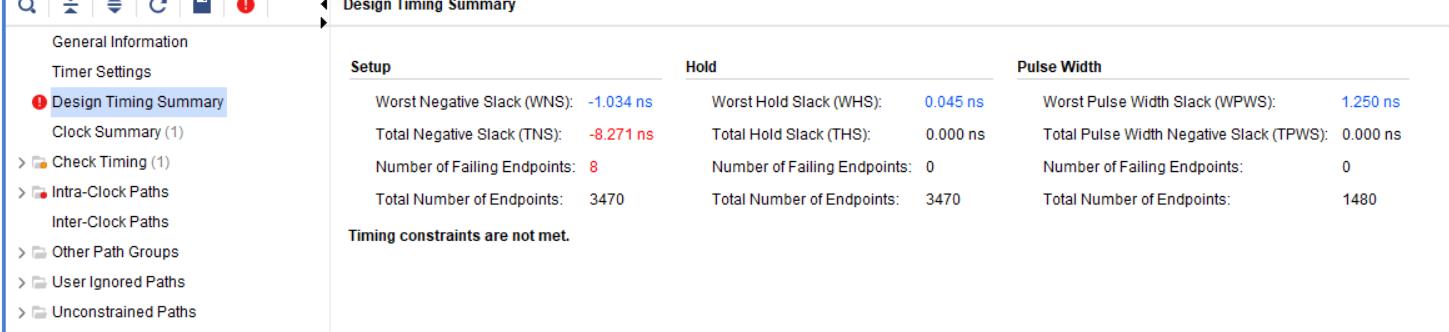

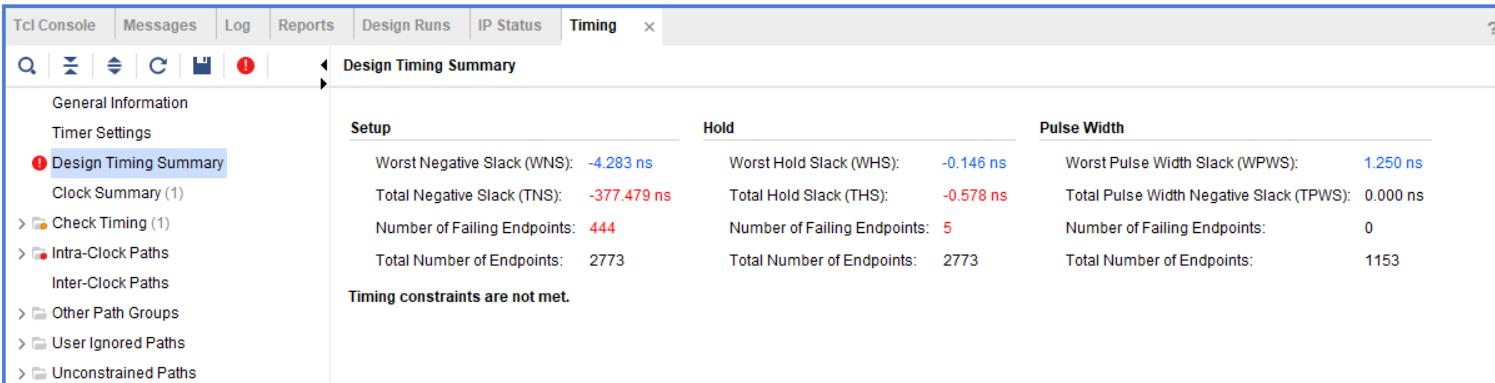

三:通过report timing summary可以看到出现了12个时序问题,总的时序问题达到9个ns多,说明时序问题已经比较糟糕了

-

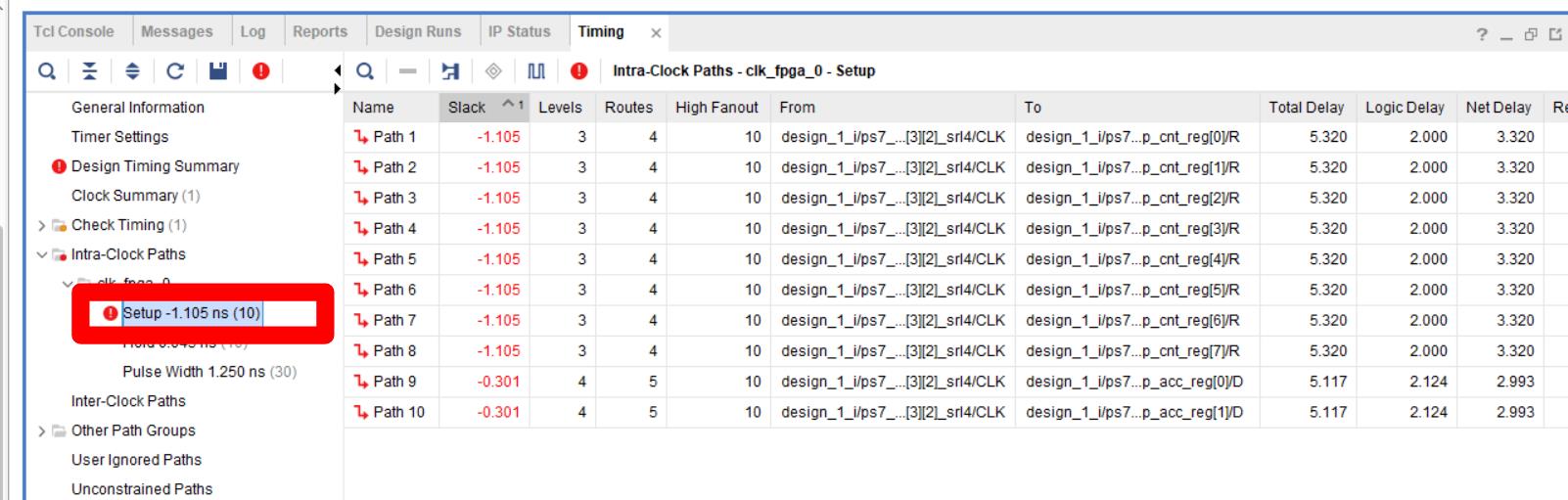

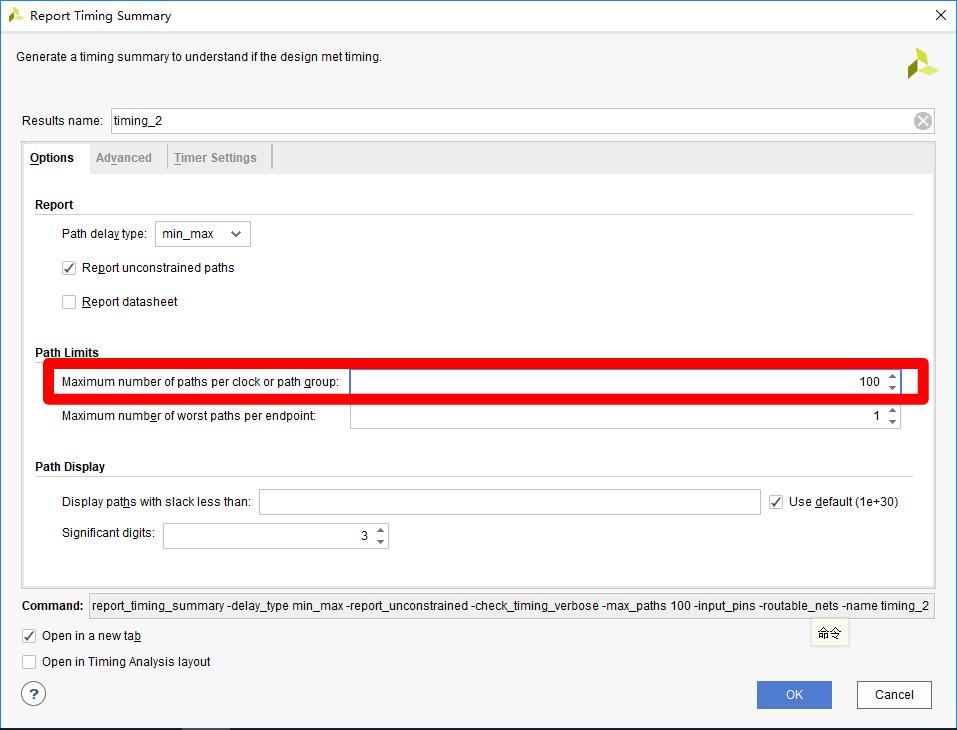

四:在timing窗口里面可以查看相关的时序违例信息,这里只显示了10个,可以在report timing summary中选择要查看的个数,比如选择100个

-

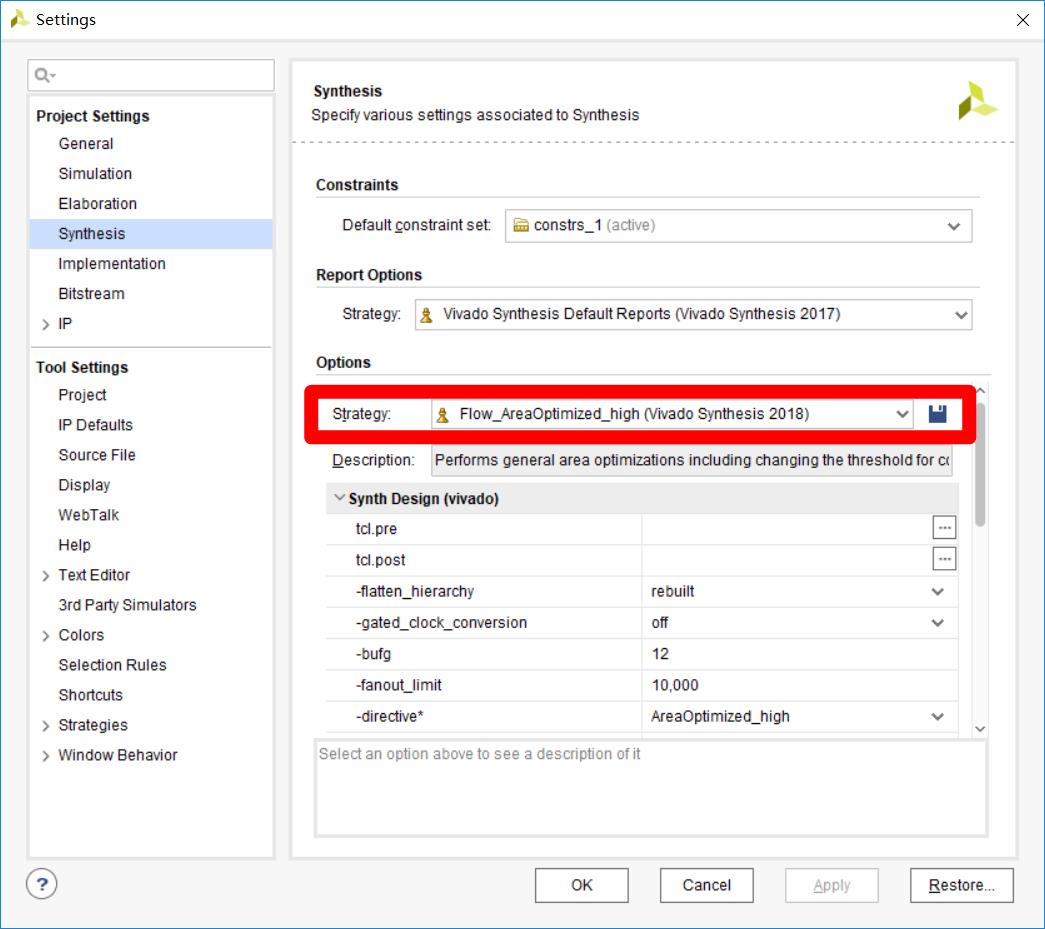

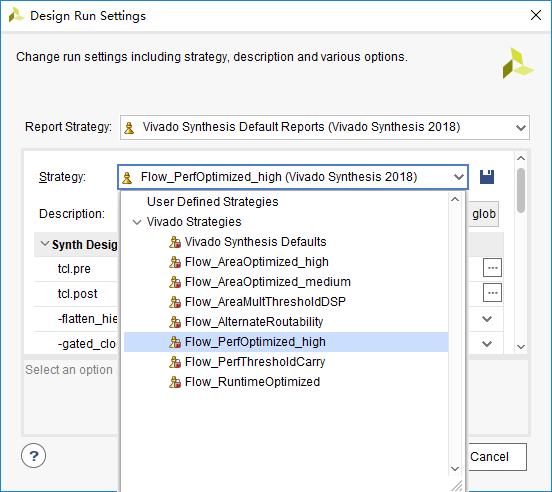

五:我们可以打开setting ->synthesis,更改strategy里面VIVADO提供的优化strategy来进行相关的优化,不同的strategy对应不同的综合模式

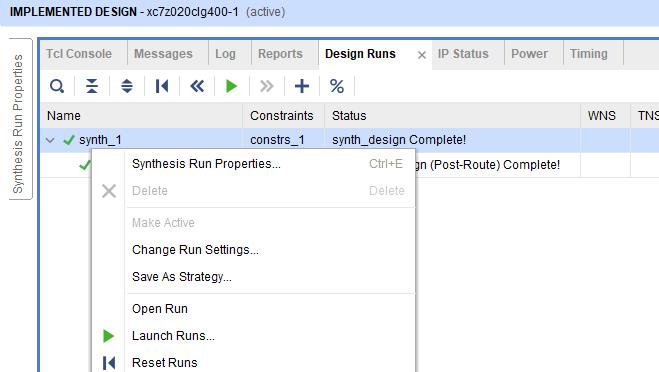

也可以在design runs里面,右键点击相应的sunth->change run settings来修改不同的综合方案

-

六:这里我们选择Flow_PerfOptimized_high来进行综合(也可以一个一个的尝试),综合完成之后,可以看到,违例的现象优化到了8条,总的违例时间减少了1ns。

-

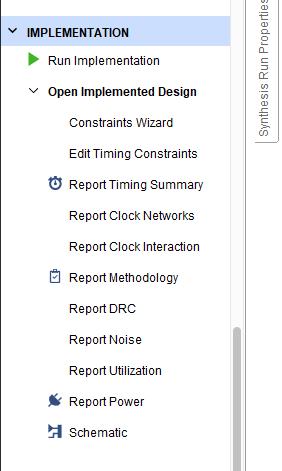

七:小编在尝试各种综合方案之后,发现并不能够优化很好,所以我们开始进行下一步操作——Run Implementation,看看通过Implementation VIVADO能够把时序问题优化到什么程度。

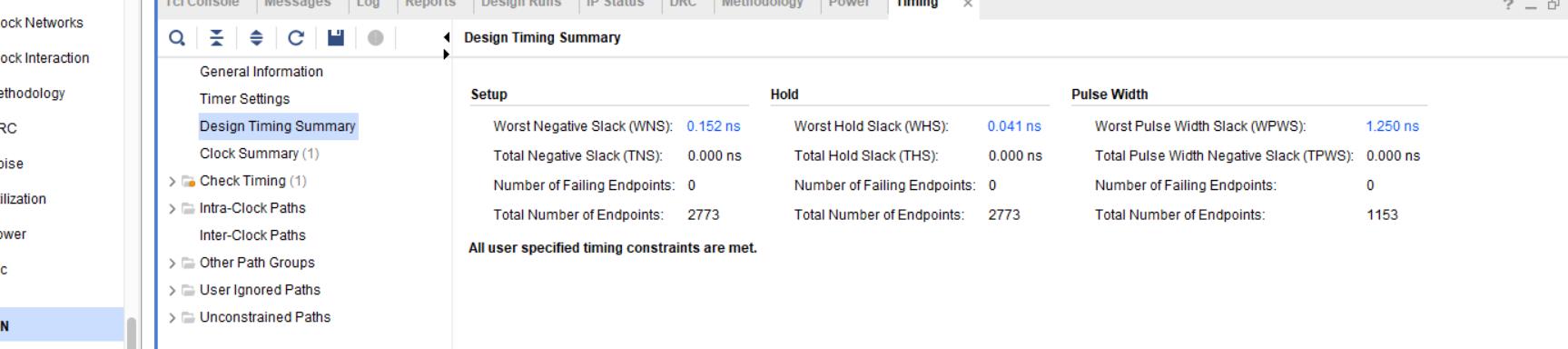

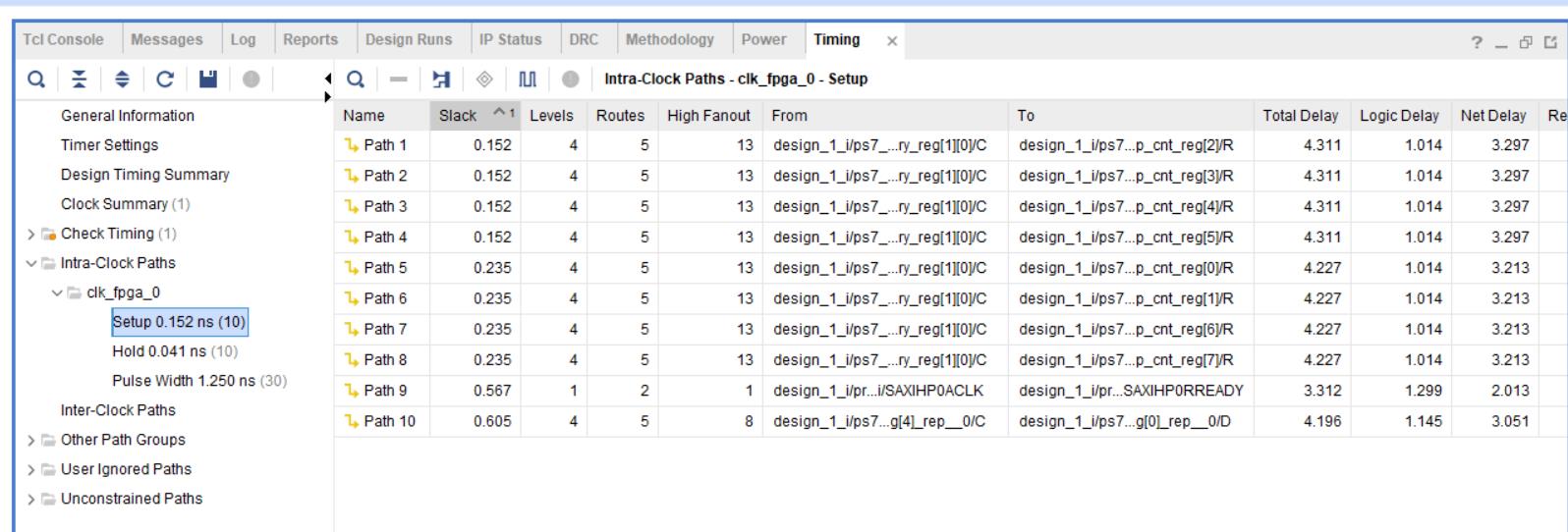

完成布局布线之后,可以看到先前的时序问题通过布局布线已经被优化了,现在没有了时序问题,但是最差的余量只有0.152ns,这个结果并不是很理想。

- 八:通过查看时序路径详情,可以看到时序的余量很不理想

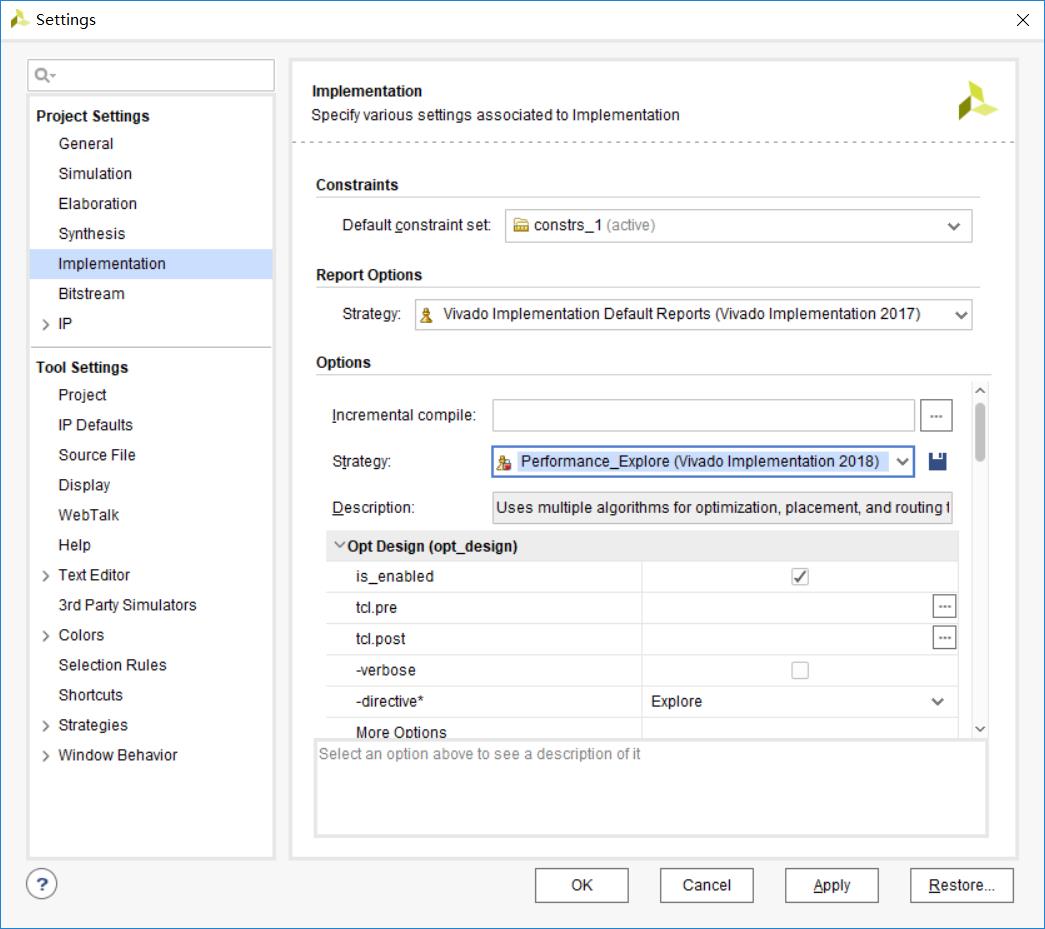

那么我们可以通过修改Implementation的方案来进行优化,在settings里面找到Implementation的strategy,选择不同的方案进行尝试

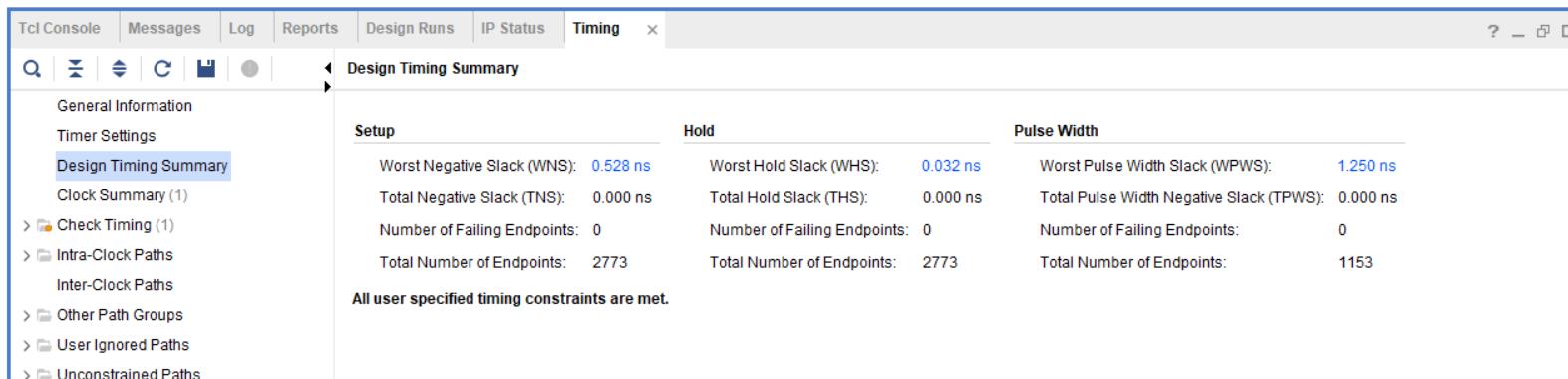

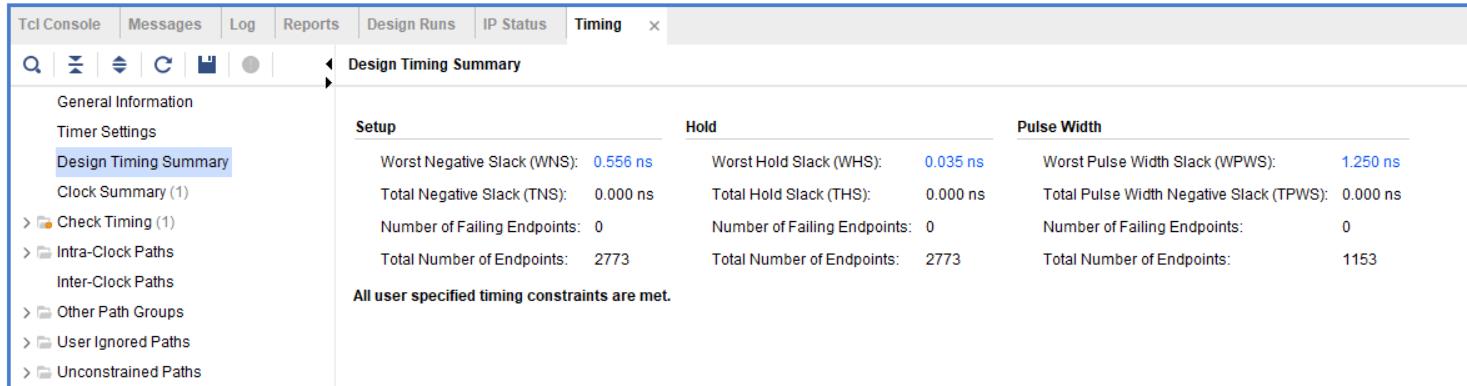

- 九:这里我们选择Performance Explore进行尝试,可以看到通过更改Implementation的strategy,时序被优化了,最差的余量达到了0.556ns,比之前更好了,但是似乎还可以再进行优化,需要不断的尝试,从而找到最优的结果。

-

十:在synthesis的strategy和Implementation的strategy里面可以看到其他的一些选项,都可以尝试,比如在Implementation的strategy里面有一个Flow quick的模式,选择Flow quick模式对比之前的模式可以发现,VIVADO在这个模式下进行布局布线会快很多,但是时序也变的一塌糊涂。小编认为这种模式可以在一些比较大的工程里,比较赶时间的情况下尝试使用。

-

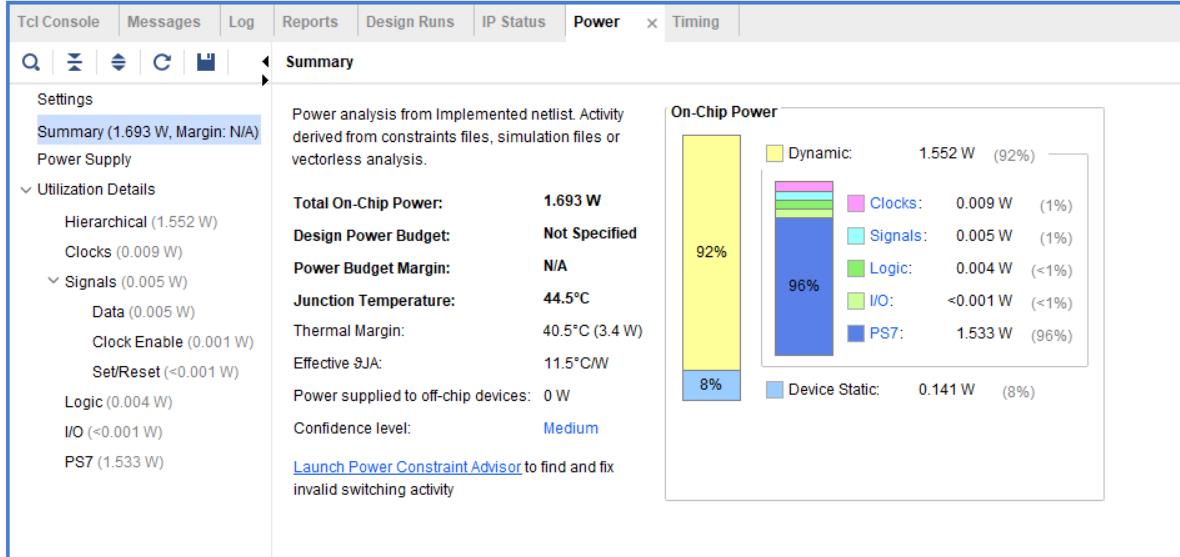

十一:同样的,我们还可以通过report power来查看功耗情况,并通过更改一些策略进行优化,其他的一些功能小编也在探索中。