VIVADO时序约束及STA基础

Posted moluoqishi

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了VIVADO时序约束及STA基础相关的知识,希望对你有一定的参考价值。

一、前言

无论是FPGA应用开发还是数字IC设计,时序约束和静态时序分析(STA)都是十分重要的设计环节。在FPGA设计中,可以在综合后和实现后进行STA来查看设计是否能满足时序上的要求。本文阐述基本的时序约束和STA操作流程。内容主要来源于《Vivado从此开始》这本书,我只是知识的搬运工。

二、时序约束与XDC脚本

时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

1 时序约束首要任务是创建主时钟,主时钟即为时钟引脚进入时钟信号或高速收发器生成时钟。[create_clock]

create_clock -name clk_name -period N -waveform {pos_time neg_time} [get_ports port_name] (划线部分可选)

创建两个异步的主时钟:

create_clock -name clk_a -period 10 [get_ports clk_a]

create_clock -name clk_b -period 15 [get_ports clk_b]

set_clock_groups -asynchronous -group clk_a -group clk_b

当两个主时钟是异步关系,它们生成时钟同样是异步关系:

set_clock_groups -asynchronous -group [get_clocks clk_a -include_generated_clocks]

-group [get_clocks clk_b -include_generated_clocks]

差分时钟仅约束P端口:

create_clock -name clk -period 10 [get_ports clk_p]

高速收发器生成时钟作为主时钟:

create_clock -name gt0_txclk -period 8 [get_pins GT0/.../TXOUTCLK]

有一种特殊情况无需与具体引脚绑定,即创建虚拟时钟。该约束用于设定输入/输出延迟。需要创建虚拟时钟的场景是输入FPGA的数据由FPGA内部产生时钟采样,如串口通信。

create_clock -name clk_v -period 5

2 创建主时钟后,需要约束生成时钟:[create_generated_clock]

生成时钟分为两种。由PLL MMCM等专用时钟单元生成产生的时钟信号,Vivado会自动产生相关约束。还有一种是自定义生成时钟,一般为逻辑分频得到。

时钟源是时钟端口:

create_generated_clock -name clk_div -source [get_ports clk] -divide_by 2 [get_pins rega/Q] 意思是在rega单元的Q引脚上的时钟信号clk_div是由clk经过2分频得到的生成时钟。

时钟源是引脚:

create_generated_clock -name clk_div -source [get_pins rega/C] -divide_by 2 [get_pins rega/Q]

除了使用-divide_by -multiply_by表示主时钟和生成时钟的频率关系,也可以用 -edges实现更精确的表达:

create_generated_clock -name clk_div -source [get_pins rega/C] -edges {1 3 5} [get_pins rega/Q]

相移关系使用-edge_shift命令描述。

该约束命令还常用于重命名时钟信号:

create_generated_clock -name clk_rename [get_pins clk_gen/.../CLKOUT0]

3 创建时钟组:[set_clock_groups]

a. 异步时钟情况:

set_clock_groups -asynchronous -group clk_a -group clk_b clk_a和clk_b是异步时钟。

b. 物理互斥情况:

create_clock -name clk_a -period 10 [get_ports clk]

create_clock -name clk_b -period 8 [get_ports clk] -add

create_clock -name clk_c -period 5 [get_ports clk] -add

set_clock_groups -physically_exclusive -group clk_a -group clk_b -group clk_c

该种情况仅是为了观察clk引脚时钟信号周期依次为10ns 8ns和5ns时,时序是否收敛。因此这三个时钟物理上不同时存在。

c. 逻辑互斥情况:

set_clock_groups -logically_exclusive

-group [get_clocks -of [get_pins clk_core/.../CLKOUT0]] -group [get_clocks -of [get_pins clk_core/.../CLKOUT1]]

clkout0和clkout1送入到BUFGMUX中,后续根据sel信号确定选择哪一个作为工作时钟。此时clkout0和clkout1同时存在电路中,但仅有一个会作为后续电路工作时钟,因此逻辑上互斥。

特殊用法:当asynchronous 的group只有一个,说明改组内时钟是同步的,但与其他所以时钟异步。

4 设置伪路径:[set_false_path]

设置伪路径后,不再对特殊路径进行时序分析。特殊路径如测试逻辑、添加同步电路后的跨时钟域路径等。在两个时钟域之间应该相互设置为set_false:

set_false_path -from [get_clocks clk_a] -to [get_clocks clk_b]

set_false_path -from [get_clocks clk_b] -to [get_clocks clk_a]

5 常用时钟相关命令:

report_clocks:查看创建的所有时钟

report_property [get_clocks <clk_name>]:查看时钟clk_name的属性

report_clock_network:查看时钟的生成关系网络

report_clock_interaction:查看时钟交互关系

其中最后一项非常重要,经常被用于查看异步时钟域之间的路径是否安全。若存在不安全路径,需要添加同步、握手或FIFO后,设置为异步时钟组或false_path。

键入该命令后,会生成时钟交互矩阵。对角线是每个时钟内部路径,其他非黑色部分即为存在对应两个时钟的跨时钟域路径。红色部分是非安全路径,若不处理会产生亚稳态。

三、查看时序报告(STA)

本节以一个有很多时序问题的工程为例进行讲解。在综合后即可打开时序概要查看时序报告。

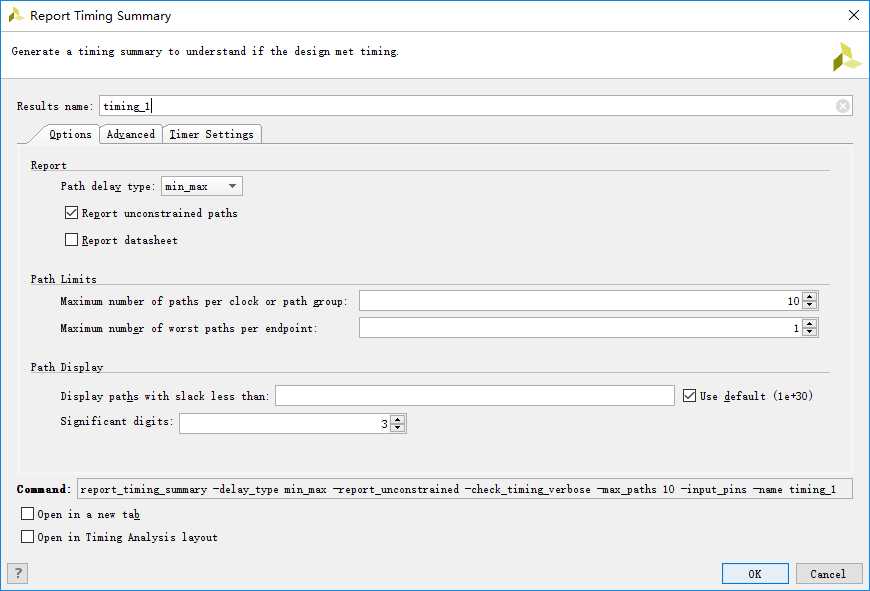

打开后有如下界面:

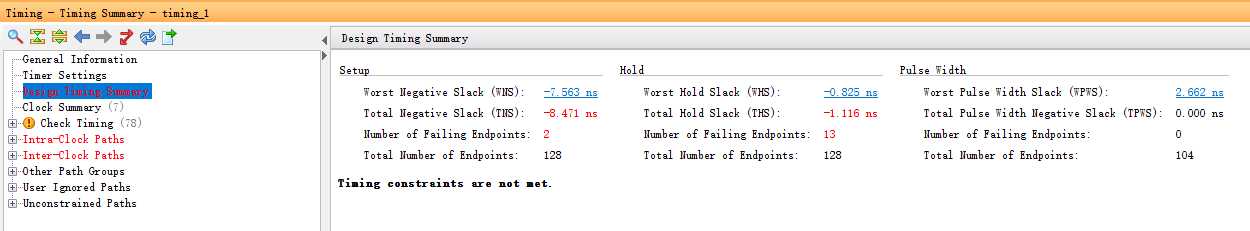

其中Design Timing Summary是时序概况,包括最大延迟分析、最小延迟分析以及脉冲宽度三个部分。其中WNS或WHS为负数,说明当前设计无法满足建立时间或保持时间要求,也就是说数据无法被稳定采样。

Clock Summary内的信息与使用report_clocks TCL脚本调出来的信息相似,包含了全部已创建的时钟信号。Check Timing部分则包含了未被约束的部分,我们可以根据该部分信息进一步添加必要的约束。Intra-Clock Paths和Inter-Clock Paths则分别描述了同步和异步电路时序路径的裕量参数。

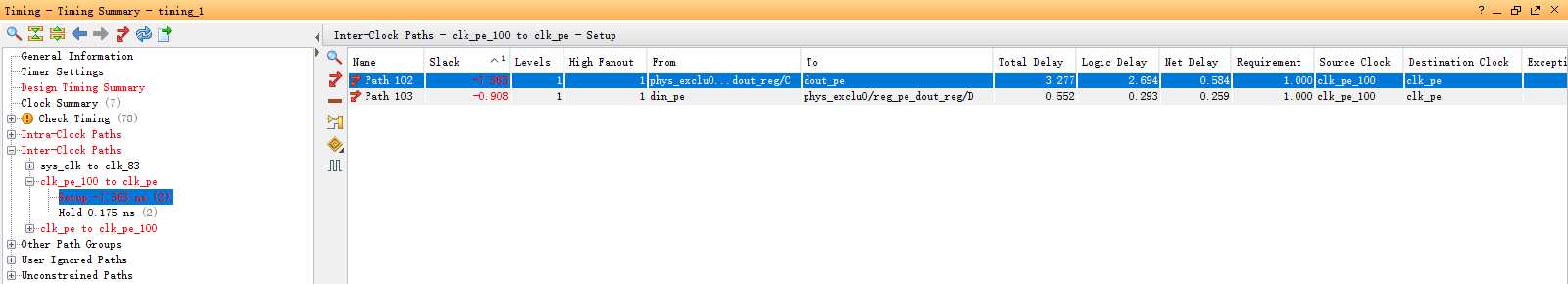

点击WNS或WHS后的数值可以直接找到时序裕量最差的路径:

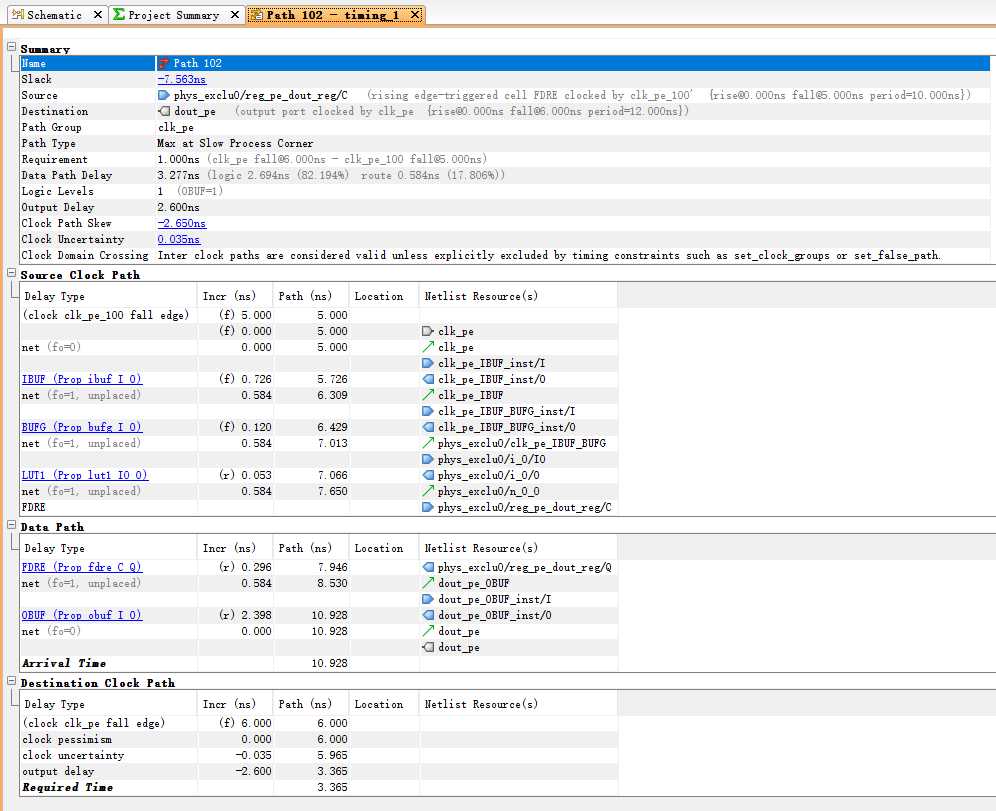

双击路径信息所在行任意位置,界面会跳转到该路径的详细信息界面:

四类时序路径中,除了FPGA输入端口到输出端口这一特殊情况外,其他时序路径均由源时钟路径、数据路径和目的时钟路径三部分构成。上表中各项的具体解释见官方文档UG908.

本文说明了时序约束和STA的关系,基本时序约束情形及相应的XDC脚本。之后简单介绍了如何在VIVADO中查看时序报告来分析时序问题。后续会以网络通信中常见的RGMII接口设计实例阐述I/O延迟约束部分。

以上是关于VIVADO时序约束及STA基础的主要内容,如果未能解决你的问题,请参考以下文章