RTL基本知识:全加器设计(VHDL)

Posted 魏老师说IC

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了RTL基本知识:全加器设计(VHDL)相关的知识,希望对你有一定的参考价值。

【设计要求】

使用层次化设计方法,用VHDL语言设计四位二进制全加器,并进行仿真。

【设计目的】

考查对于VHDL元件例化语法的熟悉程度;

考查对于数字电路中全加器工作原理的理解;

【设计思路】

用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。

第一步:一位全加器;

第二步:多位全加器,在其中例化一位全加器实现;

1 一位全加器

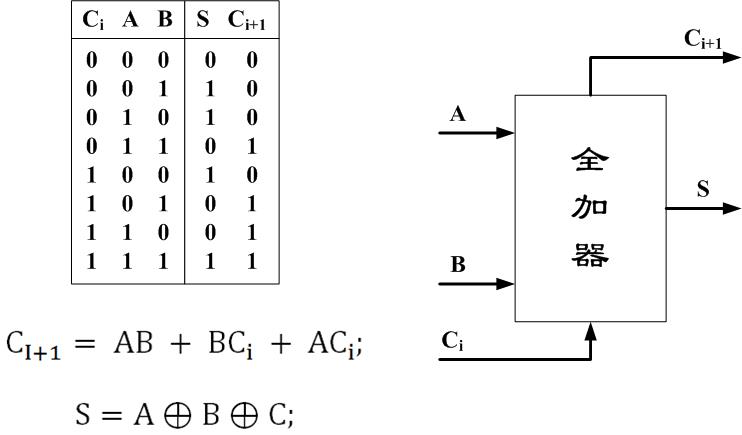

a和b为两位二进制数据,cin为前级进位位,cout为当前计算后的进位位,sum为加法结果,电路结构和真值表如下:

2 四位全加器

四位全加器是在一位全加器的基础上利用进位进行串行级联实现,实现后的电路结构示意图如下:

【源代码】

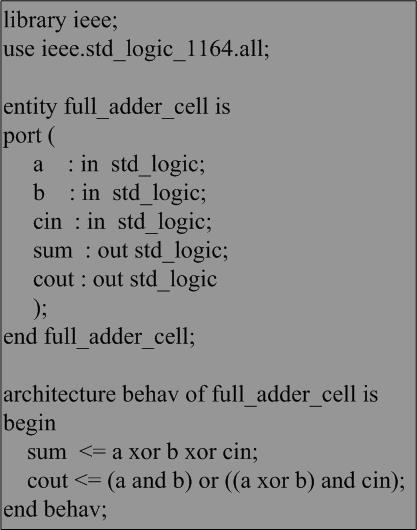

1 一位全加器源代码

2 四位全加器源代码

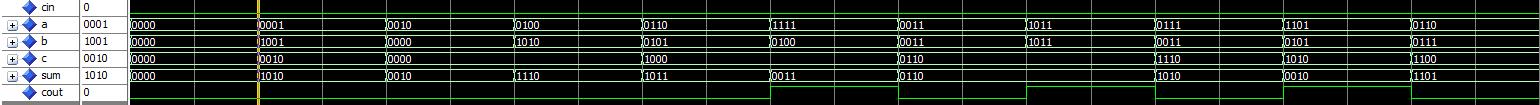

【实验结果】

【思考】

在仿真时,输入可能会存在毛刺,采用什么方法可以消除毛刺?

在设计多位全加器时,如果位数很多,用元件例化的方式程序会很长,可以采用什么方法可以改进实现?

以上是关于RTL基本知识:全加器设计(VHDL)的主要内容,如果未能解决你的问题,请参考以下文章