FPGA设计入门

Posted 满足没有

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA设计入门相关的知识,希望对你有一定的参考价值。

FPGA设计入门

1位全加器设计———原理图与VHDL设计初步

实验目的

通过1位全加器的详细设计,掌握原理图输入以及Verilog的两种设计方法。 软件基于quartusII 13.0版本,开发板基于Intel DE2-115。

半加器的设计

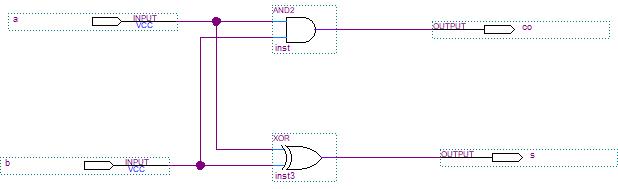

1位全加器可以用两个半加器及一个或门连接而成, 因此需要先完成半加器的设计。

使用原理图输入的方法进行底层元件设计和层次化设计的主要步骤:

1.新建工程

点击next到以下界面,给工程选择路径和取名

下一步

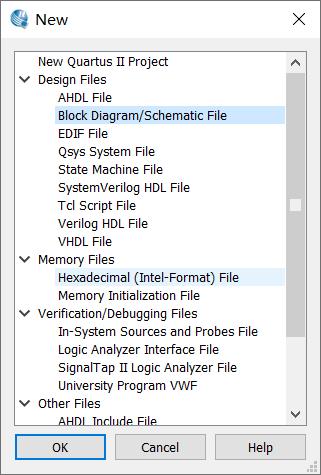

2.新建原理图文件

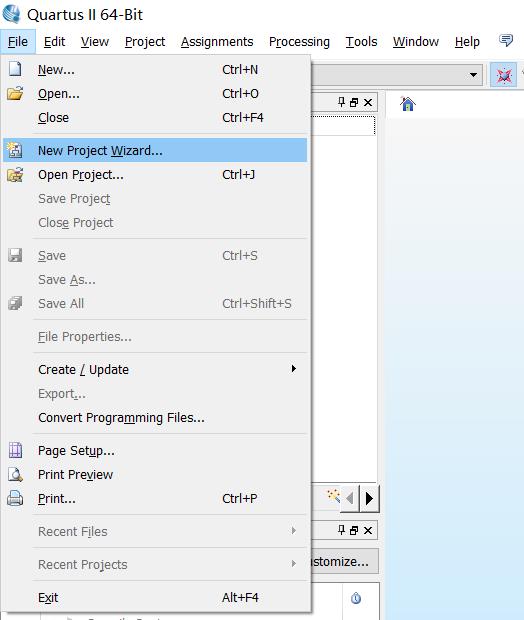

打开QuartusII,选菜单“File”一“New”,

3.在编辑窗中调入元件,完成半加器的原理图输入

点击按纽“ ”或直接双击原理图空白处,从“ Symbol”窗中选择

需要的符号,或者直接在“name”文本框中键入元件名,如“and2”为2输入与门,点OK按钮,即将元件调入原理图编辑窗中。例如为了设计半加器,分别调入元件and2,not,xnor和输入输出引脚input和output。并如图用点击拖动的方法连接好电路。然后分别在input和output的PIN NAME上双击使其变黑色,再用键盘分别输入各引脚名:a、b,co和s

4.存盘编译

选择菜单File - Save As,选择刚才为自己的工程建立的目录F:\\QuartusII_13.1\\project,将已设计好的原理图文件命名为:project1.bdf(注意默认的后缀是.bdf),并存盘在此文件夹内。然后点击编译,若无错误则可进行下一步,若有错进行原理图修改。编译完成后最下面的“message”框中信息只要没有红色的报错就可以了。

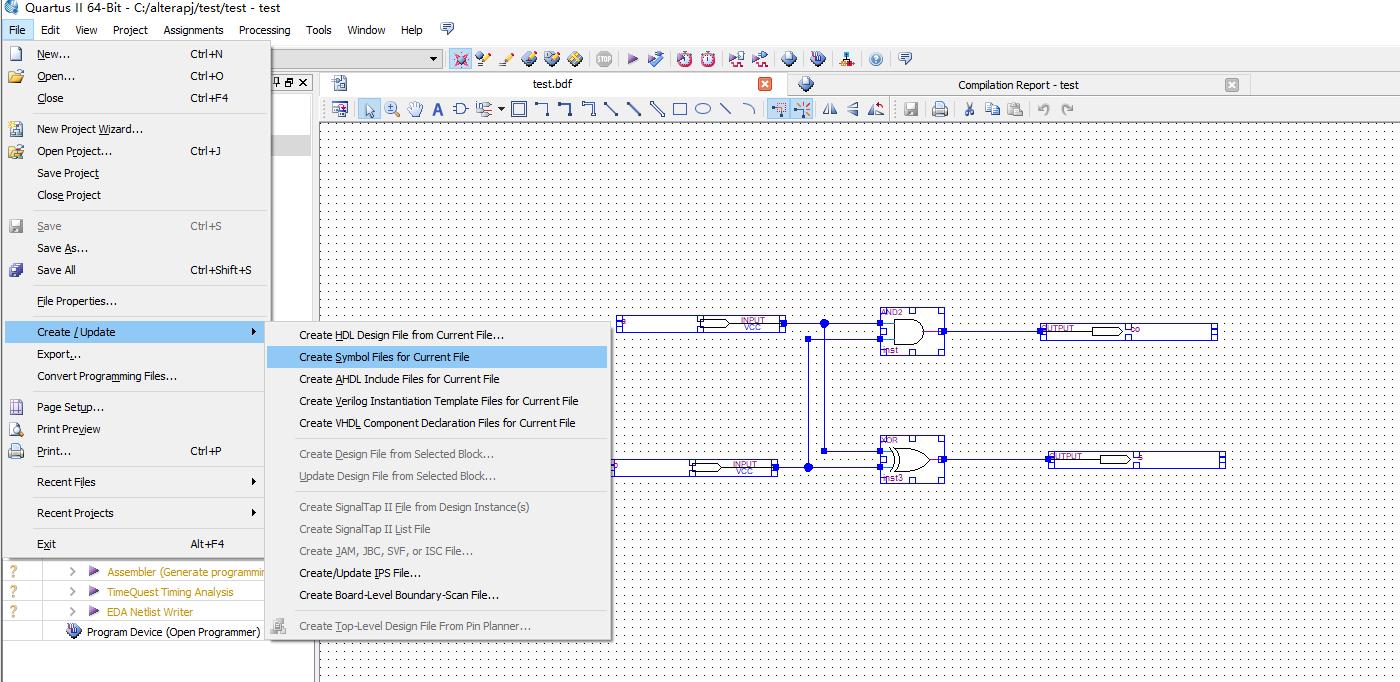

3.将设计项目设置成可调用的元件

为了构成全加器的项层设计,必预将以上设计的半加器project1.bdf设置成可调用的元件。方法图所示,在打开半加器原理图文件project1.bdf的情况下,选择菜中File中的Create/Update→Create Symbol Files for Current File项,即可将当前文件变成一个元件符号存盘,以待在高层次设计中调用。

使用完全相同的方法也可以将VHDL文本文件变成原理图中的一个元件符号,实现VHDL文本设计与原理图的混合输入设计方法。转换中需要注意以下两点:

(1)转换好的元件必须存在当前工程的路径文件夹中;

(2)该方法只能针对被打开的当前文件。

半加器仿真

(1).新建波形文件

如上面新建图形文件的方法,从“file”中选择“new”,然后从出现的对话框中选择“university program VWF”。点击“OK”。

(2)输入波形文件

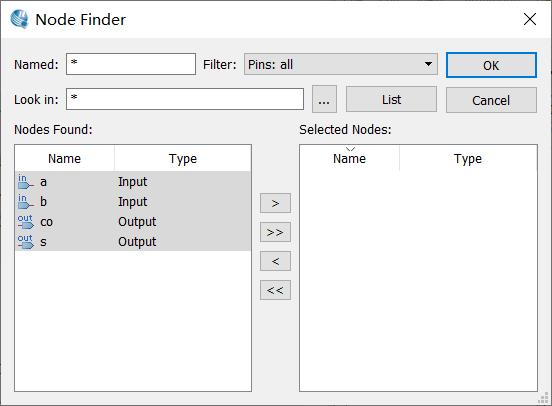

在波形文件编辑器左端大片空白处双击,出现“insert node

or bus”对话框,点击“node finder”按钮。如图。

然后在随后出现的“node finder”对话框中点击“list”按钮,则半加器中所有的输入输出引脚全部出现在对话框左边。如图

再在该界面上点击“>>”,则把左边所有的端口都选择到右边,进入波形。如图。

点击两次“OK”后,出现如图的波形文件

(3)设置输入波形取值

方法可以是选中某段需要设置数值“1”的波形,然后在工具栏上点击按钮 ,即可。反之设置“0”,或其余数值同法可行

(4)仿真

先保存文件为“project1.vwf”,点击工具栏上功能仿真按钮 ,完成后会自动跳出仿真后的文件。如图。从该图中可以分析半加器的逻辑关系是否正确。

这里编译的时候遇到了很多问题,最主要有两个问题:

1.出现以下报错

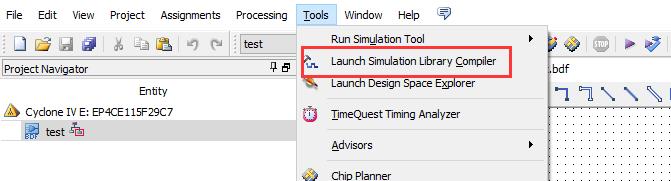

解决:点击【Tools】→【Lauch Simulation Library Compiler】

然后再进行编译就可以了。

2.出现

这个我还没找到好的方法去解决它,在这一直卡了好久,(我怀疑是用户名是中文,导致文件路径有中文)但一直没能解决,所以就很下心装了个win10的虚拟机,用英文的用户名,软件也重新安装,环境也重新设置,终于搞定了,遇到这个问题的朋友可以试试。或者有好的解决方法,欢迎解答。。。

以上是关于FPGA设计入门的主要内容,如果未能解决你的问题,请参考以下文章