FPGA代码一位半加器入门-第2篇

Posted 乔海权_429512***杭州

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA代码一位半加器入门-第2篇相关的知识,希望对你有一定的参考价值。

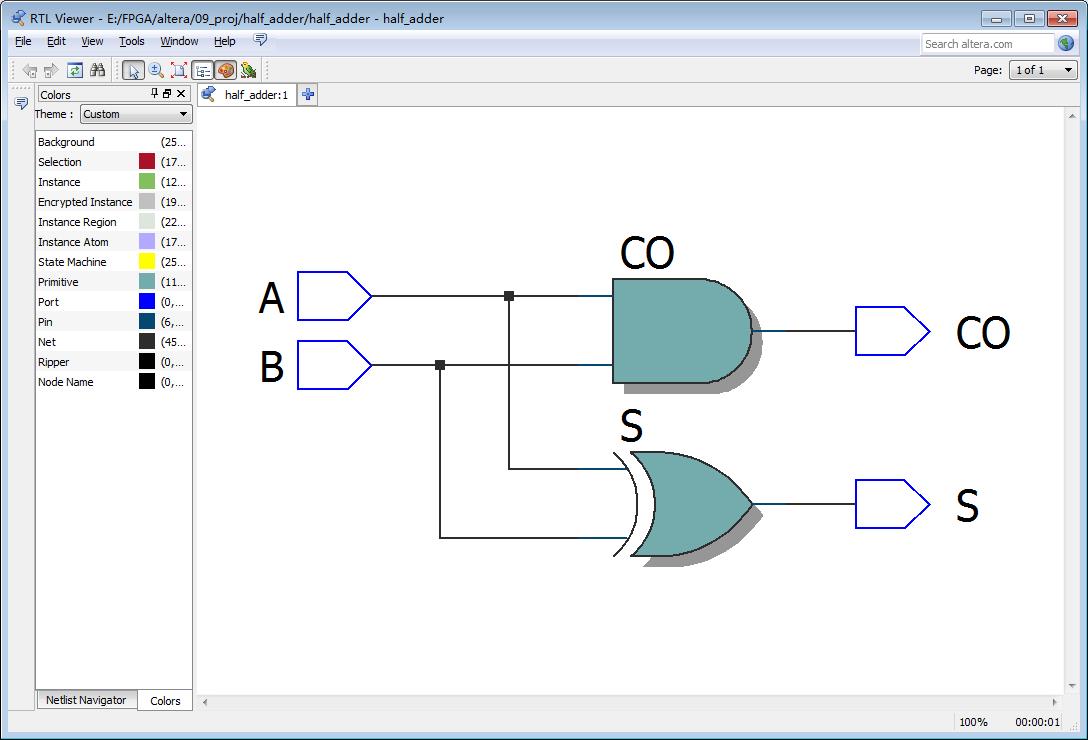

1. 代码比较简单,总结起来是用逻辑运算替代了数学运算加减,应该是因为这样的逻辑资源耗费的少。S是A+B的个位,CO是A+B的进位。

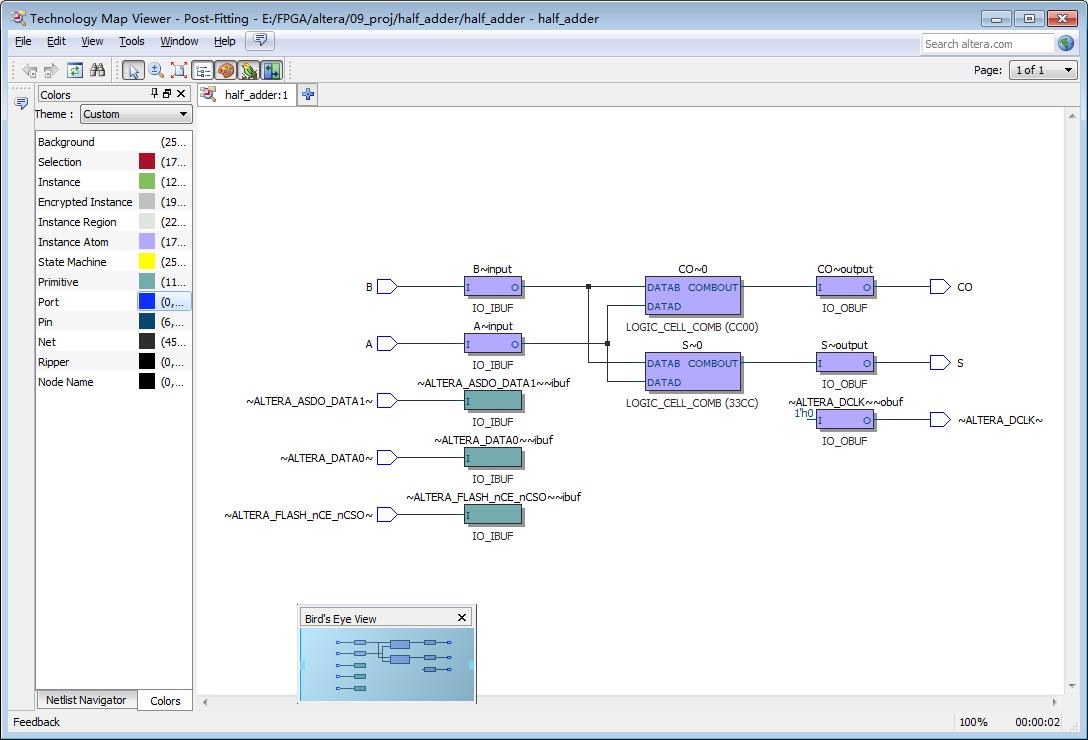

1 module half_adder(A,B,S,CO); 2 input A,B; 3 output S,CO; 4 assign S=A^B; 5 assign CO=A&B 6 endmodule

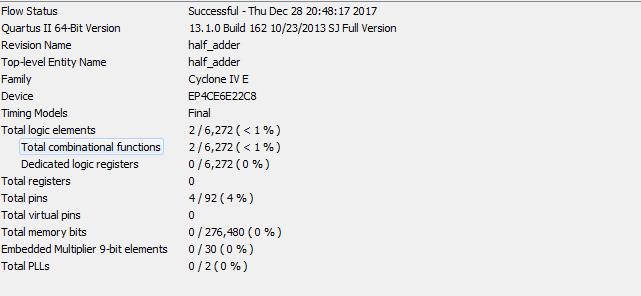

2. quartus13.1不支持中文路径,下面研究下生成的逻辑资源,差不多6K的逻辑资源,我们用到了2个,究竟是那两个?

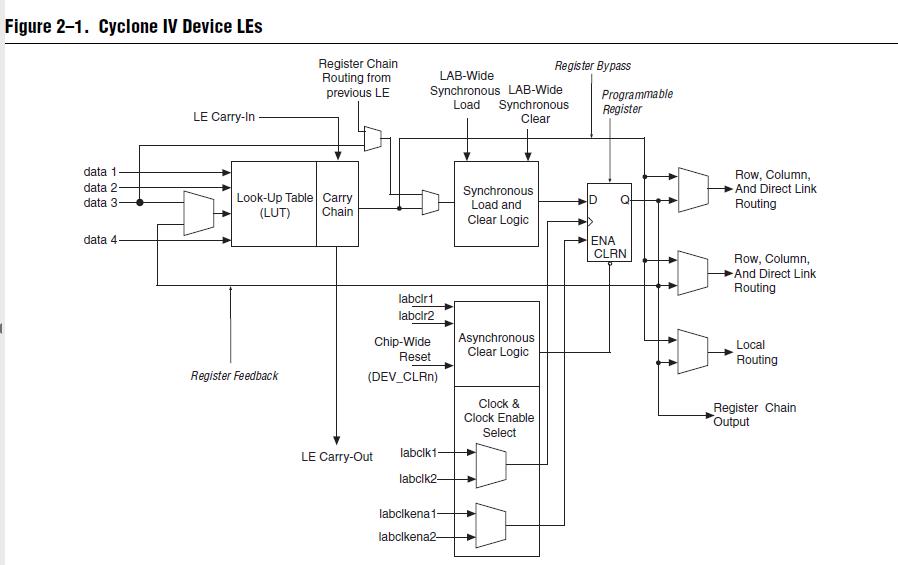

3. 当然目前猜测是CO和S各用了一个逻辑资源,一个逻辑资源包括什么?

4. 一个逻辑资源有什么,从下图看出有一个4输入的查找表,其实我也就只能看懂这些了,所以这个工程用了2个查找表,最基本的单元是LE逻辑单元

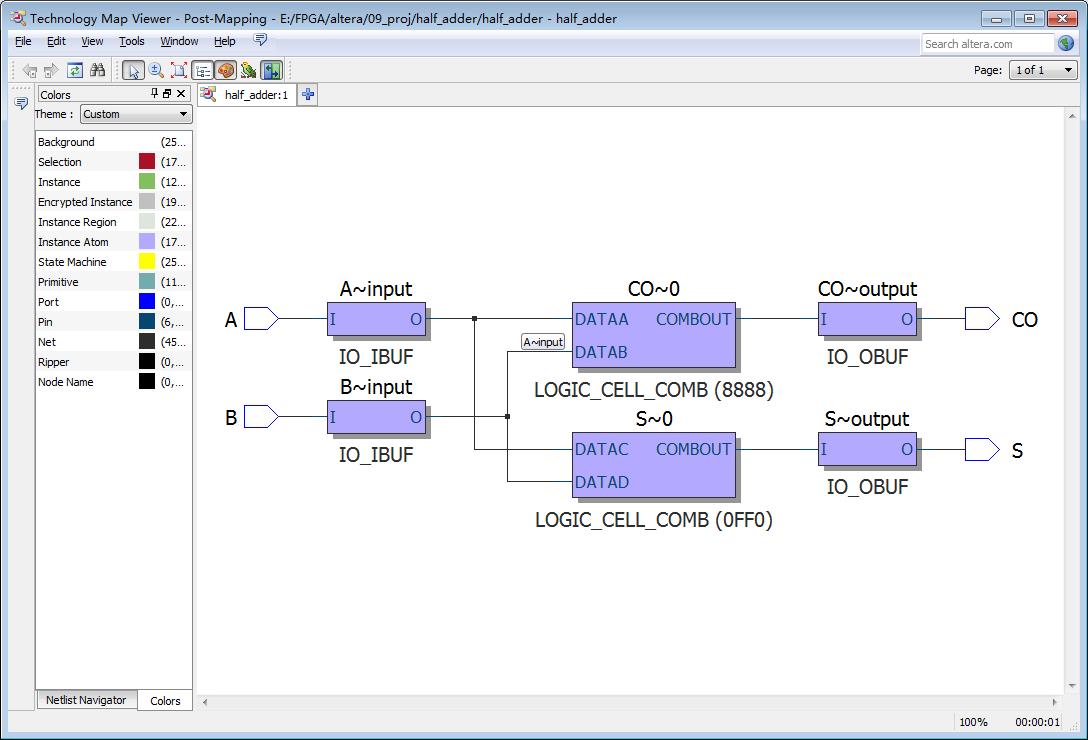

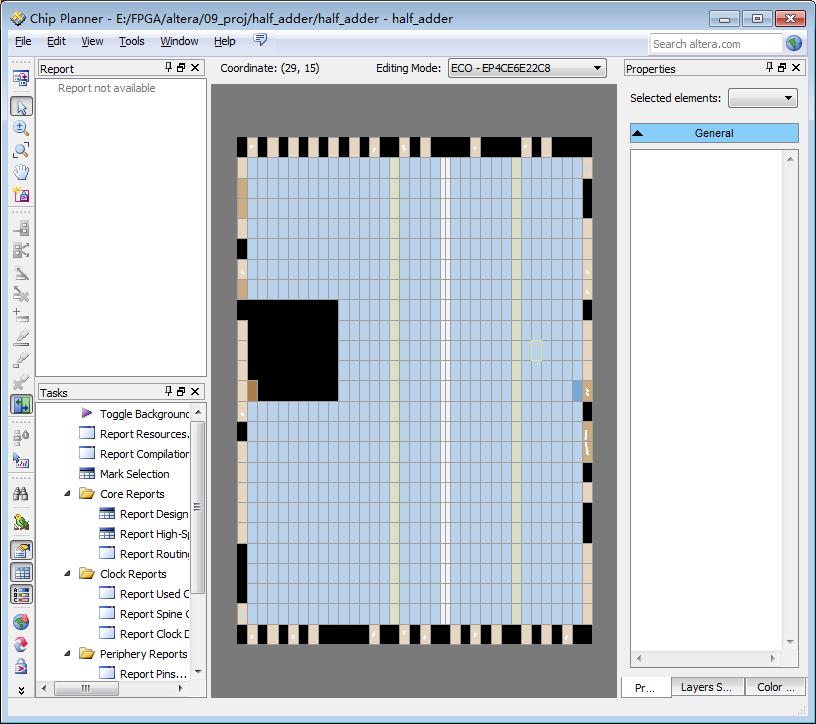

5. 看下图,上面有个鸟的图标,是鸟眼观察,只能说ALTEAR的工程师真耿直,真的放个鸟的图标,哈哈哈哈,下面两张图对比看

6. 下面一张图没看懂,应该是芯片的内部,放大都是一些框框之类的。

以上是关于FPGA代码一位半加器入门-第2篇的主要内容,如果未能解决你的问题,请参考以下文章