FPGA的学习:全加器的实现

Posted 石小舟

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA的学习:全加器的实现相关的知识,希望对你有一定的参考价值。

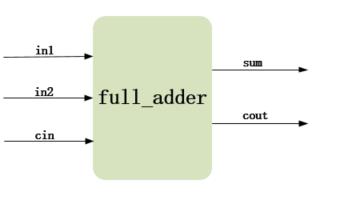

前面已经学习了半加器的实现。全加器的实现是依靠两个半加器实现,首先来看系统框图和时序图。

这里实现功能的时候用到了半加器的实例化,所以需要在此文件夹下同时放入半加器的实现,不然编译会不通过

`timescale 1ns/1ns

module full_adder

(

input wire in1 , //加数1

input wire in2 , //加数2

input wire cin , //上一级的进位

output wire sum , //两个数的加和

output wire cout //加和后的进位

);

//wire 型变量的定义

wire h0_sum;

wire h0_cout;

wire h1_cout;

//第一个实例化

half_adder half_adder_inst0

(

.in1 (in1 ),

.in2 (in2 ),

.sum (h0_sum ),

.cout (h0_cout)

);

half_adder half_adder_inst1

(

.in1 (h0_sum ),

.in2 (cin ),

.sum (sum ),

.cout (h1_cout)

);

//cout:总的进位信号

assign cout = h0_cout | h1_cout;

endmodule

对其进行仿真:

`timescale 1ns/1ns

module tb_full_adder();

//wire define

wire sum;

wire cout;

//reg define

reg in1;

reg in2;

reg cin;

//初始化输入信号

initial begin

in1 <= 1'b0;

in2 <= 1'b0;

cin <= 1'b0;

end

//in1:产生输入随机数,模拟加数1的输入情况

always #10 in1 <= {$random} % 2;

//in2:产生输入随机数,模拟加数2的输入情况

always #10 in2 <= {$random} % 2;

//cin:产生输入随机数,模拟前级进位的输入情况

always #10 cin <= {$random} % 2;

initial begin

$timeformat(-9, 0, "ns", 6);

$monitor("@time %t: in1=%b in2=%b cin=%b sum=%b cout=%b", $time, in1, in2, cin, sum, cout);

end

//实例化

full_adder full_adder_inst

(

.in1 (in1 ), //input in1

.in2 (in2 ), //input in2

.cin (cin ), //input cin

.sum (sum ), //output sum

.cout (cout ) //output cout

);

endmodule

以上是关于FPGA的学习:全加器的实现的主要内容,如果未能解决你的问题,请参考以下文章