阻抗匹配处理方式

Posted alifpga

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了阻抗匹配处理方式相关的知识,希望对你有一定的参考价值。

关于阻抗匹配的处理方式

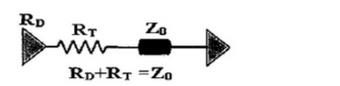

串联端接方式

靠近输出端的位置串联一个电阻,要达到匹配效果,串联电阻和驱动端输出阻抗的总和应等于传输线的特征阻抗Z0。

在通常的数字信号系统中,器件的输出阻抗通常是十几欧姆到二十几欧姆,传输线的阻抗通常会控制在50欧姆,所以始端匹配电阻常见为33欧姆电阻。

当然要达到好的匹配效果,驱动端输出到串联电阻这一段的传输路径最好较短,短到可以忽略这一段传输线的影响。

串联电阻优缺点如下:

优点

1、只需要一个电阻;

2、没有多余的直流功耗;

3、消除驱动端的二次反射;

4、不受接收端负载变化的影响;

缺点

1、接收端的一次发射依然存在;

2、信号边沿会有一些变化;

3、电阻要靠近驱动端放置,不适合双向 传输信号;

4、在线上传输的电压是驱动电压的一半,不适合菊花链的多型负载结构。

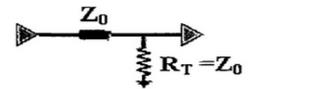

并联端接方式

并联端接又叫终端匹配,要达到阻抗匹配的要求,端接的电阻应该和传输线的特征阻抗Z0相等。

在通常的数字信号传输系统里,接收端的阻抗范围为几兆到十几兆,终端匹配电阻如果和传输线的特征阻抗相等,其和接收端阻抗并联后的阻抗大致还是在传输线的特征阻抗左右,那么终端的反射系数为0。不会产生反射,消除的是终端的一次反射。

并联端接优缺点

优点

1、适用于多个负载

2、只需要一个电阻并且阻值容易选取

缺点

1、增加了直流功耗

2、并联端接可以上拉到电源或者下拉到地,是的低电平升高或者高电平降低,减小噪声容限。

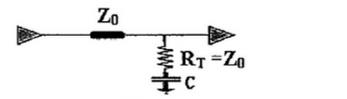

AC并联端接

并联端接为消除直流功耗,可以采用如下所示的AC并联端接(AC终端匹配)。要达到匹配要求,端接的电阻应该和传输线的特征阻抗Z0相等。

优缺点描述如下:

优点

1、适用于多个负载

2、无直流功耗增加

缺点

1、需要两个器件

2、增加了终端的容性负载,增加了RC电路造成的延时

3、对周期性的信号有效(如时钟),不适合于非周期信号(如数据)

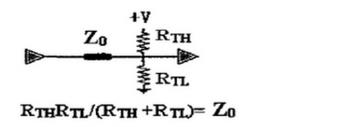

戴维南端接

戴维南端接同终端匹配,如图,要达到匹配要求,终端的电阻并联值要和传输线的特征阻抗Z0相等。

优缺点描述:

优点

1、适用于多个负载

2、很适用于SSTL/HSTL电平上拉或下拉输出阻抗很好平衡的情况。

缺点

1、直流功耗增加

2、需要两个器件

3、端接电阻上拉到电源或下拉到地,会使得低电平升高或高电平降低

4、电阻值较难选择,电阻值取值小会使低电平升高,高电平降低更加恶劣;电阻值取大有可能造成不能完全匹配,使反射增大,可以通过仿真来确定。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

以上是关于阻抗匹配处理方式的主要内容,如果未能解决你的问题,请参考以下文章