硬件设计--特性阻抗匹配详解

Posted wcat

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了硬件设计--特性阻抗匹配详解相关的知识,希望对你有一定的参考价值。

参考资料:信号反射与振铃产生

一、基本概念介绍与理解

1、特性阻抗

特性阻抗(又称特征阻抗)并不是实际的电阻,而是属于长线传输中的概念。在射频范围内,信号传输的过程中,信号沿到达的地方,信号线和参考平面(电源或地平面)间由于电场的建立,会产生一个瞬时电流,如果传输线是各向同性的,那么只要信号在传输就始终存在一个电流I,而如果信号的输出电平为V,在信号传输的过程中,传输线就会等效成一个电阻,大小为V/I。把这个等效的电阻称为传输线的特性阻抗ZO。信号在传输过程中,如果传输路径上的特性阻抗发生变化,信号就会在阻抗不连续的结点发生反射。影响特性阻抗的因素为:介电常数、介质厚度、线宽、铜箔厚度;而与工作频率、传输线长短、所接射频器件无关。

2、电压驻波比

电压驻波比(VSWR):指驻波波腹电压与波节电压幅度之比,驻波比等于1时,表示馈线和天线的阻抗完全匹配,此时高频能量全部被天线辐射出去,没有能量的反射损耗;驻波比无穷大时,表示全反射,能量完全没有辐射出去。

计算公式:VSWR=(1+K)/(1-K);

3、反射系数

反射系数(反射电压与输入电压的比值)是衡量信号反射量的重要指标,其定义为:K=( ZL - ZO)/( ZL + ZO),ZL为变化后的阻抗,ZO为变化前的阻抗;如果负载和传输线完全匹配,K=0,VSWR=1:1;

*下面通过信号振铃现象的产生原理来增强对信号反射的理解

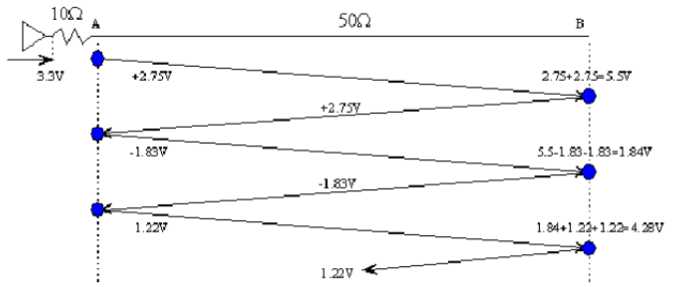

如图1所示,假设驱动端的输出阻抗为10Ω,输出3.3V电压信号,PCB走线的特征阻抗为50Ω;为了分析方便,假设负载端开路,即负载阻抗无穷大,并且忽略传输线寄生电容和寄生电感的影响,只考虑阻性负载。

图1 振铃现象产生过程

第一次反射:信号从芯片内部发出,经过10Ω输出阻抗和50ΩPCB特征阻抗的分压,实际加到PCB走线上的信号为A点电压3.3*50/(10+50)=2.75V;传输到远端B点,由于B点开路,阻抗无穷大,反射系数为1,即信号全部反射,所以反射信号也为2.75V,此时B点测量电压为2.75V+2.75V=5.5V;

第二次反射:2.75V反射电压回到A点,阻抗由50Ω变为10Ω,发生负反射,A点反射系数为K=-2/3,即反射电压为-1.83V,该电压到达B点,再次发生反射,由于反射系数为1,反射电压也为-1.83V,此时B点测量电压为5.5V-1.83V-1.83V=1.84V(此处两个1.83V电压,一个是由A点传输过来的,一个是在B点反射造成的);

第三次反射:从B点反射回来的-1.83V电压到达A点后,再次发生反射,反射电压为1.22V。该电压到达B点后再次发生正反射,反射电压同样为1.22V,所以B点电压变为1.84+1.22+1.22=4.28V;

由于信号在A点和B点之间来回反射,引起B点电压不稳定,从而在B点形成振铃现象,所以如果在A点或者B点做好阻抗匹配,则反射信号就不会来回反射,从而保证了信号的稳定。

二、阻抗匹配的理解

阻抗匹配是指信号源或者传输线跟负载之间的一种合适的搭配方式,阻抗匹配可分为低频和高频两种情况考虑。

低频情况下:阻抗匹配主要是保证负载上可获得最大输出功率。在直流情况下,负载阻抗等于信号源内阻(对于前后级情况,信号源内阻即为前级输出阻抗)时,实现阻抗匹配。在交流情况下,负载阻抗与信号源内阻符合共轭匹配时,负载获得最大输出功率。如果我们需要输出电流大,则选择小的负载电阻R;如果我们需要输出电压大,则选择大的负载R;如果我们需要输出功率最大,则选择和信号源内阻匹配的负载R。

高频情况下:当信号的频率很高时,为避免信号反射,传输线与负载必须进行阻抗匹配:负载阻抗必须和传输线阻抗相等。如果不匹配,则会形成反射,能量传递不下去,降低效率,会在传输线上形成驻波;高速信号线与负载阻抗不匹配,会产生震荡,辐射干扰等。

三、阻抗匹配方式

通过上述对特征阻抗及信号振铃现象产生原理的理解,可得出以下几种实现阻抗匹配的方法。

3.1、串联终端匹配

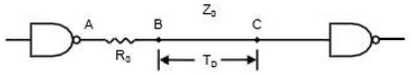

图2 串联终端匹配

串行连接终端匹配技术是在源端的一种终端匹配技术,和其他类型的终端匹配技术不同。串行连接终端匹配技术是由连接在驱动器输出端和信号线之间的一个电阻组成,驱动器输出阻抗RD以及电阻R的和必须与信号线的特征阻抗ZO匹配;

在串行连接终端匹配技术中,由于信号会在驱动器的阻抗RD、串行匹配电阻RS以及传输线特性阻抗ZO之间实现信号电压的分压,因而加在传输线上的电压只有信号电压的一半;而在接收端,由于传输线阻抗和接收器输入阻抗的不匹配(通常情况下接收器的输入阻抗比传输线阻抗高得多),所以导致产生幅值大致相同的信号反射,故在负载端的信号电压大约是驱动器输出电压的一半,再加上同样幅值的信号反射电压,使得接收器马上就会接收到完整的信号电压;而反射电压会反向传递到驱动端,但是串行连接的匹配电阻在驱动器端实现了反射信号的终端匹配,因而不会出现进一步的信号反射,从而保证了传输线上信号的完整性。

优点:1.器件单一,只需要一个电阻元件;

2.抑制振铃,减少过冲;

3.增强信号完整性,产生更小的EMI;

4.适用于集总线型负载和单一负载;

缺点:1.接收端的反向反射依然存在;

2.影响信号上升时间并增加信号延时;

3.分布式负载不适用,因为在走线路径的中间,电压仅为源电压的一半;

4.当TTL、CMOS器件出现在相同网络时,串联匹配不是最佳选择;

3.2、并联终端匹配

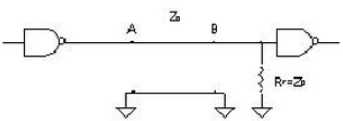

图3 并联终端匹配

并联终端匹配是最简单的阻抗匹配技术, 通过一个电阻R将传输线的末端(可能是开路,也可能是负载)接到地或者接到VCC上,电阻R的值必须同传输线的特征阻抗ZO匹配,以消除信号的反射。如果R同传输线的特征阻抗ZO匹配,那么匹配电阻将吸收造成信号反射的能量,而不管匹配电压的值,在数字电路的设计中,返回通路上吸收的电流通常都大于电源上提供的电流(这句话我也不理解)。

将终端匹配到VCC可以提高驱动能力,而将终端匹配到地则可以提高地上的吸收能力。所以,对于50%占空比的信号而言,将终端匹配到VCC要优于将终端匹配到地。

优点:1.器件单一,只需要一个电阻元件;

2.适用于分布式负载;

3.反射几乎可以完全消除;

4.电阻阻值易于选择;

缺点:1.该电阻会增加系统电路的功耗;

2.降低了噪声容限(比如将TTL输出终端匹配到地会降低VOH的电平值,从而降低接收器输入端的抗噪声能力);

3.3、戴维南终端匹配

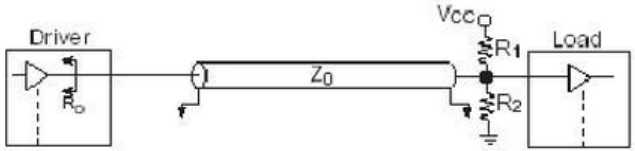

图4 戴维南终端匹配

戴维南终端匹配技术也叫做双终端匹配技术也就是双电阻形式的并联匹配,它采用两个电阻R1和R2来实现终端匹配,要求的电流驱动能力比单电阻形式小,这是由于R1和R2的并联值与传输线的特性阻抗相匹配,每个电阻都比传输线的特性阻抗大。根据戴维南终端匹配设计规则,R1通过从VCC向负载注入电流来帮助驱动器更容易到达逻辑高状态;R2帮助通过向地吸收电流来将驱动器下拉到逻辑低状态。当R1和R2的并联同信号线的特征阻抗ZO匹配时可以加强驱动器的扇出能力,并且减小由于信号占空比的变化导致的功耗的改变。

优点:1.终端匹配电阻采用上下拉的方式,有效抑制信号过冲;

2.信号摆幅降低,加强了系统噪声容限;

3.增强驱动器驱动能力,在5V和3.3V的CMOS和BiCMOS的系统中显得尤为有益;

缺点:1.存在静态直流功耗;

2.戴维南电压接近于器件的开关阈值电压,对于CMOS逻辑器件来说会导致更高的功耗;

扩展资料:戴维南终端匹配设计规则

1、两个电阻的并联值必须与传输线的特性阻抗相等;

2、与电源VCC连接的电阻不能太小,需保证驱动器的IOL电流在驱动器的性能指标范围以内,以免信号为低电平时灌电流过大,损坏器件;

3、与地连接的电阻不能太小,需保证驱动器的IOH电流在驱动器的性能指标范围以内,以免信号为高电平时拉电流过大,损坏器件;

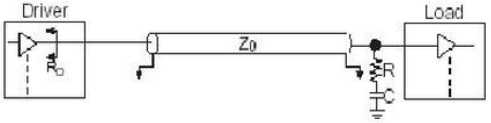

3.4、RC终端匹配

图5 RC终端匹配

RC终端匹配技术也称之为AC终端匹配技术,它是由一个电阻R和一个电容C组成的,电阻R和电容C连接在传输线的负载一端。对于RC终端匹配来说,电阻R的值必须同传输线的特征阻抗ZO的值匹配才能消除信号的反射,而电容的值的挑选却十分复杂,这是因为电容值较小的话会导致RC时间常数过小,这样一来RC电路就类似于一个尖锐信号沿发生器,从而引起信号的过冲与下冲,反之,较大的电容值会引入更大的功耗;信号的频率、信号占空比、以及过去的数据位模式等因素都会影响终端匹配电容的充电和放电特性,从而影响功率消耗。通常情况下,RC时间常数大于该传输线负载延时的两倍较为理想。

RC终端匹配技术的优势在于终端匹配电容阻断了直流通路,因此节省了可观的功率消耗,同时恰当地选取匹配电容的值,可以确保负载端的信号波形接近理想的方波,同时信号的过冲与下冲又都很小。

RC终端匹配技术的一个缺点是信号线上的数据可能出现时间上的抖动,这取决于在此之前的数据模式。举例来说,一长串比较接近的数据位会导致信号传输线和电容充电到驱动器的最高输出电平的值,如果紧接着的是一个相位相反的数据位就需要花比正常情况更长的时间来确保信号跨越逻辑阈值电平。因此在设计系统时序的余量时务必将这一额外的时间考虑在内以确保设计的系统能够正常运作。

3.5、肖特基二极管终端匹配

肖特基二极管终端匹配技术也称之为二极管终端匹配技术,由两个肖特基二极管组成,此法不属于阻抗匹配的思路,而是通过二极管的钳位来减小过冲和下冲;传输线末端的信号反射,导致负载输入端上的电压升高超过VCC和二极管D1的正向偏值电压,使得该二极管正向导通连接到VCC上,从而将信号的过冲嵌位在VCC和二极管的阈值电压的和上,同样,连接到地的二极管D2也可以将信号的下冲限制在二极管的正向偏置电压上;因为二极管不会吸收任何的能量,仅仅只是将能量导向电源或者地,传输线上就会出现多次的信号反射。由于能量会通过二极管到电源和二极管到地的消耗,信号的反射会逐渐衰减,能量的损耗限制了信号反射的幅度,以维持信号的完整性。

以上是关于硬件设计--特性阻抗匹配详解的主要内容,如果未能解决你的问题,请参考以下文章