verilog--逻辑仿真的构成及设计举例

Posted PDF同学

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了verilog--逻辑仿真的构成及设计举例相关的知识,希望对你有一定的参考价值。

1、 模块设计完成之后,我们需要检验功能的正确性,通过设计激励块来完成测试。(可以把激励块理解成一个新的设计块,但是又和原来的设计块存在联系)

将激励块和测试块分开设计是一种良好的设计风格。激励块一般称为测试台。可以使用不同的测试台对设计块进行全面测试。

2、激励块的设计有两种模式。

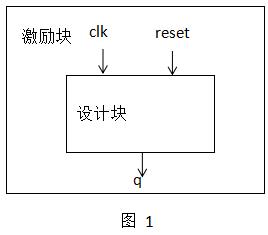

一种是将激励块作为顶层模块,调用(实例引用)并直接驱动设计块,如图1。顶层为激励块,由它控制clk和reset信号,检查并显示输出信号q。

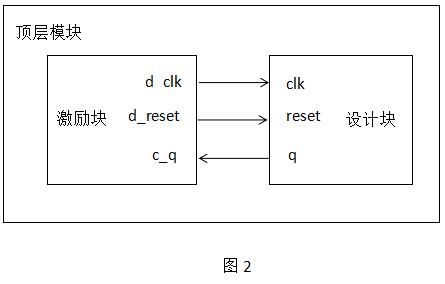

另一种是在一个虚拟的顶层模块中调用(实例引用)激励块和设计块,激励块和设计块之间通过接口进行交互,如图2。激励块驱动信号d_clk和d-reset,这两个信号则连接到设计块的clk和reset输入端口,激励模块同时检查和显示信号c_q,这个信号连接到输出端口q,顶层模块的作用只是调用(实例引用)设计块和激励块。

3、设计举例

☆设计块:我们使用自顶向下的方法设计。

①顶层模块:脉动进位计数器

module ripplp_carry_counter(q,clk,reset); output [3:0] q; input clk, reset; //调用(实例引用)四个T触发器 T_FF tff0(q[0],clk,reset); T_FF tff1(q[1],clk,reset); T_FF tff2(q[2],clk,reset); T_FF tff3(q[3],clk,reset); endmodule

②定义模块T_FF

module T_FF(q,clk,reset); output q; input clk, reset; wire d; D_FF dff0(q,d,clk,reset);//调用(实例引用)一个D触发器 not n1(d,q);//调用(实例引用)一个非门,非门是verilog语言的内置原语部件 endmodule

③定义模块D触发器

//异步复位D触发器 module D_FF(q,d,clk,reset); output q; input d,clk,reset; reg q; always @(posedge reset or negedge clk) if (reset) q<=1\'b0; else q<=d; endmodule

通过以上三步,我们按照自顶向下的设计方法完成了设计块。接下来就要对设计块施加激励信号以检验其是否正确,即设计激励块。

☆激励块:激励块可以看做是一个新的模块,但同时又和设计块一一对应。在这一例中按照前面的第一种方法来设计激励块,即在激励块中实例引用设计块。

①激励块的编写

module stimulus; reg clk; reg reset; wire [3:0] q; //实例引用已经设计好的模块 ripple_carry_counter r1(q,clk, reset); //控制驱动设计块的时钟信号,时钟周期为10个单位时间 initial clk =1\'b0;//把clk设置为0 always #5 clk =~clk;//每5个时间单位时钟翻转一次,即时钟周期为10个时间单位 //控制驱动设计块的reset信号 initial begin reset = 1\'b1; #15 reset = 1\'b0; #180 reset = 1\'b1; #10 reset =1\'b0; #20 $finish;//终止仿真 end //监视输出 initial $monitor($time," Output q= %d",q); endmodule

在激励块设计完成之后就可以进行仿真来验证设计块的功能正确性了。

②仿真

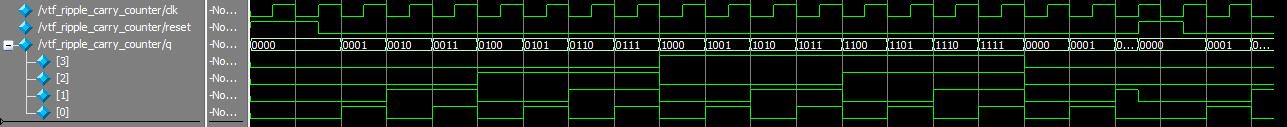

在激励块中信号有clk,reset,和计数器的4位输出。

信号clk的重复周期为10个单位;

信号reset在0-15和195至205两个时间区段为1,其余时刻为0;

输出信号q从0开始计数到15;

整个仿真在225个时间单位(此例中每个单位为1ns)终止。

仿真结果如下图所示:

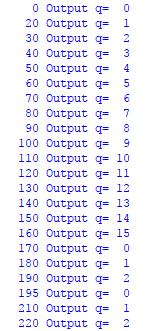

检测输出结果为:

以上是关于verilog--逻辑仿真的构成及设计举例的主要内容,如果未能解决你的问题,请参考以下文章

verilog中`timescale后面的单位最小可以定义为多少?和啥有关?

使用74LS83构成4位二进制全加\全减器。 具体要求:1)列出真值表; 2)画出逻辑图; 3)用Verilog HDL仿真