verilog行为仿真时钟激励显示总是z

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了verilog行为仿真时钟激励显示总是z相关的知识,希望对你有一定的参考价值。

仿真代码如下:

module test();

div div(

.CLK(CLK),

.CLK_out(CLK_out)

);

reg CLK=0;

wire CLK_out;

initial

begin

while(1)begin

CLK=0;

#100;

CLK=1;

#100;

CLK=0;

#100;

CLK=1;

#100;

end

end

endmodule

使用的是vivado

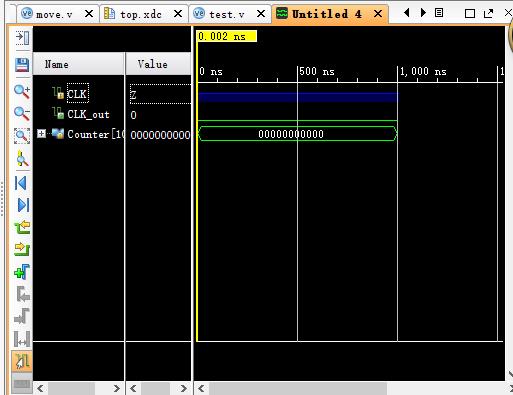

仿真波形如下。我的激励根本没起作用。

创造时钟激励的写法确实有问题。。然后我改了。。仿真结果依然是z,不止这个程序,我按书上的例程照抄然后进行仿真CLK信号也是z。。我写的时钟激励信号根本输不进去

参考技术B reg CLK = 0; 改成 reg CLK;追问改了之后还是z。。。

追答你的div代码是不是也乱赋值了?

试试这个:

module div (CLK, CLK_out);

input CLK;

output CLK_out;

assign CLK_out = CLK;

endmodule

如果还不行,换编译器吧。

z(高阻)的形成的还有一个原因是内部定义是tri类型。其他都应该是 x(不确定) 态。

请问tri类型是什么意思。。

参考技术C 最后怎么解决的 我也是这样以上是关于verilog行为仿真时钟激励显示总是z的主要内容,如果未能解决你的问题,请参考以下文章