从延迟触发器链到边沿检测

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了从延迟触发器链到边沿检测相关的知识,希望对你有一定的参考价值。

本文记录一下关于延迟触发器链与它的常用用法(即边沿检测。多级延迟的触发器应该是比较常用的,当我们需要对信号信号进行延时,这个时候我们就用到了延迟触发器链。下面就来记录一下吧。

一、多级延迟触发器(或延迟触发器链)

(1)多级延迟触发器电路

多级延迟触发器,顾明思议就是多个触发器串在一起,对信号进行打拍,一个触发器就延时了一拍,也就是延迟了一个时钟周期。

多级触发器的代码如下所示:

1 module DFF_N #(parameter N=3)( 2 input clk, 3 input reset, 4 input [N-1:0] D, 5 output reg [N-1:0] Q 6 ); 7 reg [N-1:0]d0; 8 reg [N-1:0]d1; 9 always@(posedge clk or negedge reset) 10 if(!reset)begin 11 d0 <= 0; //同步清 0,低电平有效 12 d1 <= 0; //同步清 0,低电平有效 13 Q <= 0; //同步清 0,低电平有效 14 end 15 else begin 16 d0 <= D; 17 d1 <= d0; 18 Q <= d1; 19 end 20 21 endmodule

d0 是 D 的延迟一级采样或者称为 D 的延迟一拍信号,同样 d1 是 D 的延迟两拍信号,而 Q 则是 延迟三拍信号。一方面可以通过修改N来改变对多少位的信号的进行延时;另一方面,可以用通过修改部分代码,添加或者减少延迟计数。

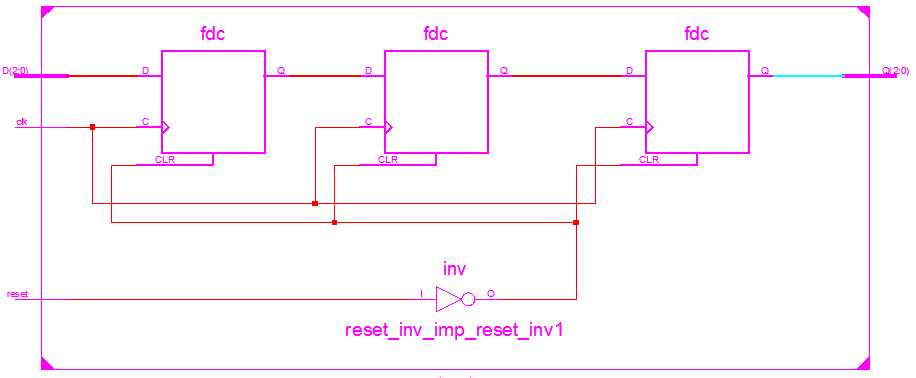

代码综合得到的电路(综合之后)如下所示:

电路中显示出三级延时,可以延时三个时钟节拍(也就是三个时钟周期),需要说明的是,上述每一级触发器都包含了3个触发器(对三位数据总线进行延时)。

(2)多级延迟触发器的主要用法

①简单的延时

多级延迟触发器最原始的作用单纯的对 D 信号做延迟操作,这里就不进行详述。

②降低亚稳态往后级传输的概率

如果 D 信号相对 clk 属于不稳定信号,则 Q 和 d1 输出相对 clk 属 于稳定信号,这样就有效地降低了亚稳态往后级传输的概率,多级延时触发器链有时也称为同步器。有关多级触发器在降级亚稳态传输概率的内容,请查看我的另一篇博文:http://www.cnblogs.com/IClearner/p/6485389.html 。

③用来边沿检测

可以通过 d1 和 Q 信号获取 D 信号的上升沿或者下降沿,具体介绍如下第二大点所示。

二、边沿检测电路

边沿检测的电路如下所示:

代码如下所示:

综合得到的电路如下所示:

以上是关于从延迟触发器链到边沿检测的主要内容,如果未能解决你的问题,请参考以下文章