ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型- 其它

Posted HZero

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型- 其它相关的知识,希望对你有一定的参考价值。

1. 前言

2.可配置的指令使能/禁用控制和trap控制

- 指令使能/禁用

当指令被禁用,则这条指令就会变成未定义

- 指令Trap控制

控制某条或某些指令在运行时进入陷阱,进入陷阱的指令会产生trap异常,路由规则如下:

(1)当前为EL1,则陷阱异常传递给EL1(HCR_EL2.TGE定义为1时,会路由到EL2);

(2)当前为EL2,则陷阱异常传递给EL2;

(3)当前为EL3,则陷阱异常传递给EL3;

3. 系统调用

- SVC

默认情况下SVC产生supervisor call,同步异常目标级别为EL1,使得运行EL0的软件可以调用EL1下的操作系统或软件的接口

- HVC

如果实现了EL2,默认情况下HVC产生hypervisor call,同步异常目标级别为EL2

注:HVC指令在EL0和secure EL1没有定义

- SMC

如果实现了EL3,默认情况下SMC产生Secure monitor Call,同步异常目标级别为EL3

注:SMC指令在EL0未定义

注:

1.此处说的默认情况需满足如下两个条件:

(1)系统调用指令的运行等级低于或等于目标异常级别;

(2)系统调用指令没有被trap控制到其他异常级别???

2. 如果运行HVC和SVC的异常级别高于目标异常级别,会引发异常,并被传递给当前异常级别;

3. EL3和EL2可以禁用HVC系统调用;

4. EL2可通过trap(配置陷阱异常)的方式调用SMC;

5. EL3可以禁用SMC

4. 低功耗模式机制

- Send Event指令

(1)SEV指令,在多处理器系统中,event会被发送给所有的PE;

(2)SEVL指令,设置本地event Register;

注:

(1)建议SEV前加DSB保证内存访问完成;

(2)SEVL与WFE在同个PE执行,不需要加屏障

所有的异常级别都可以执行SEV和SEVL指令;

- Event Register

Event register对应每个PE都有一个bit,如果置位说明有一个事件发生,PE要请求某些行为。有如下事件均可导致event register置位:

(1)执行SEV指令;

(2)当前PE执行SEVL指令;

(3)异常返回;

(4)global monitor中关于本PE的标记位被清除;

(5)来自于generic timer event stream的事件;

(6)发送自定义事件

- Wait for Event(WFE)

|

PE可以通过使用WFE指令进入低功耗状态,依赖Event register的值,如果接收到WFE wake-up event,会离开低功耗状态。利用WFE指令可以减少spin lock机制的功耗; |

|

|

WFE指令 |

|

|

WFE wake-up event in AArch64 |

注:并不是如上所有事件都会设置event register |

- Wait for Interrupt(WFI)

|

WFI |

软件可以通过使用WFI命令让PE进入低功耗状态。PE进入低功耗状态后,如果接收到WFI wake-up event,会离开低功耗状态 |

|

WFI wake-up event |

|

5. Self-hosted debug

- debugger

Self-hosted debug:PE自身拥有debugger调试器,debugger调试器通过编程让PE产生debug异常

Externel debug:PE受外部debugger调试器的控制,debugger调试器通过编程让PE产生debug事件,这样可以让PE进入debug状态,在debug状态,PE被halted

- Debug异常

Debug异常包括:

(1)Breakpoint Instruction exceptions

(2)Breakpoint exceptions.

(3)Watchpoint exceptions.

(4)Vector Catch exceptions.

(5) Software Step exceptions

要产生debug异常,需要满足2个条件:

(1)使能Debug异常;

(2)当前的EL和secure state使能debug异常

- Debug mask bit

当目标异常级别是当前异常级别时PSTATE的D bit可以maskWatchpoint, Breakpoint, and Software Step exceptions

6. Performance Monitor Extension

PMU(Performance Monitor Unit)提供如下:

1. 一个64bit时钟计数器

2.一个自定义数目的32bit事件计数器,每个事件计数器记录某一事件的发生次数

7. Interprocessing

|

Interprocessing |

用来描述AArch32与AArch64运行状态切换的术语 |

|

运行状态切换时机 |

运行状态只能在异常级别变化的时候才能进行切换,也即运行状态只能发生在捕获到异常时传递给高异常级别或从异常返回时返回到低异常级别 |

|

当捕获一个异常并切换到更高的异常级别,运行状态可以保持不变 或 32->64 |

|

|

当从一个异常返回切换到更低的异常级别,运行状态可以保持不此案或 64->32 |

8. 自定义实现对编程模型的影响

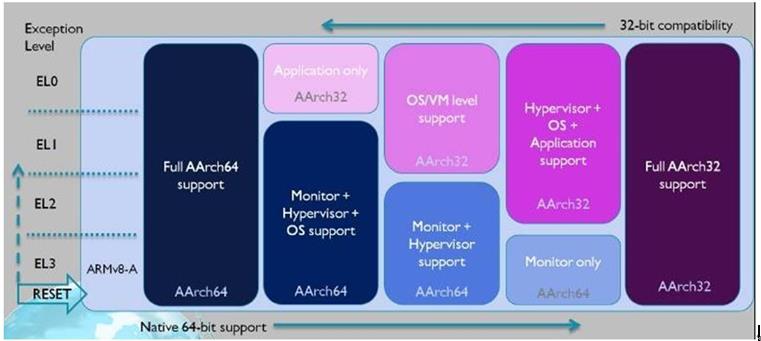

- ARMv8三个自定义选项

(1)实现的异常级别的数目;

(2)哪些异常级别支持AArch32,哪些异常级别支持AArch64;

(3)SIMD和Float-point是否支持

- 异常级别实现暗含的内容

1. 所有实现必须包含EL0和EL1;

2. EL2和EL3是可选的

3. 可选的组合方式有:

(1)EL0、EL1和EL2,只支持non-secure state;

(2)EL0、EL1和EL3,只支持secure state;

(3)EL0、EL1,只能实现一种安全状态,secure state或non-secure state;

(4)EL0、EL1、EL2、EL3均实现

- 异常级别、运行状态、安全状态的组合方式

|

实现的异常级别 |

secure state |

EL3 |

EL2 |

EL1 |

EL0 |

|

EL0/EL1/EL2/EL3 |

Sec&non-sec |

AArch64/AArch32 |

AArch64/AArch32 |

AArch64/AArch32 |

AArch64/AArch32 |

|

AArch64 |

AArch64 |

AArch64/AArch32 |

AArch64/AArch32 |

||

|

AArch64 |

AArch64 |

AArch64 |

AArch64/AArch32 |

||

|

AArch64 |

AArch64 |

AArch64 |

AArch64 |

||

|

AArch32 |

AArch32 |

AArch32 |

AArch32 |

||

|

EL0/EL1 /EL3 |

Sec&non-sec |

AArch64 |

\\ |

AArch64/AArch32 |

AArch64/AArch32 |

|

AArch64 |

\\ |

AArch64 |

AArch64/AArch32 |

||

|

AArch64 |

\\ |

AArch64 |

AArch64 |

||

|

AArch32 |

\\ |

AArch32 |

AArch32 |

||

|

EL0/EL1/EL2 |

Non-sec only |

\\ |

AArch64 |

AArch64/AArch32 |

AArch64/AArch32 |

|

\\ |

AArch64 |

AArch64 |

AArch64 |

||

|

EL0/EL1 |

Sec or non-sec |

\\ |

\\ |

AArch64 |

AArch64/AArch32 |

|

\\ |

\\ |

AArch64 |

AArch64 |

||

|

\\ |

\\ |

AArch32 |

AArch32 |

- 五类经典组合图示(EL0/EL1/EL2/EL3都实现)

- 如果没有实现全部4个异常级别的影响

(1)中断不会路由到这些异常级别;

(2)没有异常通过陷阱进入这些异常级别;

(3)所有从低异常级别通过系统调用切换到未实现的异常级别被作为未定义处理;

(4)不支持从未实现异常级别做地址转换

(5)任何要通过异常返回到未实现的异常级别被视为非法的异常返回

(6)任何和未实现异常级别相关的寄存器都被视为RES0(具有切换到低异常级别功能的相关寄存器除外)

9.参考文档

[1] DDI0487A_k_armv8_arm_iss10775.pdf

以上是关于ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型- 其它的主要内容,如果未能解决你的问题,请参考以下文章

ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型- 异常

ARMV8 datasheet学习笔记4:AArch64系统级体系结构之系统级存储模型

ARMV8 datasheet学习笔记4:AArch64系统级体系结构之Generic timer

ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型- 其它