基于FPGA 的简化UART 电路设计转载

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了基于FPGA 的简化UART 电路设计转载相关的知识,希望对你有一定的参考价值。

0 引言

随着嵌入式系统的广泛推广和应用,UART ( Universal Asynchronous Receiver Transmiller )作为一种串行数据传输方式也得到广泛的使用。UART 允许在串行链路上进行全双工通信。串行外设到RS 232-C 异步串行接口一般采用专用的集成电路即UART 实现。常见的串行接口芯片如8250 、8251 、NS16450 等,能够实现比较全面的串行通信功能。而在实际应用中,我们往往并不需要如此完整的功能,从而会造成资源的浪费和成本的提高。随着EDA 技术的飞速发展,我们就可以根据自己的需求,将所需要的UART 功能集成到FPGA 内部,从而简化了电路、减小了体积、提高了系统的可靠性。基于这种思想,作者在设计中选用Altera 公司的EP1C12Q240CQ8,使用Verilog HDL 设计实现UART 的核心功能。1 UART 通信原理 串行通信分为两种类型:同步通信方式和异步通行方式。UART 是通用异步发送器,是一种串行异步通信方式。它是各种设备之间进行通信的关键模块,允许在串行链路上进行全双工的通信。在发送端,并行的数字信号需要转化成串行信号才能通过有线或无线传输到另外一台设备;而在接收端,串行信号必须要被恢复成并行信号才能进行数据处理。UART 就是用来处理这种数据与串口之间的串并和并串转换的。

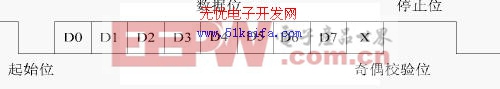

UART 传送一个字符以起始位(Start Bit) 开始,以停止位(Stop Bit )结束,字符之间没有固定的时间间隔要求。每一个字符的前面都有一个起始位(低电平),字符本身由5~8 位数据位组成,然后是一位校验位(可选),最后是停止位(1 位,1 位半或2 位),停止位后面是不定长度的空闲位。停止位和空闲位都规定高电平,这样就可以保证起始位开始处有一个下降沿。

图1 数据传输格式

2 UART 在FPGA 中的实现

2.1UART 的硬件电路设计

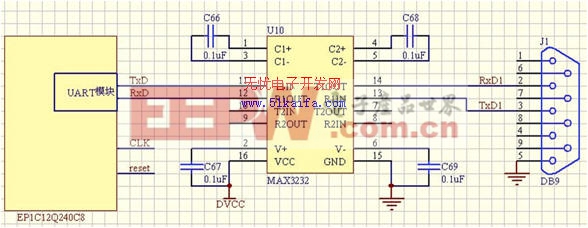

在串行通信中,普遍采用的是RS-232 接口标准。硬件电路主要由FPGA 串口模块、MAX3232 和DB-9 组成,电路图如图2 所示。数据从DB-9 的TxD 端进入,经过MAX3232 进行电平转换后由FPGA 串口模块中的RxD 端进入,进行串并转换后由数据总线进入FPGA 的其他模块。数据处理后经由数据总线进入FPGA 串口模块,在其中进行并串转换后由TxD 端输出到MAX3232 中,经电平转换后由DB-9 的RxD 端输出。

图2 UART 硬件电路图

1. 2.2 UART 的结构设计 UART 主要由波特率发生模块、发送模块、接收模块这三个部分组成。

2.2.1 波特率发生模块

当UART 在发送数据的时候,只需要按照一定的速率将数据串行地移动出就可以了。然而,当UART 在接收串行的数据时,在什么时刻将数据移入移位寄存器是非常关键的。最理想的情况是在串行数据的每一位的中间时刻,对串行数据进行采样。对每一位数据的时间进行分段,时间的分段越多,对串行数据的采样就越靠近中点,由于接收方和发送方的时钟不可能完全同步,时间的分段越多,接收方出现采样错误的概率就越低。但时间的分段越多,也意味着采样时间就越高,系统的开销就越大。因此,在实际的设计中,采用16 倍于波特率的时钟频率。UART 收发的每一个数据宽度都是波特率发生器输出的时钟周期的16 倍。如按照9600b/s 进行收发,那么波特率发生器的输出时钟频率应为9600×16Hz 。由于外部时钟采用25MHz ,可以很简单地通过总线写入不同的数值到波特率发生器保持寄存器中,然后用计数器的方式生成所需要的各种波特率。计算公式为:25000000/(16 ×所期望的波特率)-1。

2. 2.2.2 发送模块

发送模块主要实现对并行数据的缓存,并串转换,然后把串行数据按照既定数据帧格式进行输出,其机构如图3 所示:

图3 UART 发送模块

a) data_input[7:0]是8 位并行数据的输入端,转换成串行数据后从txd 输出;

b) wrn 是写控制信号,为1 时禁止数据输入,为0 时允许输入;

c) reset 为系统复位输入端,低电平有效;

d) clk 为系统时钟信号输入端,由波特率发生器产生;

e) tser 是并串转换过程的标志:在没有数据转换时保持为1,在并串转换开始时变成0,

并在转换过程中保持为0; f) tbre 是整个工作过程的标志。实验中串行数据结构为1 位起始位,8 位数据位,1 位奇偶校验位,1 位停止位。数据 的发送由外部接收模块控制,接收模块给出wrn 信号,UART 发送模块根据此信号将并行数据data-input 锁存进发送缓冲,并通过移位寄存器进行并串转换,在转换结束后加上奇偶校验位,发送到端口txd 进行串行输出。在整个工作过程中,输出信号tbre 作为标志信号,在串行数据全部输出完毕之后变成0, 并在发送模块未工作时保持为0。

2.4 接收模块

接收模块的结构如图4 所示。接收模块的作用是把收到的串行数据转换成并行数据进行输出,并判断收到数据是否有错。接收模块的内部结构及工作过程与发送模块类似,只不过接收模块的工作和发送模块的工作相反,是进行数据的串并转换。

图4 UART 接收模块

a) rxd 接收串行数据输入;

b) rdn 为输入控制端,只有rdn 为0 时,并行数据才允许输出;

c) data-ready 为数据是否准备好的标志;

d) parity-error 为校验位是否出错的标志;

e) framing-error 为帧是否出错的标志;

f) data-out[7:0]为并行数据输出端。

接收模块从捕捉到数据串的第一个0 开始工作,然后把随后依次输入的8 个数据位通过移位在寄存器中完成窜并转换,并将并行数据输出至端口data-out 。将8 个数据位移位至寄存器后,接收模块将检测输入数据串的最后一位是否为1(停止位)来判断接收到的数据帧是否出错,若不为1,就将输出framing-error 置1。

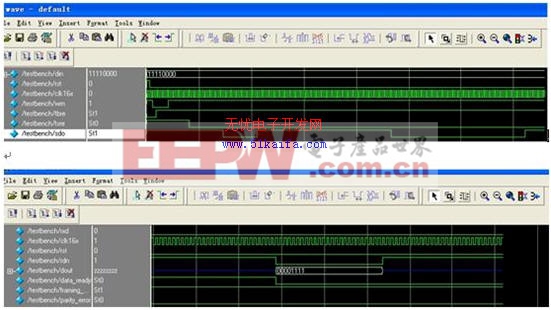

3 仿真验证在实验中,作者选用Altera 公司的Cyclone 系列产品中的EP1C12Q240C8 芯片,硬件描述语言采用Verilog HDL,用Quartus 5.1 进行逻辑综合,仿真工具则使用ModelSim6.0 。发送模块和接收模块的仿真结果分别如图5 所示。发送的数据能够严格按照串行通信协议进行传输;接收的数据也完全正确。通过仿真测试后,将程序下载到FPGA 芯片中运行,结果通信数据正确,电路工作稳定、可靠。

图5 发送和接收模块仿真

4 结束语

用FPGA 实现了UART 通信功能,可以实现对数据的接收和发送,并可以在接收 数据时对其校验位、停止位进行判断,在发送数据时可以形成完整的一帧数据格式。本 文利用FPGA 设计实现了UART 的核心功能,可以和上位机进行异步串行通信。实验 证明该UART 设计占用资源少,工作稳定可靠。

本文作者创新观点:本文对UART 系统结构进行了模块化分析,可以根据实际的需要可选择地实现相应的通信功能,简化了电路设计,提高了系统的可靠性,可以灵活地嵌入到各个通信系统当中。

以上是关于基于FPGA 的简化UART 电路设计转载的主要内容,如果未能解决你的问题,请参考以下文章