EDA课设 FPGA开发板 VHDL实现串口通信

Posted 叶庭云

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了EDA课设 FPGA开发板 VHDL实现串口通信相关的知识,希望对你有一定的参考价值。

一、设计概述

1. UART串口通信设计目的

随着 FPGA/CPLD 器件在控制领域的广泛使用,开发嵌于 FPGA/CPLD 器件内部的通用异步收发器,以实现 FPGA/CPLD 开发系统与 PC 机之间的数据通信是很有实际意义的。FPGA/CPLD与单片机、ARM等器件不同,它内部并没有集成UART,因此要实现串行通信必须要独立开发UART模块。

通用异步收发器(Universal Asynchronous Receiver/Transmitter, 简称为UART)由于具有数据通信时需要的连线少,具有相关工业标准提供的标准的接口电平规范等优点,在工业控制领域被广泛采用。近年来,FPGA器件逐渐开始广泛使用,开发基于 FPGA/CPLD 器件内部的通用异步收发器,以实现 FPGA/CPLD 开发系统与 PC 机或其它外设之间的数据通信引起了 FPGA/CPLD 领域研究人员的关注。为此,本设计基于 FPGA 器件设计了符合 RS232 标准的UART,实现开发板与计算机串口助手之间的收发,并能够自行调节波特率。

2. UART串口通信设计目的

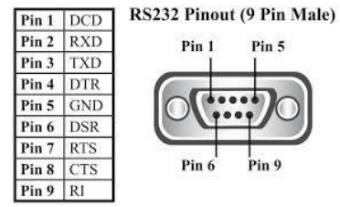

通用异步收发传输器(Universal Asynchronous Receiver/Transmitter,UART)是一种异步收发传输器,其在数据发送时将并行数据转换成串行数据来传输,在数据接收时将接收到的串行数据转换成并行数据,可以实现全双工传输和接收。它包括了 RS232、RS449、RS423、RS422 和 RS485 等接口标准规范和总线标准规范。换句话说,UART是异步串行通信的总称。而 RS232、RS449、RS423、RS422 和 RS485 等,是对应各种异步串行通信口的接口标准和总线标准,它们规定了通信口的电气特性、传输速率、连接特性和接口的机械特性等内容。RS-232是美国电子工业联盟(EIA)制定的串行数据通信的接口标准,原始编号全称是 EIA-RS-232(简称232,RS-232),被广泛用于计算机串行接口外设连接。其 DB9 接口的针脚定义如下图所示。

引脚功能如下表所示。若系统存在多个 UART 接口,则可分别称为 COM1、COM2 等。

UART通信使用前需要做多项设置,常见的设置包括数据位数、波特率大小、奇偶校验类型和停止位数。数据位(Data bits):该参数定义单个UART数据传输在开始到停止期间发送的数据位数。可选择为:5、6、7或者8(默认)。波特率(Baud):是指从一设备发送到另一设备的波特率,即每秒钟可以通信的数据比特个数。典型的波特率有4800、9600、19200、38400、57600、115200等。一般通信两端设备都要设为相同的波特率,但有些设备也可设置为自动检测波特率。

奇偶校验类型(Parity Type):是用来验证数据的正确性。奇偶校验一般不使用,如果使用,则既可以做奇校验(Odd)也可以做偶校验(Even)。在偶校验中,因为奇偶校验位会被相应的置1或0(一般是最高位或最低位),所以数据会被改变以使得所有传送的数位(含字符的各数位和校验位)中“1”的个数为偶数;在奇校验中,所有传送的数位(含字符的各数位和校验位)中“1”的个数为奇数。奇偶校验可以用于接受方检查传输是否发送生错误,如果某一字节中“1”的个数发生了错误,那么这个字节在传输中一定有错误发生。如果奇偶校验是正确的,那么要么没有发生错误,要么发生了偶数个的错误。如果用户选择数据长度为8位,则因为没有多余的比特可被用来作为奇偶校验位,因此就叫做“无奇偶校验”。

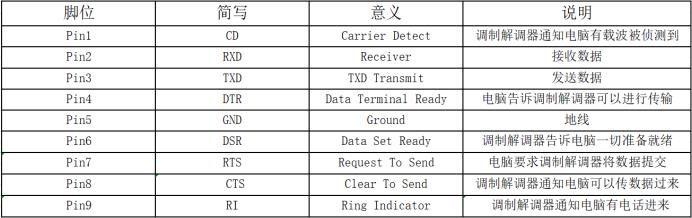

停止位(Stop bits):在每个字节的数据位发送完成之后,发送停止位,来标志着一次数据传输完成,同时用来帮助接收信号方硬件重同步。可选择为:1(默认)、1.5或者2位。在 RS-232 标准中,最常用的配置是8N1(即八个数据位、无奇偶校验、一个停止位),其发送一个字节时序图如下图所示。

空闲状态为一个高电平,按照一个完整的字节包括一位起始位、8位数据位、一位停止位即总共十位数据来算,要想完整地实现这十位数据的发送,就需要 11 个波特率时钟脉冲,第 1 个高电平脉冲标记一次传输的开始,第 11 个高电平脉冲标记一次传输的结束。

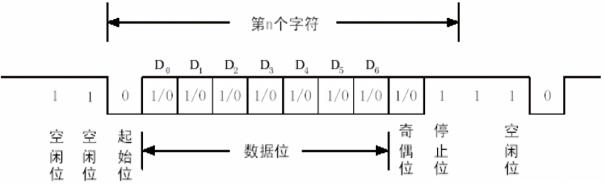

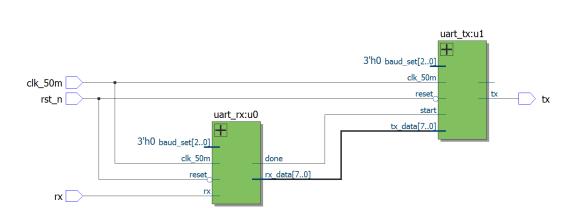

二、顶层设计

在 FPGA 内部实现串口接收与串口发送模块,串口接收模块接收上位机发送的数据,然后通过串口发送模块将数据发回上位机,实现串口数据环回。系统框图如下图所示:

如上图所示,为串口通信的顶层设计原理图。

三、子模块设计

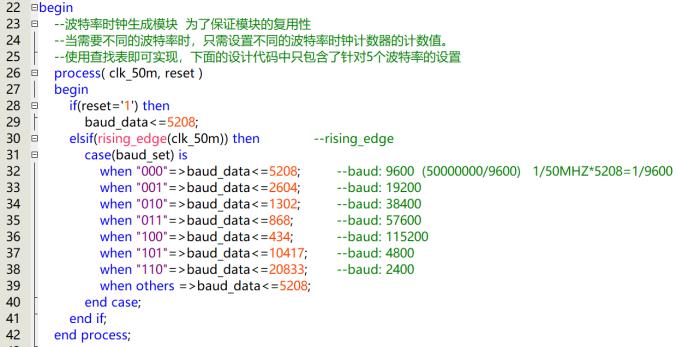

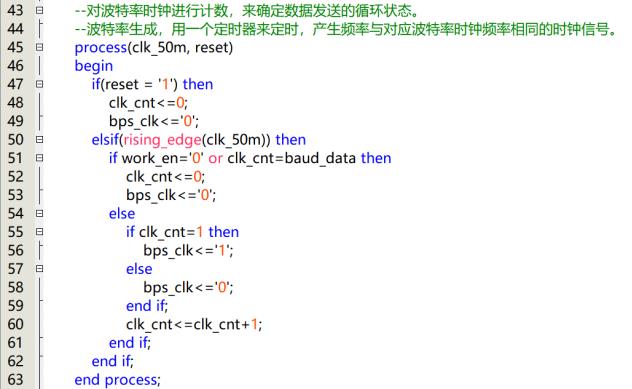

1. 波特率时钟生成模块

本模块的设计是为了保证模块的复用性。当需要不同的波特率时,只需设置不同的波特率时钟计数器的计数初值,使用查找表即可实现。下面的设计代码中包含了针对 7 个波特率的设置,如需要其他波特率可根据实际使用情况自行调节。如下图所示。

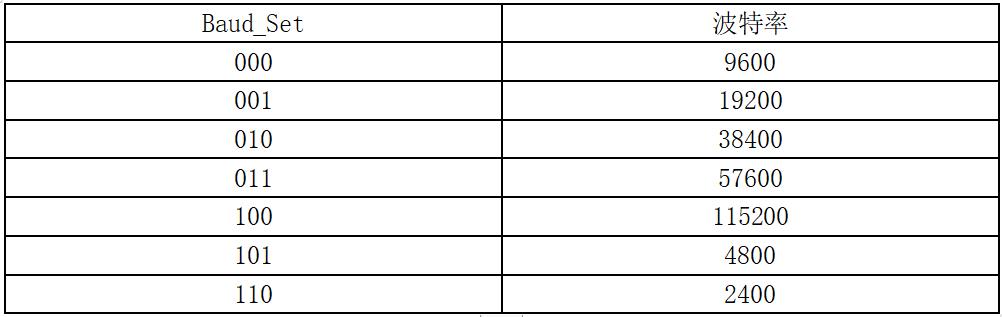

波特率生成,用一个定时器来定时,产生频率与对应波特率时钟频率相同的时钟信号,如下图所示。例如,我们使用波特率为115200bps,则我们需要产生一个频率为115200Hz的时钟信号。这里,我们首先将 115200Hz 时钟信号的周期计算出来,1秒钟为1000000000ns,因此波特率时钟的周期Tb=1000000000/115200=8680.6ns,即 115200Hz 时钟信号的一个周期为8680.6ns,那么,我们只需要设定我们的定时器定时时间为8680.6ns,每当定时时间到,产生一个系统时钟周期长度的高电平脉冲信号即可。系统时钟频率为50MHz,即周期为20ns,那么,我们只需要计数 8680/20 个系统时钟,就可获得 8680ns 的定时,bps115200=Tb×Fclk-1=Fclk115200-1。相应的,其它波特率定时值的计算与此相同。为了实现可以自行调节波特率,设计中使用了一个 3 位的波特率选择端口:Baud_Set。通过给此端口不同的值,就能选择不同的波特率,此端口控制不同波特率的原理很简单,就是一个多路选择器,多路选择器通过选择不同的定时器计数最大值来设置不同的比特率时钟频率。Baud_Set的值与各波特率的对应关系如下表所示。

2. 发送模块

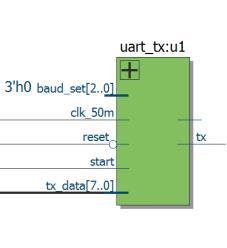

串口发送模块的整体框图,如下图所示。

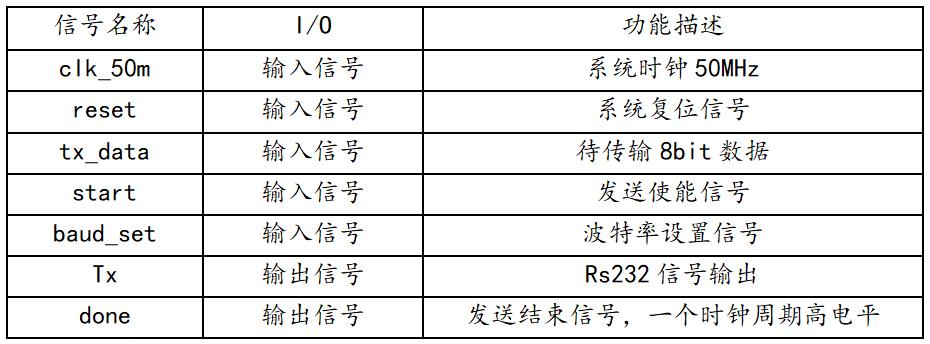

其接口列表如下表所示:

从原理部分已知,波特率是 UART 通信中需要设置的参数之一。在波特率时钟生成模块中,系统时钟周期为System_clk_period,这里为20ns。如果接入到该模块的时钟频率为其他值,需要根据具体的频率值修改该参数。

3. 数据输出模块

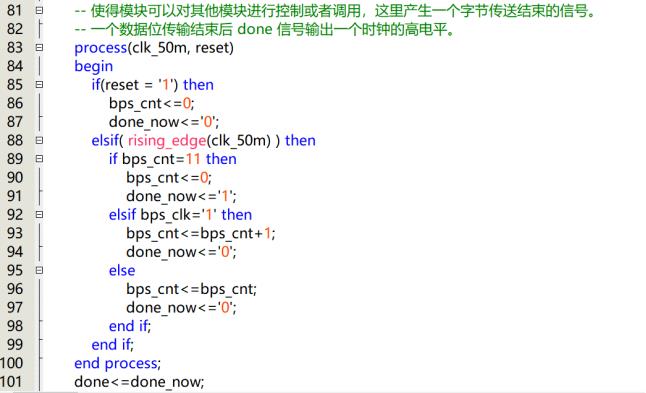

通过对波特率时钟进行计数,来确定数据发送的循环状态。为了使得模块可以对其他模块进行控制或者调用,这里产生一个 byte 传送结束的信号。一个数据位传输结束后 done 信号输出一个时钟的高电平,如下图所示。

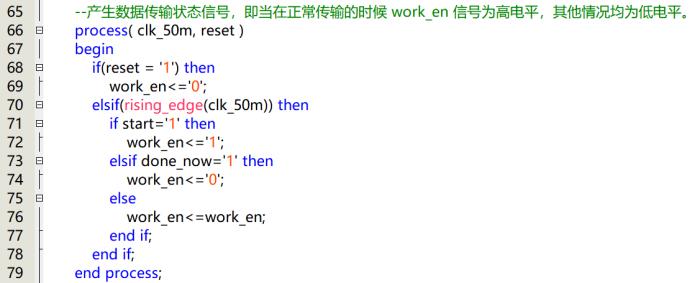

产生数据传输状态信号,如上图所示。即当在正常传输的时候 work_en 信号为高电平,其他情况均为低电平。

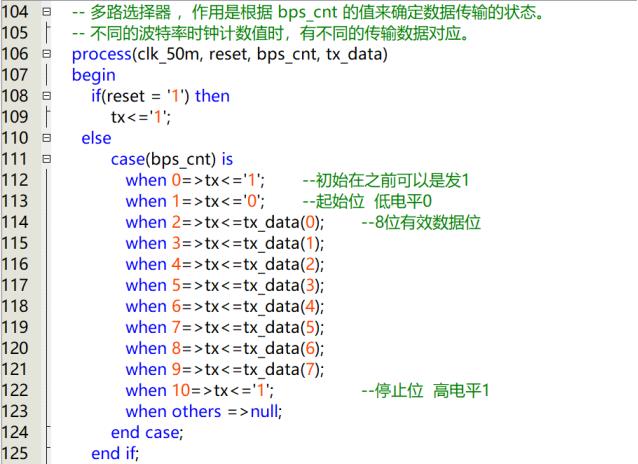

4. 数据传输状态控制模块

在模块结构图中还有一个多路选择器,作用是根据 bps_cnt 的值来确定数据传输的状态。不同的波特率时钟计数值时,有不同的传输数据对应。

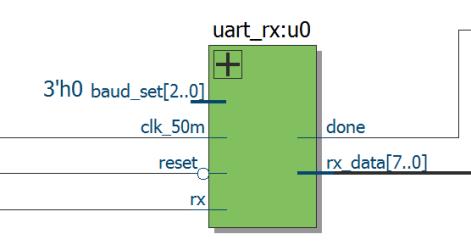

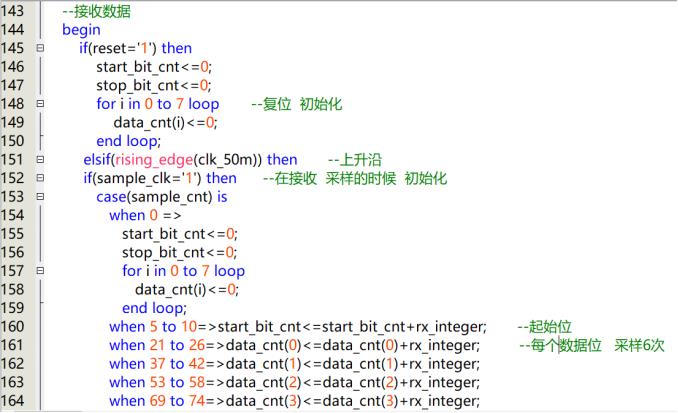

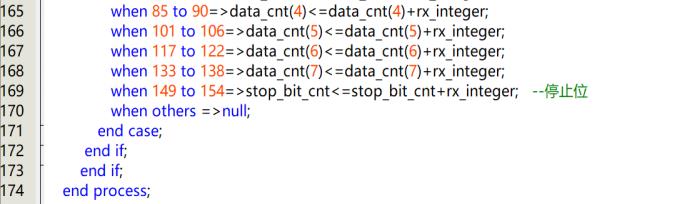

5. 接收模块

串口接收模块与串口发送模块设计思路类似。串口接收模块整体框图,如下图所示。

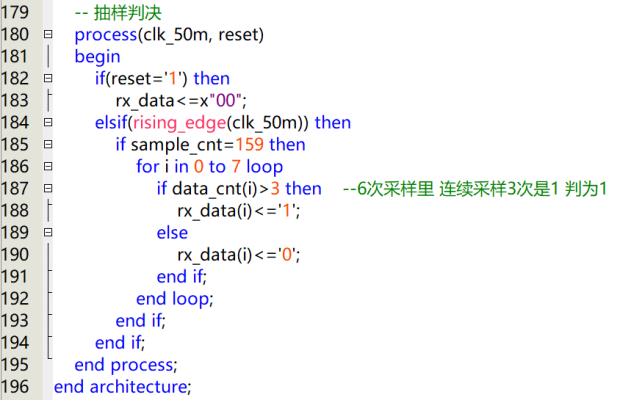

如上图所示,为接收模块的关键的 VDHL 代码。

四、系统测试

1. 仿真结果与分析

对该发送模块进行功能仿真。在仿真文件中,生成了复位信号以及使能信号、待传输数据。这里将所有数据变化与系统时钟错开1ns,是为了能更清楚看到输入输出数据与时钟的时序关系。

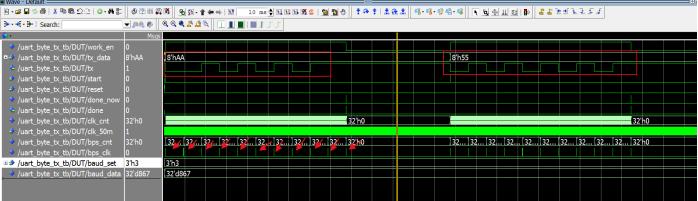

设置好仿真脚本后用ModelSim进行功能仿真,得到如图所示的波形文件,可以看出在复位信号为高电平以及使能信号有效之前输出信号Rs232_Tx均为 0,在复位结束以及使能后输出信号才开始正常,待发送数据设置为8’haa(MSB),且当开始发送后,输出信号依次为 1、0(起始位)、 8’haa(LSB)、1(停止位);当输入数据为01010101b(MSB)后,输出信号依次为 1、0(起始位)、10101010b(LSB)、1(停止位)。同时uart_state处于发送状态时为1,即仿真验证结果正确,如下图所示。

对接收模块进行功能仿真,模块输出的Tx连接到接收模块上的Rx,作为接收模块的激励。

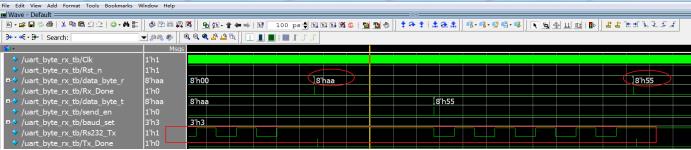

设置好仿真脚本后运行 ModelSim 进行功能仿真,得到如下图所示的波形文件。分析可知:每当一个字节发送结束后,数据输出data_byte_r均会更新输出一次,符合设计预期。

2. 管脚安排

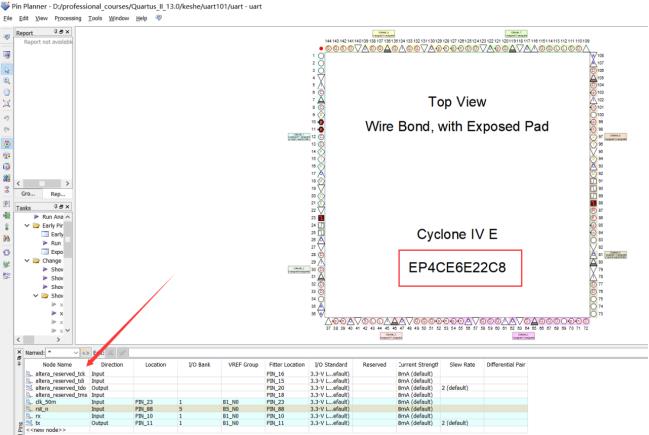

我们选用 Cyclone IV E 系列的 EP4CE6E22C8 芯片,最终的管脚安排 Pin Planner 如下图所示。

3. 下载测试

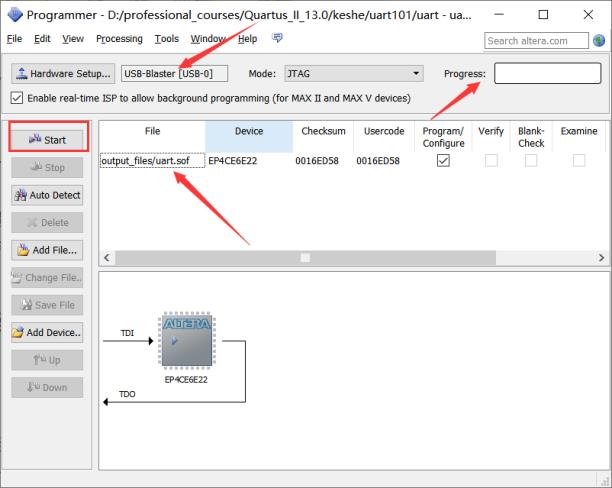

通过 USB 线缆连接 FPGA 开发板和 PC 机, Hardware Setup设置为USB-Blaster [USB-0],下载 sof 文件到 FPGA 开发板中。如下图所示。

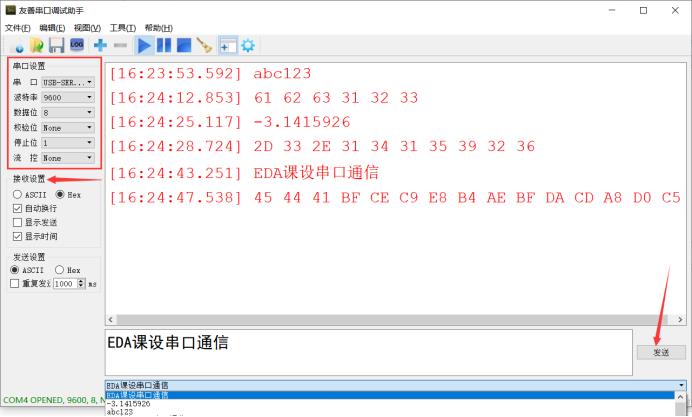

在串口助手中选择与开发板相连接的串口端口,设置波特率为9600,数据位为8,停止位为1,无校验位。通过点击“打开”按钮来打开串口。

如下图所示。串口打开后,在发送文本框中输入数据 abc123 并点击发送,可以看到串口助手中接收到了数据。在接收设置为 ASCII 时,显示abc123;在接收设置为 Hex(十六进制)时,显示61 62 63 31 32 33。分析可知接收到的数据与发送的数据一致,设计验证正确。

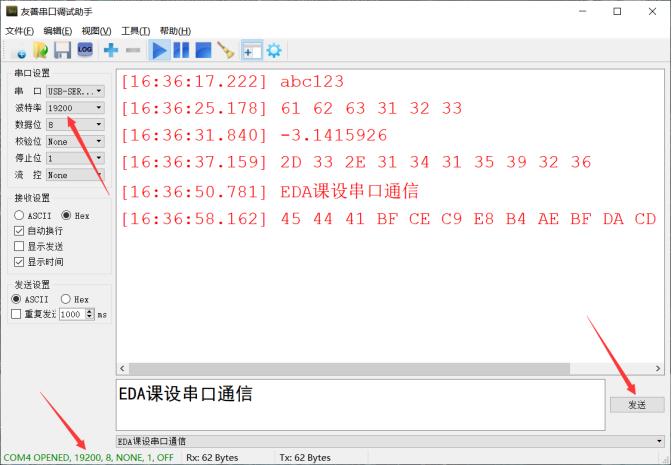

在波特率设置为 9600 时,串口调试助手中设置波特率为19200,这时发送数据,接收到的数据会有乱码。这时我们修改顶层设计的 baud_set 为001,此时对应波特率为19200,重新全编译整个项目,再下载 sof 文件到 FPGA 开发板,打开串口调试助手调试,测试结果如上图所示。分析可知,本设计实现了开发板与计算机串口助手之间数据的收发,通信格式正确,并且能自行调节波特率,符合设计预期,并且验证正确。

设计报告+源码+资料:https://download.csdn.net/download/fyfugoyfa/20691109

六、参考资料

- 黄沛昱.EDA技术与VHDL设计实验指导.西安电子科技大学出版社,2012,08.

- 杨英强.一种基于FPGA的UART电路实现[J].现代电子技术,2005,28(12):82-84.

- 郭勇.EDA技术基础(第2版)[M].机械工业出版社,2005.3.14—320.

- 褚振勇.FPGA设计及应用[M].西安:西安电子科技大学出版社.

以上是关于EDA课设 FPGA开发板 VHDL实现串口通信的主要内容,如果未能解决你的问题,请参考以下文章