ZYNQ之FPGA学习----UART串口实验

Posted 鲁棒最小二乘支持向量机

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ZYNQ之FPGA学习----UART串口实验相关的知识,希望对你有一定的参考价值。

1 UART串口简介

UART串口基础知识学习:硬件设计基础----通信协议UART

2 实验任务

上位机通过串口调试助手发送数据给 Zynq,Zynq PL 端通过 RS232 串口接收数据并将接收到的数据发送给上位机,完成串口数据环回,管脚分配如下:

图片来自《领航者ZYNQ之FPGA开发指南》

3 实验设计

3.1 创建工程

新建工程,操作如图所示:

输入工程名字和工程路径,如图:

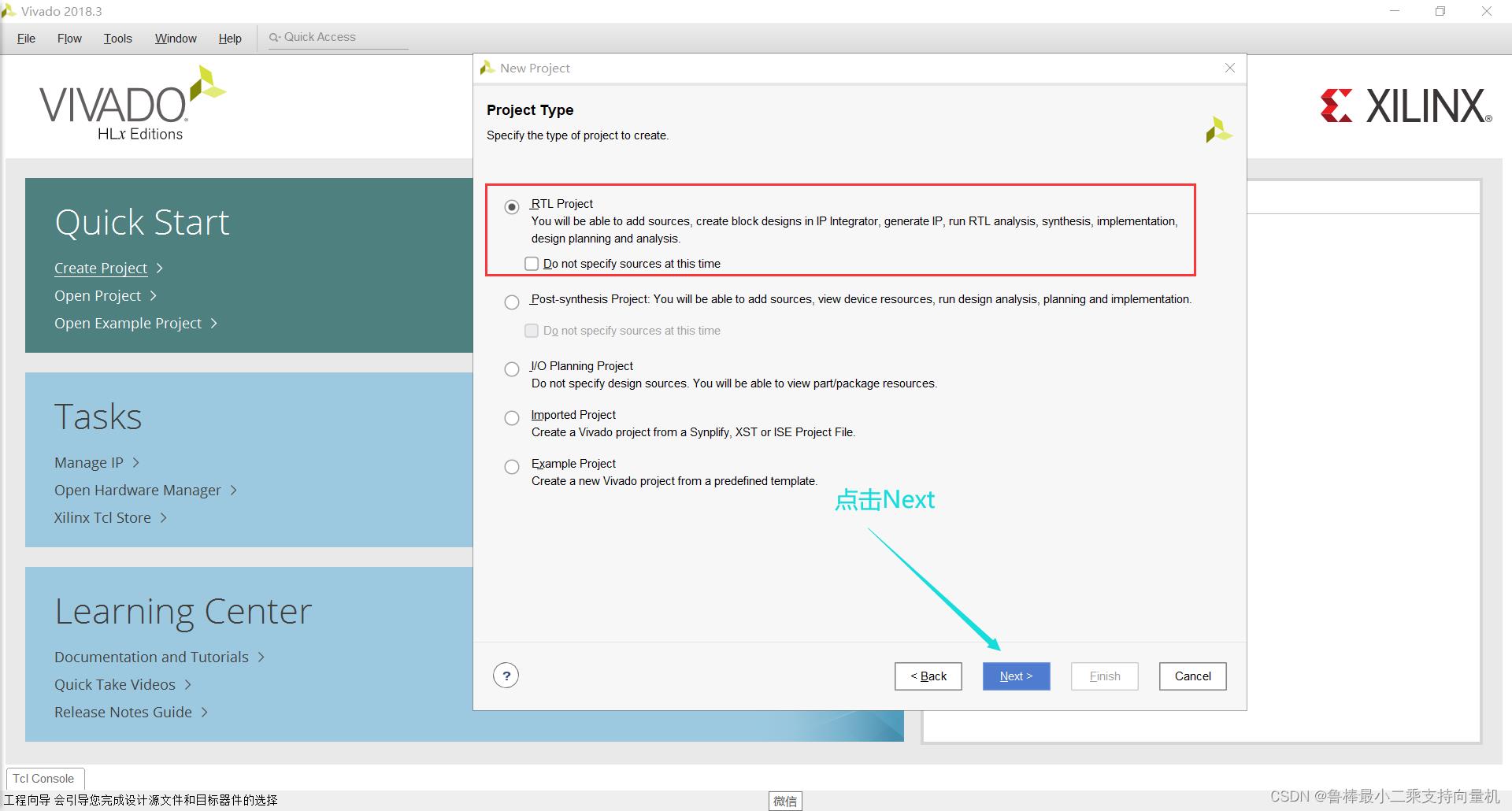

选择创建RTL工程,如图:

直接点击Next:

继续点击Next:

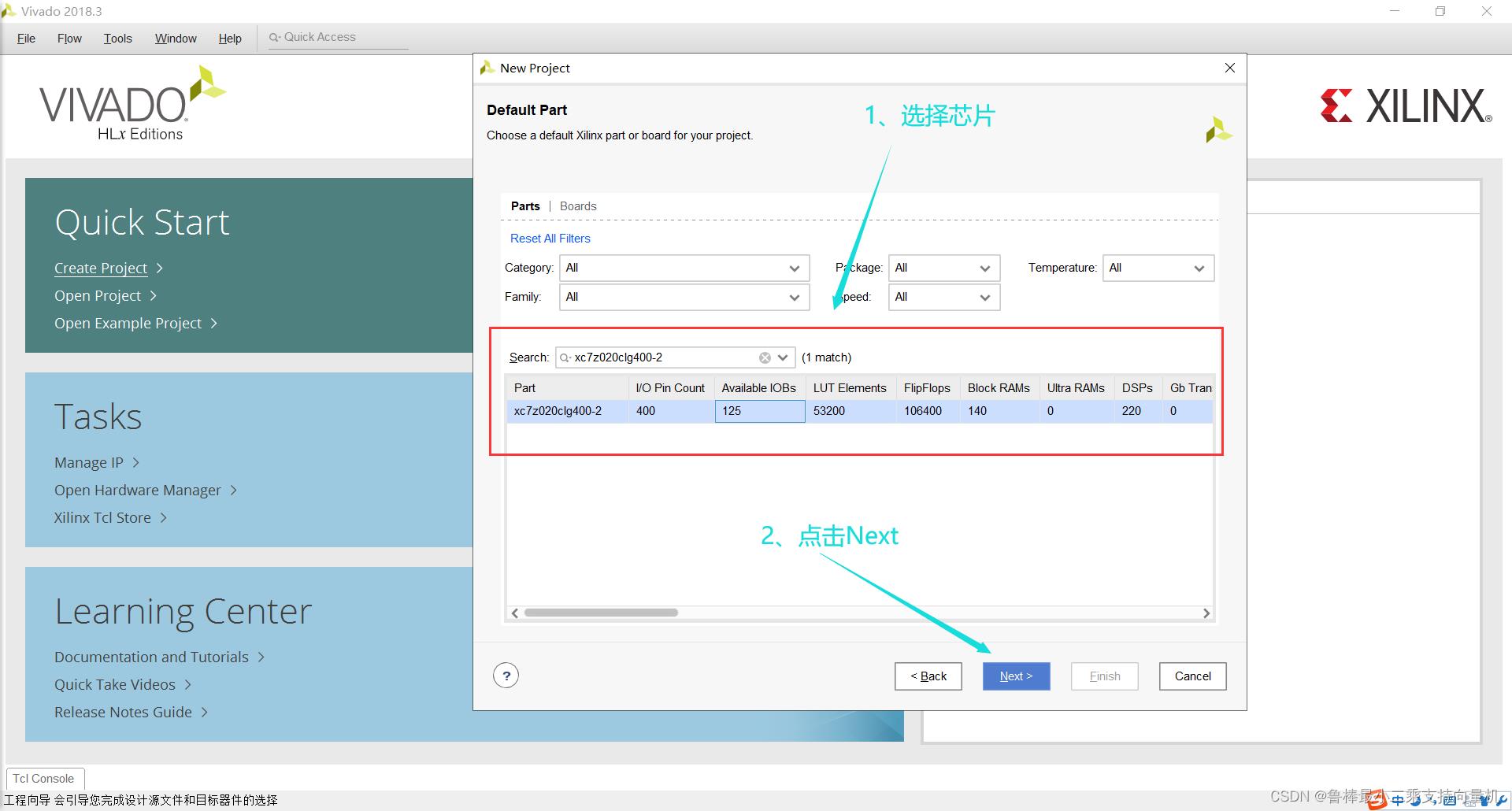

添加芯片型号,操作如图:

完成工程创建:

3.2 设计输入

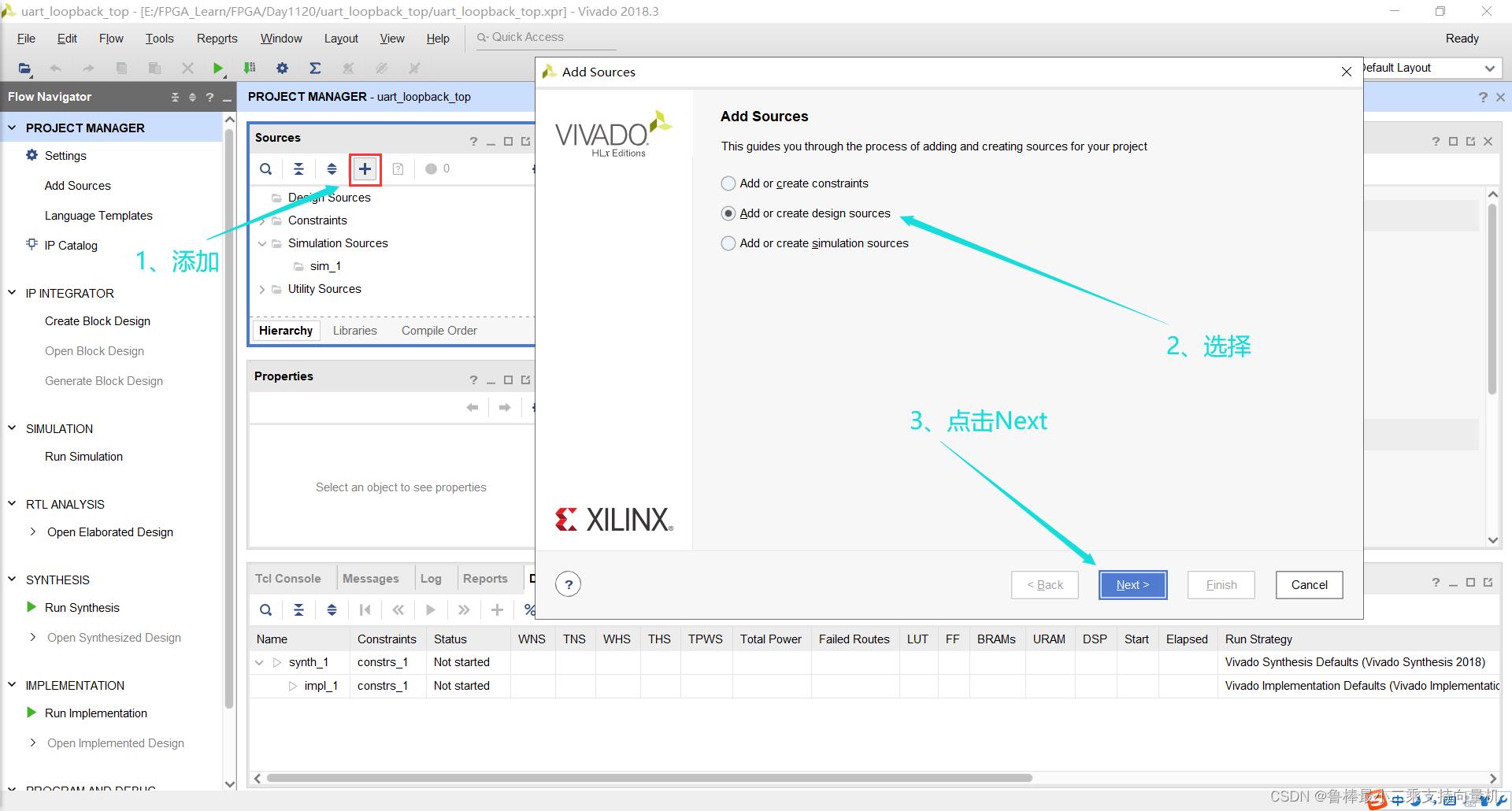

创建工程顶层文件,操作如图:

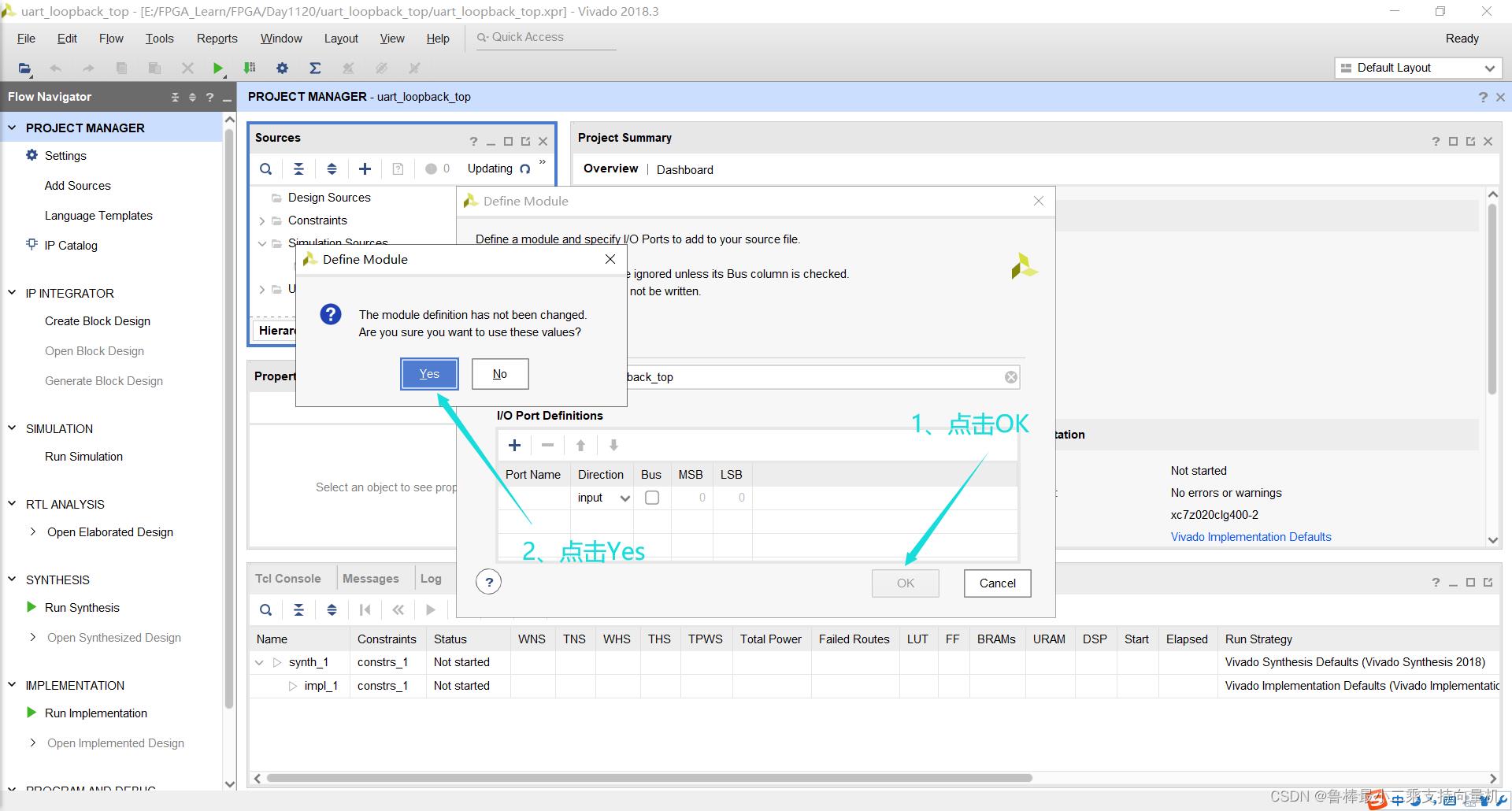

创建uart_loopback_top顶层模块:

创建完成:

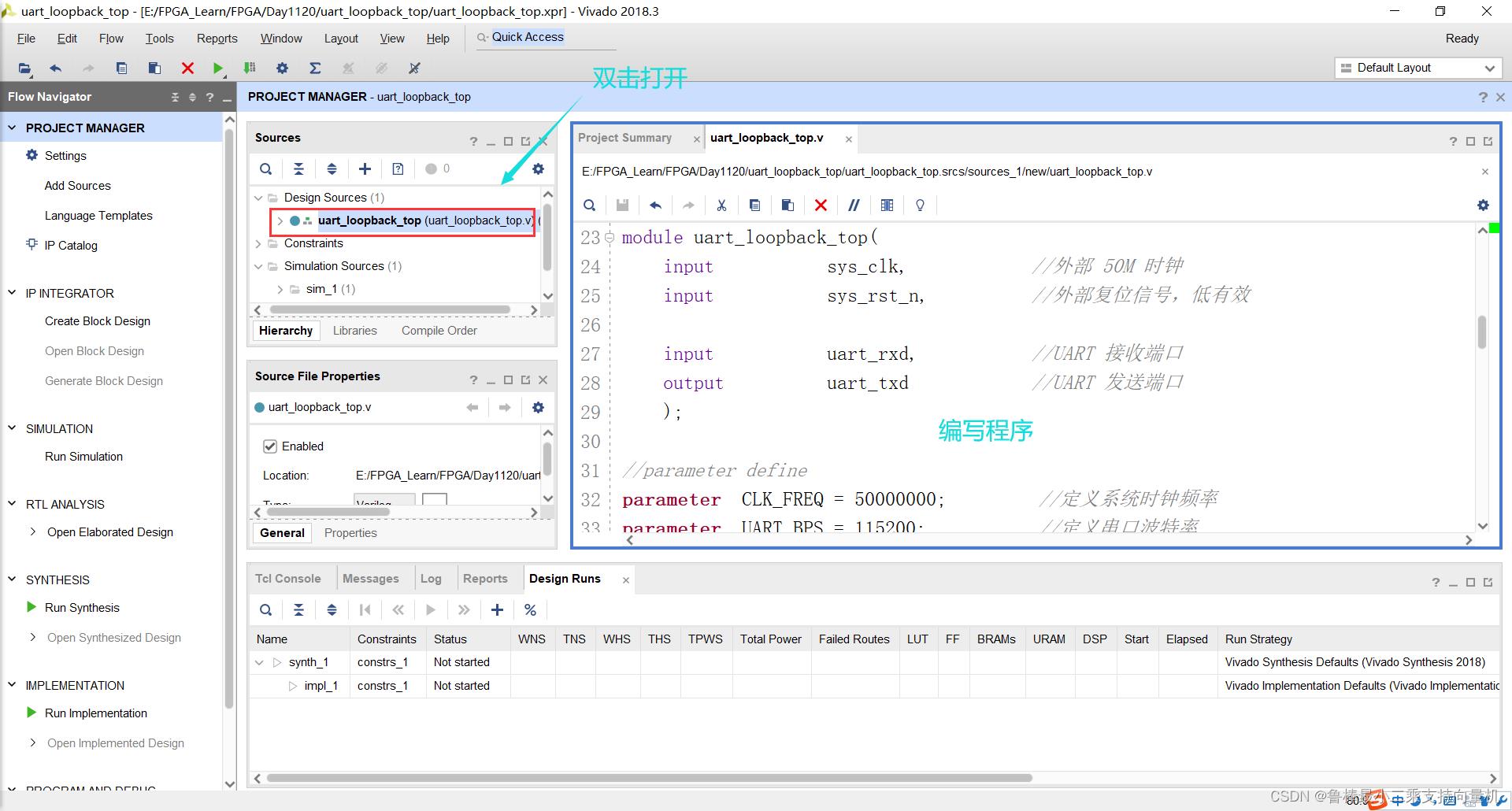

双击打开,输入代码如下:

module uart_loopback_top(

input sys_clk, //外部 50M 时钟

input sys_rst_n, //外部复位信号,低有效

input uart_rxd, //UART 接收端口

output uart_txd //UART 发送端口

);

//parameter define

parameter CLK_FREQ = 50000000; //定义系统时钟频率

parameter UART_BPS = 115200; //定义串口波特率

//wire define

wire uart_recv_done; //UART 接收完成

wire [7:0] uart_recv_data; //UART 接收数据

wire uart_send_en; //UART 发送使能

wire [7:0] uart_send_data; //UART 发送数据

wire uart_tx_busy; //UART 发送忙状态标志

//串口接收模块

uart_recv #(

.CLK_FREQ (CLK_FREQ ), //设置系统时钟频率

.UART_BPS (UART_BPS )) //设置串口接收波特率

u_uart_recv(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.uart_rxd (uart_rxd ),

.uart_done (uart_recv_done ),

.uart_data (uart_recv_data)

);

//串口发送模块

uart_send #(

.CLK_FREQ (CLK_FREQ ), //设置系统时钟频率

.UART_BPS (UART_BPS )) //设置串口发送波特率

u_uart_send(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.uart_en (uart_send_en ),

.uart_din (uart_send_data ),

.uart_tx_busy (uart_tx_busy ),

.uart_txd (uart_txd)

);

//串口环回模块

uart_loop u_uart_loop(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.recv_done (uart_recv_done ), //接收一帧数据完成标志信号

.recv_data (uart_recv_data ), //接收的数据

.tx_busy (uart_tx_busy ), //发送忙状态标志

.send_en (uart_send_en ), //发送使能信号

.send_data (uart_send_data) //待发送数据

);

endmodule

如图所示:

创建uart_recv文件,如图:

双击打开,输入代码:

module uart_recv(

input sys_clk, //系统时钟

input sys_rst_n, //系统复位,低电平有效

input uart_rxd, //UART 接收端口

output reg uart_done, //接收一帧数据完成标志

output reg [7:0] uart_data //接收的数据

);

//parameter define

parameter CLK_FREQ = 50000000; //系统时钟频率

parameter UART_BPS = 9600; //串口波特率

localparam BPS_CNT = CLK_FREQ/UART_BPS; //为得到指定波特率,

//需要对系统时钟计数 BPS_CNT 次

//reg define

reg uart_rxd_d0;

reg uart_rxd_d1;

reg [15:0] clk_cnt; //系统时钟计数器

reg [ 3:0] rx_cnt; //接收数据计数器

reg rx_flag; //接收过程标志信号

reg [ 7:0] rxdata; //接收数据寄存器

//wire define

wire start_flag;

//捕获接收端口下降沿(起始位),得到一个时钟周期的脉冲信号

assign start_flag = uart_rxd_d1 & (~uart_rxd_d0 );

//对 UART 接收端口的数据延迟两个时钟周期

always @( posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

uart_rxd_d0 <= 1'b0;

uart_rxd_d1 <= 1'b0;

end

else begin

uart_rxd_d0 <= uart_rxd;

uart_rxd_d1 <= uart_rxd_d0;

end

end

//当脉冲信号 start_flag 到达时,进入接收过程

always @( posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

rx_flag <= 1'b0;

else begin

if(start_flag) //检测到起始位

rx_flag <= 1'b1; //进入接收过程,标志位 rx_flag 拉高

//计数到停止位中间时,停止接收过程

else if ((rx_cnt == 4'd9) && (clk_cnt == BPS_CNT/2 ))

rx_flag <= 1'b0; //接收过程结束,标志位 rx_flag 拉低

else

rx_flag <= rx_flag;

end

end

//进入接收过程后,启动系统时钟计数器

always @( posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

clk_cnt <= 16'd0;

else if ( rx_flag ) begin //处于接收过程

if (clk_cnt < BPS_CNT - 1)

clk_cnt <= clk_cnt + 1'b1;

else

clk_cnt <= 16'd0; //对系统时钟计数达一个波特率周期后清零

end

else

clk_cnt <= 16'd0; //接收过程结束,计数器清零

end

//进入接收过程后,启动接收数据计数器

always @( posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

rx_cnt <= 4'd0;

else if ( rx_flag ) begin //处于接收过程

if (clk_cnt == BPS_CNT - 1) //对系统时钟计数达一个波特率周期

rx_cnt <= rx_cnt + 1'b1; //此时接收数据计数器加 1

else

rx_cnt <= rx_cnt;

end

else

rx_cnt <= 4'd0; //接收过程结束,计数器清零

end

//根据接收数据计数器来寄存 uart 接收端口数据

always @( posedge sys_clk or negedge sys_rst_n) begin

if ( !sys_rst_n)

rxdata <= 8'd0;

else if(rx_flag) //系统处于接收过程

if (clk_cnt == BPS_CNT/2) begin //判断系统时钟计数器计数到数据位中间

case ( rx_cnt )

4'd1 : rxdata[0] <= uart_rxd_d1; //寄存数据位最低位

4'd2 : rxdata[1] <= uart_rxd_d1;

4'd3 : rxdata[2] <= uart_rxd_d1;

4'd4 : rxdata[3] <= uart_rxd_d1;

4'd5 : rxdata[4] <= uart_rxd_d1;

4'd6 : rxdata[5] <= uart_rxd_d1;

4'd7 : rxdata[6] <= uart_rxd_d1;

4'd8 : rxdata[7] <= uart_rxd_d1; //寄存数据位最高位

default :;

endcase

end

else

rxdata <= rxdata;

else

rxdata <= 8'd0;

end

//数据接收完毕后给出标志信号并寄存输出接收到的数据

always @( posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

uart_data <= 8'd0;

uart_done <= 1'b0;

end

else if(rx_cnt == 4'd9) begin //接收数据计数器计数到停止位时

uart_data <= rxdata; //寄存输出接收到的数据

uart_done <= 1'b1; //并将接收完成标志位拉高

end

else begin

uart_data <= 8'd0;

uart_done <= 1'b0;

end

end

endmodule

如图所示:

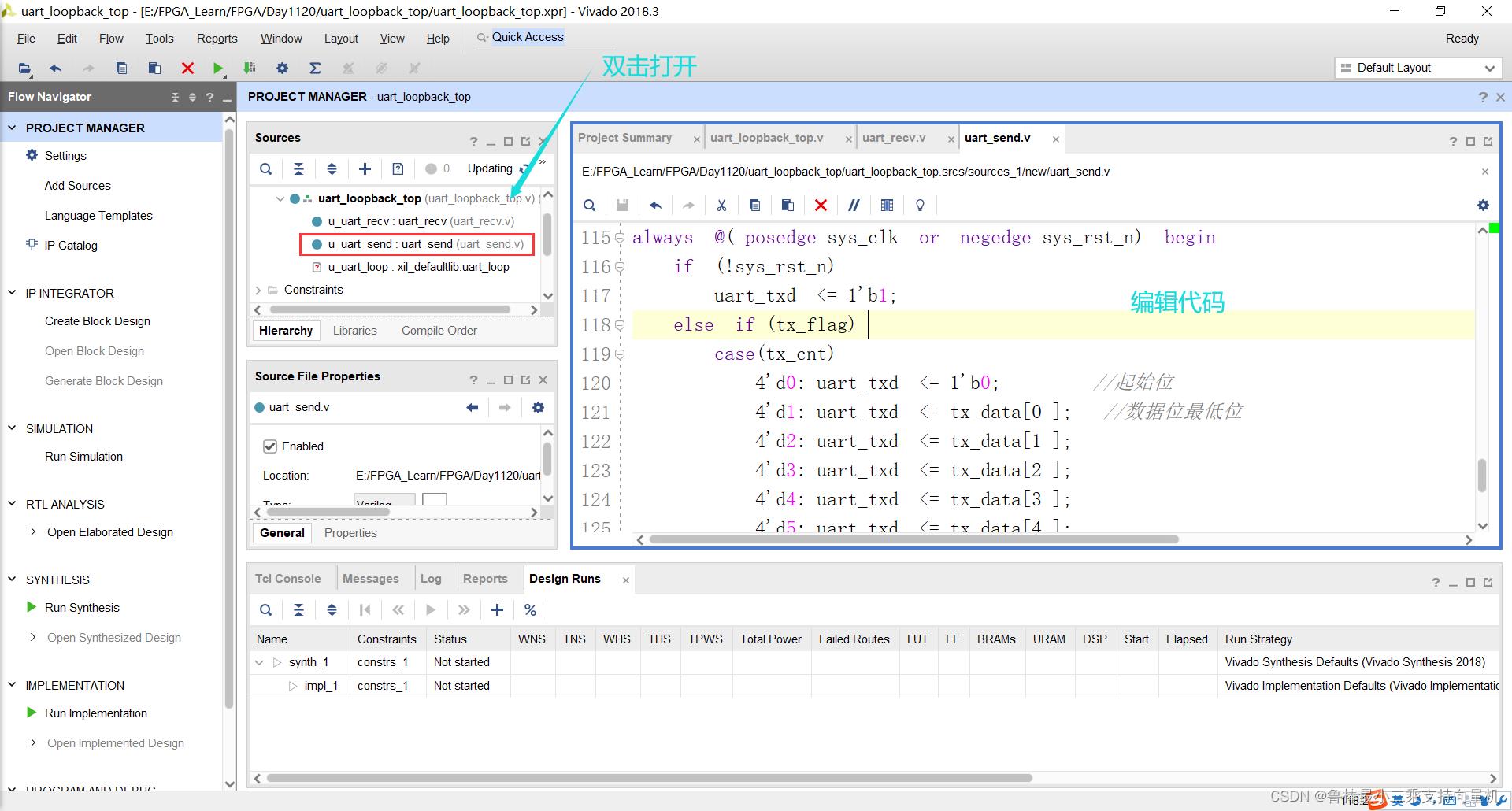

创建uart_send文件,如图所示:

双击打开文件,输入代码:

module uart_send(

input sys_clk, //系统时钟

input sys_rst_n, //系统复位,低电平有效

input uart_en, //发送使能信号

input [7:0] uart_din, //待发送数据

output uart_tx_busy, //发送忙状态标志

output reg uart_txd //UART 发送端口

);

//parameter define

parameter CLK_FREQ = 50000000; //系统时钟频率

parameter UART_BPS = 9600; //串口波特率

localparam BPS_CNT = CLK_FREQ/UART_BPS; //为得到指定波特率,对系统时钟计数 BPS_CNT 次

//reg define

reg uart_en_d0;

reg uart_en_d1;

reg [15:0] clk_cnt; //系统时钟计数器

reg [ 3:0] tx_cnt; //发送数据计数器

reg tx_flag; //发送过程标志信号

reg [ 7:0] tx_data; //寄存发送数据

//wire define

wire en_flag;

assign uart_tx_busy = tx_flag;

//捕获 uart_en 上升沿,得到一个时钟周期的脉冲信号

assign en_flag = (~uart_en_d1) & uart_en_d0;

//对发送使能信号 uart_en 延迟两个时钟周期

always @( posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

uart_en_d0 <= 1'b0;

uart_en_d1 <= 1'b0;

end

else begin

uart_en_d0 <= uart_en;

uart_en_d1 <= uart_en_d0;

end

end

//当脉冲信号 en_flag 到达时,寄存待发送的数据,并进入发送过程

always @( posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

tx_flag <= 1'b0;

tx_data <= 8'd0;

end

else if (en_flag) begin //检测到发送使能上升沿

tx_flag <= 1'b1; //进入发送过程,标志位 tx_flag 拉高

tx_data <= uart_din; //寄存待发送的数据

end

//计数到停止位结束时,停止发送过程

else if ((tx_cnt == 4'd9) && (clk_cnt == BPS_CNT -(BPS_CNT/16) )) begin

tx_flag <= 1'b0; //发送过程结束,标志位 tx_flag 拉低

tx_data <= 8'd0;

end

else begin

tx_flag <= tx_flag;

tx_data <= tx_data;

end

end

//进入发送过程后,启动系统时钟计数器

always @( posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

clk_cnt <= 16'd0;

else if (tx_flag) begin //处于发送过程

if (clk_cnt < BPS_CNT - 1)

clk_cnt <= clk_cnt + 1'b1;

else

clk_cnt <= 16'd0; //对系统时钟计数达一个波特率周期后清零

end

else

clk_cnt <= 16'd0; //发送过程结束

end

//进入发送过程后,启动发送数据计数器

always @( posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

tx_cnt <= 4'd0;

else if (tx_flag) begin //处于发送过程

if (clk_cnt == BPS_CNT - 1) //对系统时钟计数达一个波特率周期

tx_cnt <= tx_cnt + 1'b1; //此时发送数据计数器加 1

else

tx_cnt <= tx_cnt;

end

else

tx_cnt <= 4'd0; //发送过程结束

end

//根据发送数据计数器来给 uart 发送端口赋值

always @( posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

uart_txd <= 1'b1;

else if (tx_flag)

case(tx_cnt)

4'd0: uart_txd <= 1'b0; //起始位

4'd1: uart_txd <= tx_data[0 ]; //数据位最低位

4'd2: uart_txd <= tx_data[1 ];

4'd3: uart_txd <= tx_data[2 ];

4'd4: uart_txd <= tx_data[3 ];

4'd5: uart_txd <= tx_data[4 ];

4'd6: uart_txd <= tx_data[5 ];

4'd7: uart_txd <= tx_data[6 ];

4'd8: uart_txd <= tx_data[7 ]; //数据位最高位

4'd9: uart_txd <= 1'b1; //停止位

default: ;

endcase

else

uart_txd <= 1'b1; //空闲时发送端口为高电平

end

endmodule

如图所示:

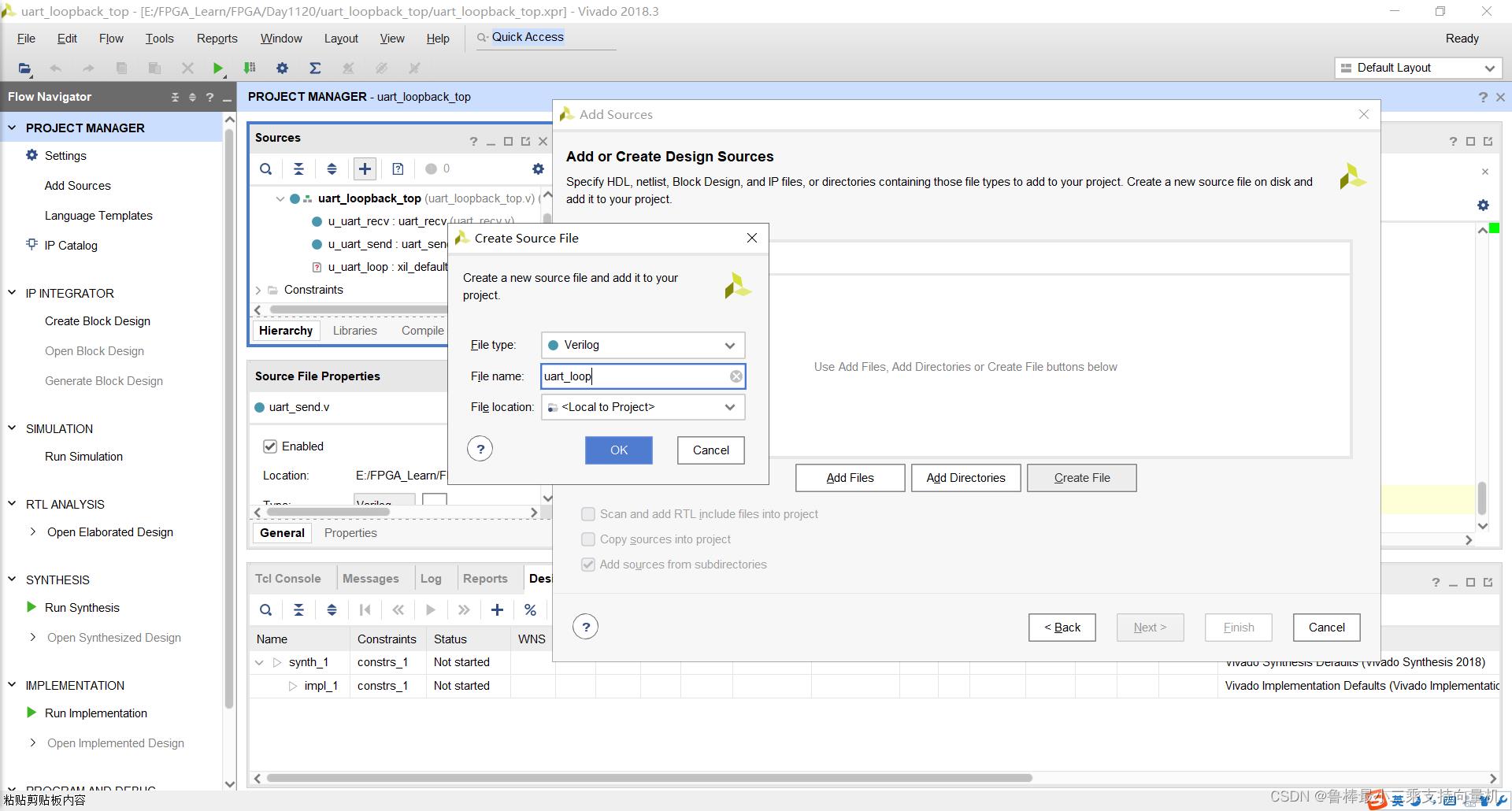

创建uart_loop文件,如图所示:

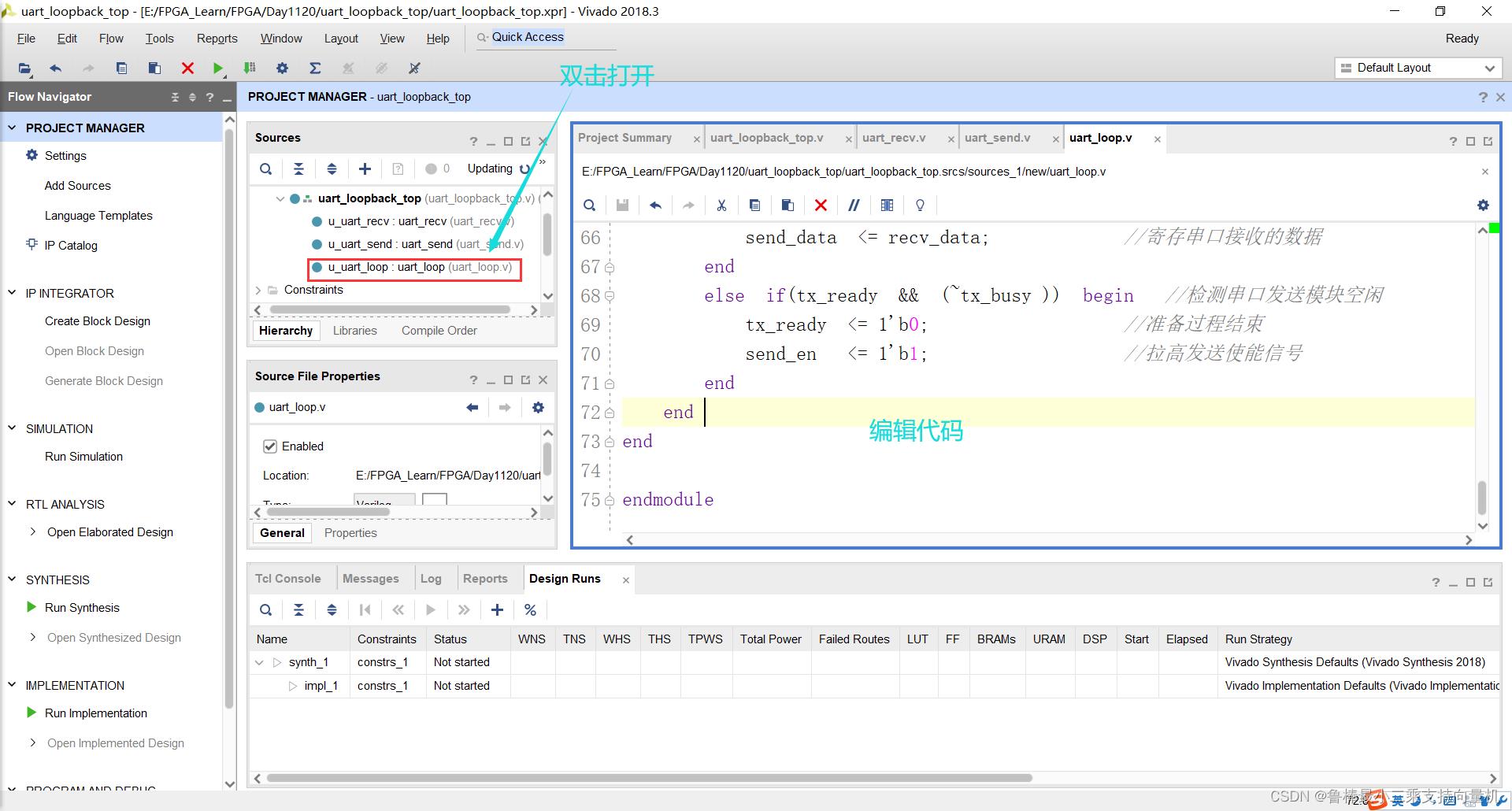

双击打开,输入代码:

module uart_loop(

input sys_clk, //系统时钟

input sys_rst_n, //系统复位,低电平有效

input recv_done, //接收一帧数据完成标志

input [7:0] recv_data, //接收的数据

input tx_busy, //发送忙状态标志

output reg send_en, //发送使能信号

output reg [7:0] send_data //待发送数据

);

reg recv_done_d0;

reg recv_done_d1;

reg tx_ready;

wire recv_done_flag;

//捕获 recv_done 上升沿,得到一个时钟周期的脉冲信号

assign recv_done_flag = (~recv_done_d1) & recv_done_d0;

//对发送使能信号 recv_done 延迟两个时钟周期

always @( posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

recv_done_d0 <= 1'b0;

recv_done_d1 <= 1'b0;

end

else begin

recv_done_d0 <= recv_done;

recv_done_d1 <= recv_done_d0;

end

end

//判断接收完成信号,并在串口发送模块空闲时给出发送使能信号

always @( posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

tx_ready <= 1'b0;

send_en <= 1'b0;

send_data <= 8'd0;

end

else begin

if(recv_done_flag) begin //检测串口接收到数据

tx_ready <= 1'b1; //准备启动发送过程

send_en <= 1'b0;

send_data <= recv_data; //寄存串口接收的数据

end

else if(tx_ready && (~tx_busy )) begin //检测串口发送模块空闲

tx_ready <= 1'b0; //准备过程结束

send_en <= 1'b1; //拉高发送使能信号

end

end

end

endmodule

如图所示:

3.3 分析与综合

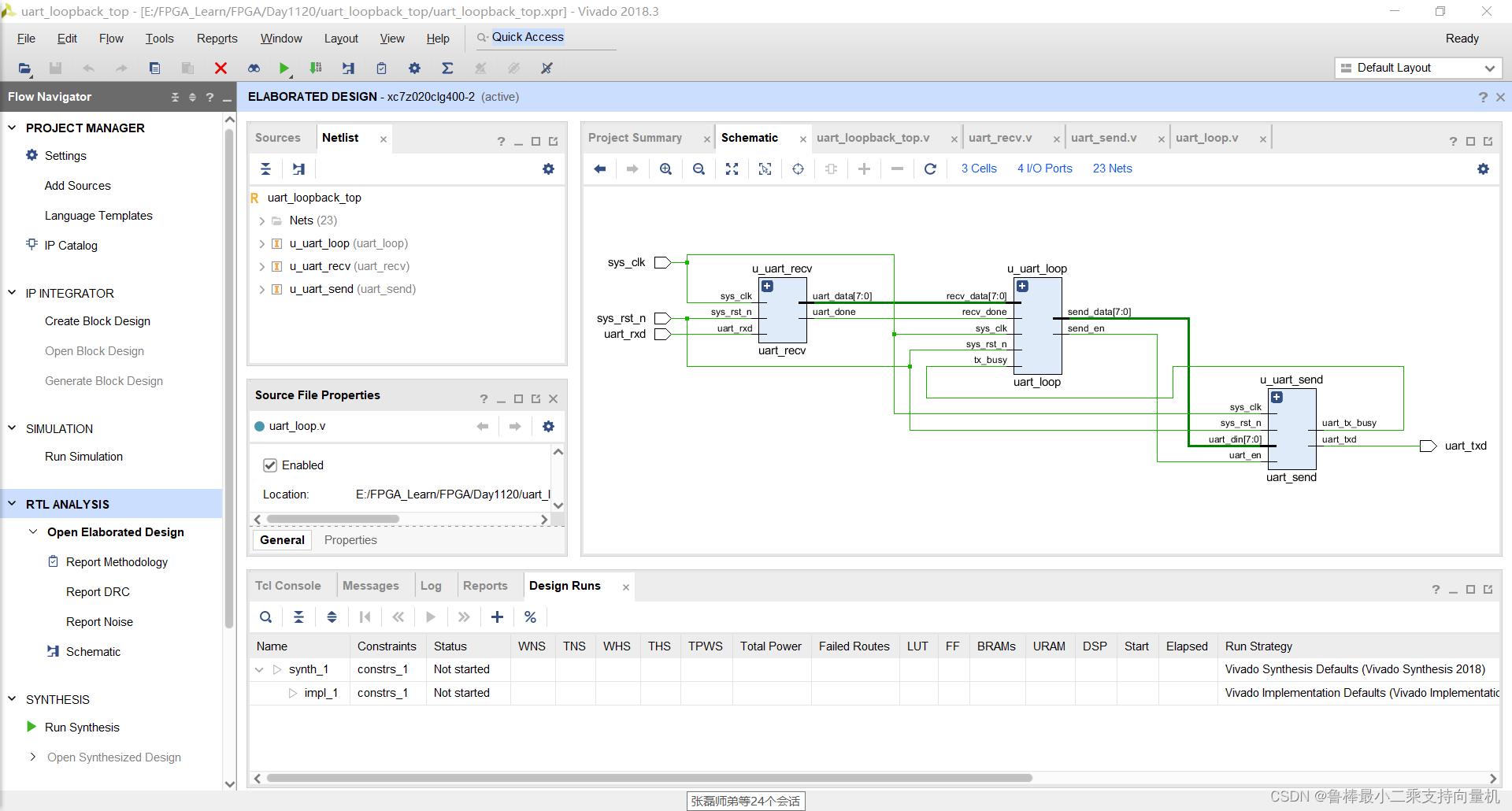

对设计进行分析,操作如图:

分析后的设计,Vivado自动生成顶层原理图,如图:

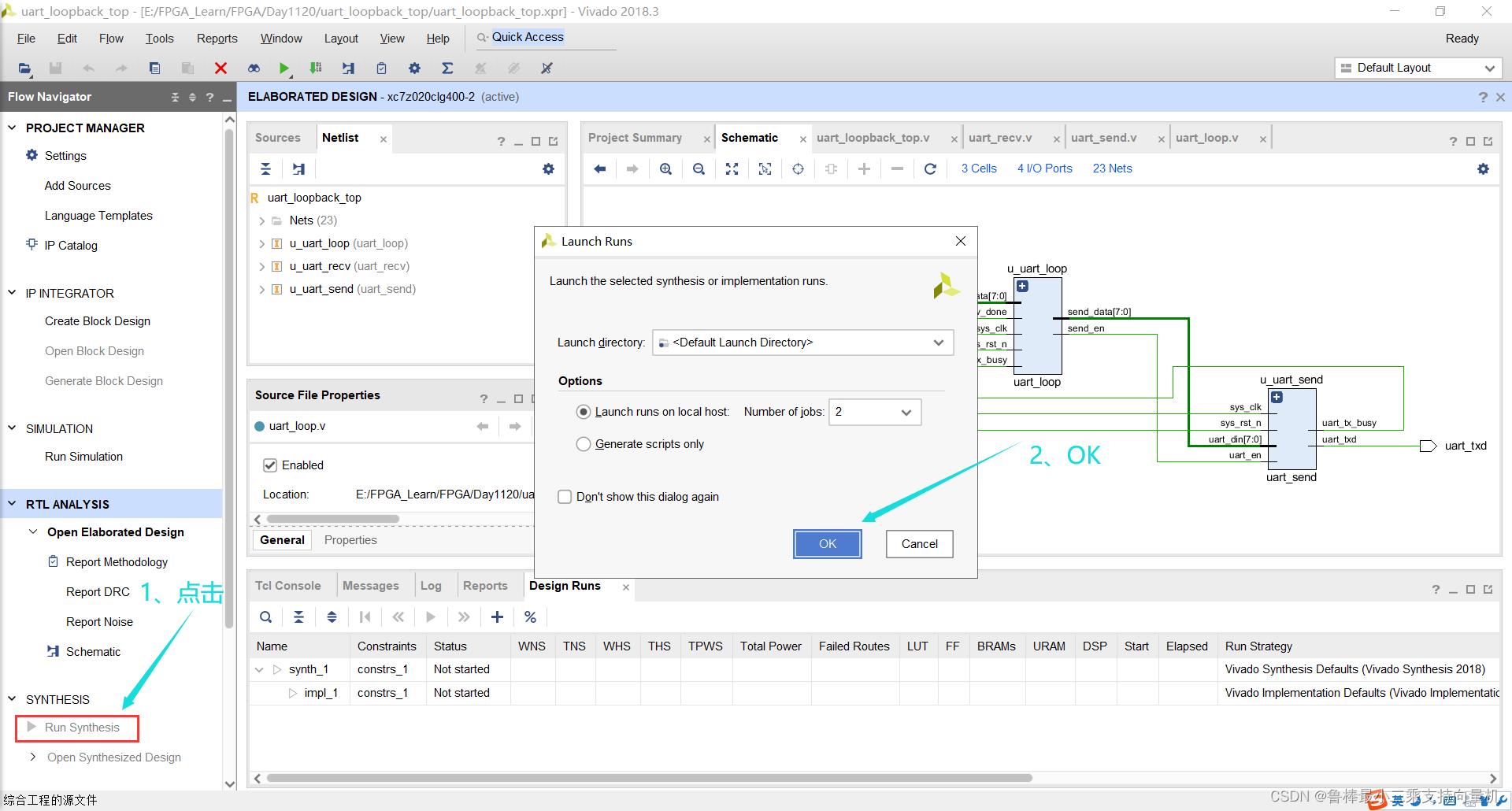

对设计进行综合,操作如图:

综合完成后,弹出窗口如下,直接关闭:

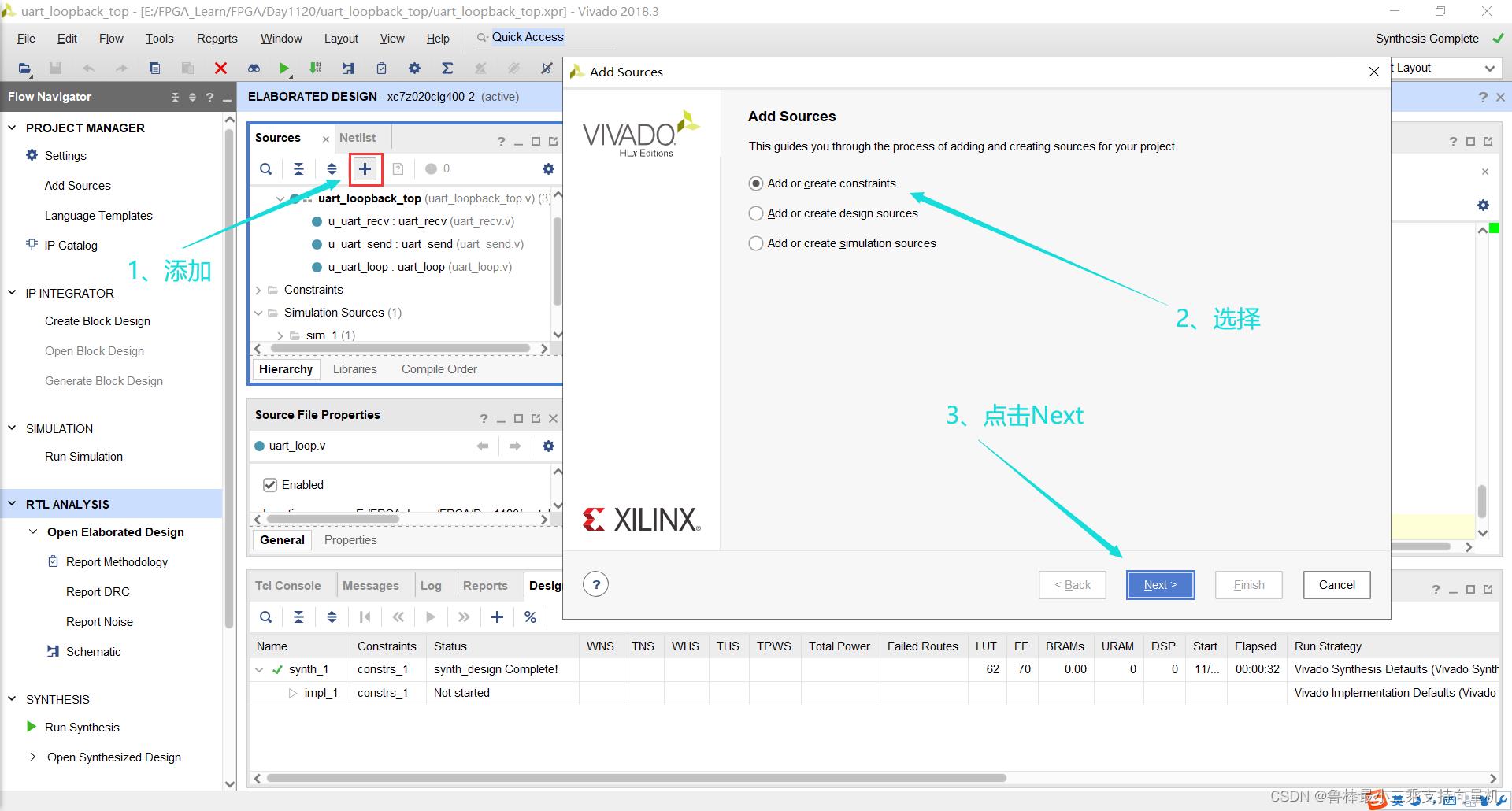

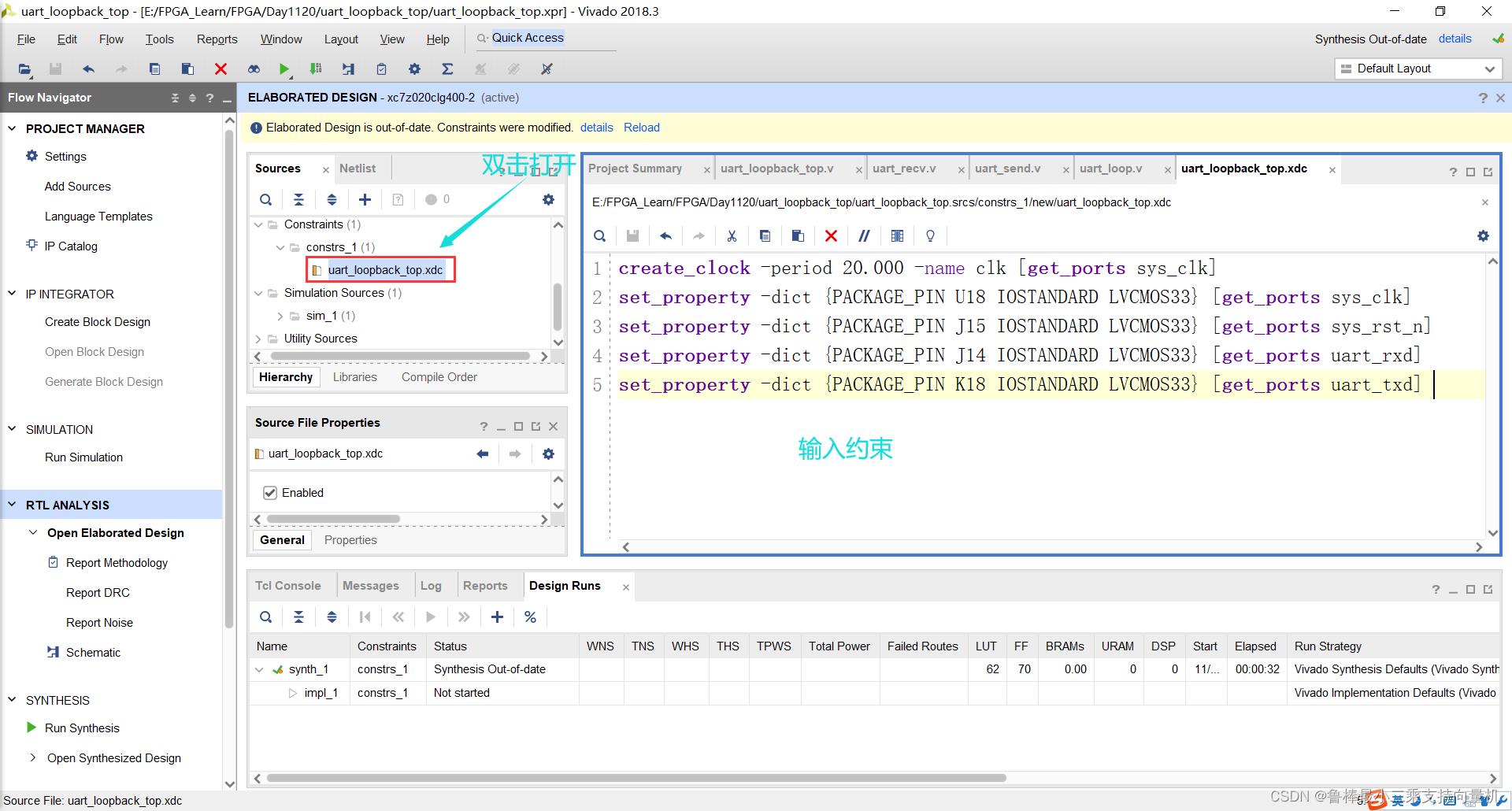

3.4 约束输入

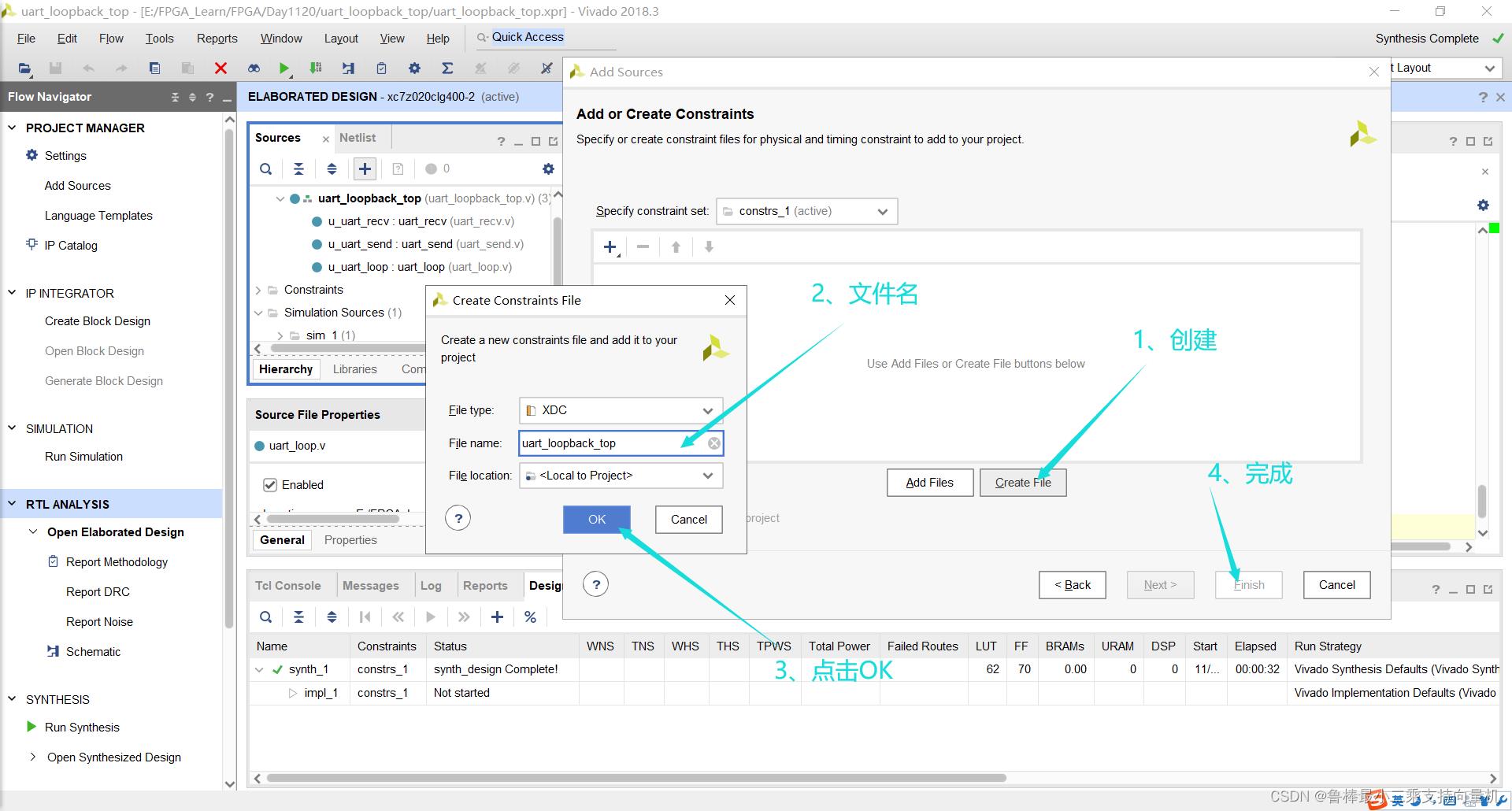

创建约束文件,操作如图所示:

创建约束文件,输入文件名:

双击打开,输入约束代码:

create_clock -period 20.000 -name clk [get_ports sys_clk]

set_property -dict PACKAGE_PIN U18 iosTANDARD LVCMOS33 [get_ports sys_clk]

set_property -dict PACKAGE_PIN J15 IOSTANDARD LVCMOS33 [get_ports sys_rst_n]

set_property -dict PACKAGE_PIN J14 IOSTANDARD LVCMOS33 [get_ports uart_rxd]

set_property -dict PACKAGE_PIN K18 IOSTANDARD LVCMOS33 [get_ports uart_txd]

如图所示:

3.5 设计实现

点击 Flow Navigator 窗口中的 Run Implementation,如图所示:

点击OK:

完成后,直接关闭:

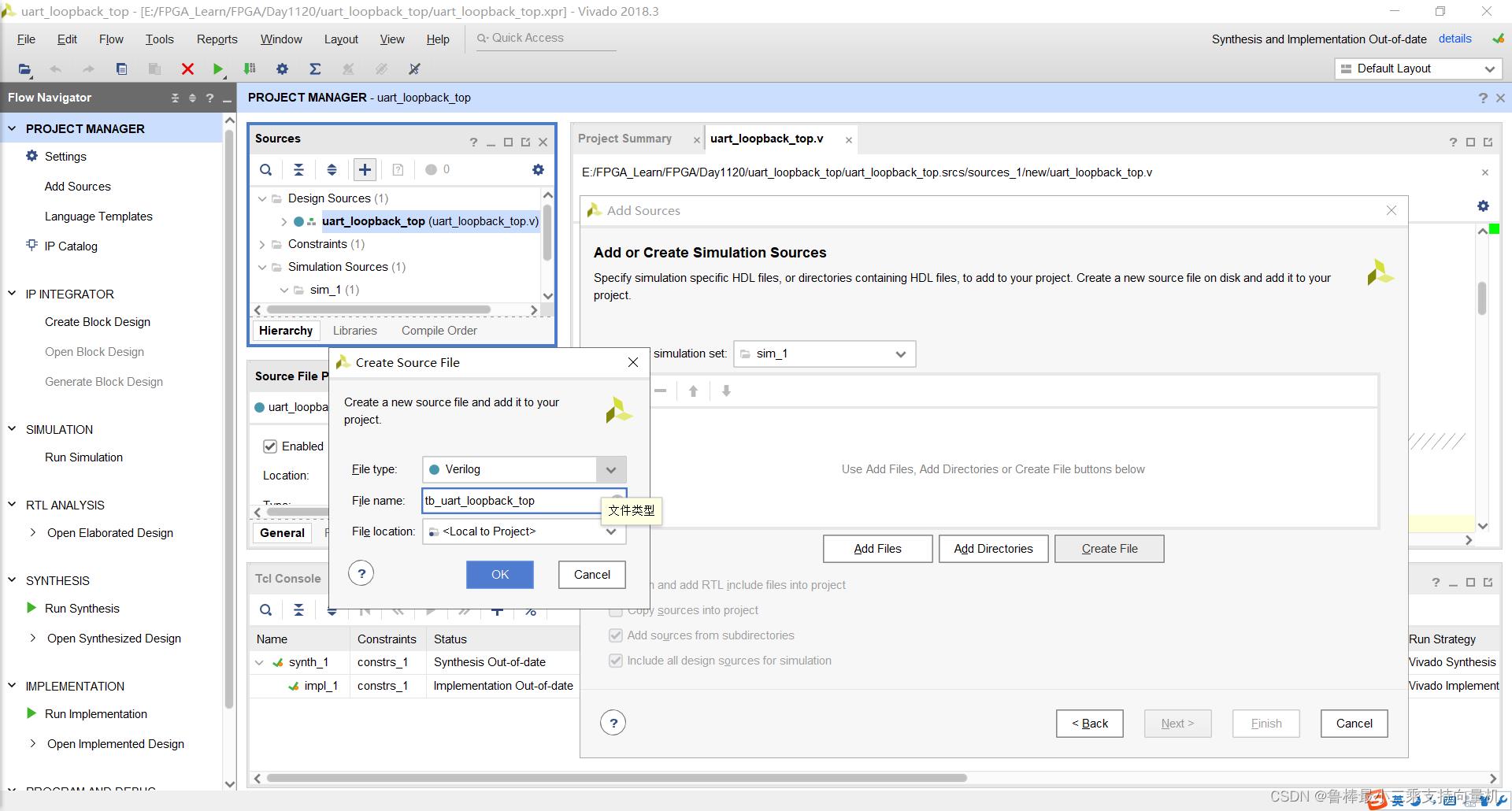

3.6 功能仿真

创建TestBench,操作如图所示:

创建激励文件,输入文件名:

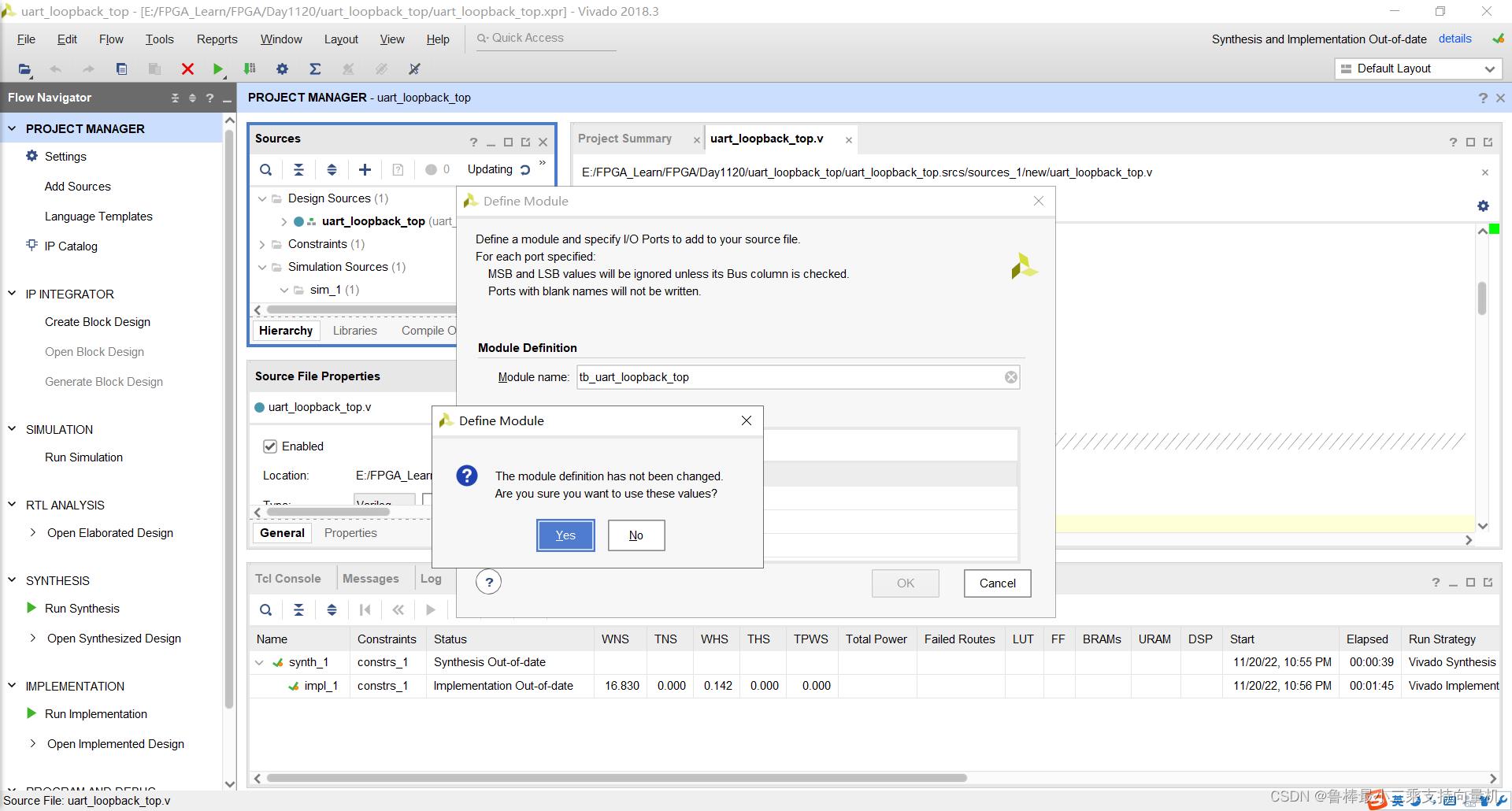

创建完成:

双击打开,输入TestBench(激励)代码:

`timescale 1ns / 1ps

module tb_uart_loopback_top();

reg sys_clk;

reg sys_rst_n;

reg uart_rxd;

wire uart_txd;

parameter SYS_CLK = 50; //系统时钟频率,单位Mhz

parameter SYS_PRE = 1000/(SYS_CLK*2); //时钟周期,单位ns

parameter UART_BPS = 115200; //串口波特率

parameter BPS_CNT = 1_000_000_000/UART_BPS;//用于串口仿真的时延

//初始时刻定义

initial begin

$timeformat(-9, 0, " ns", 10); //定义时间显示格式

sys_clk = 1'b0;

sys_rst_n = 1'b0;

uart_rxd <= 1'b1;

#200 //系统开始工作

sys_rst_n = 1'b1;

#3000

rx_byte($random % 256); //生成8位随机数1

rx_byte($random % 256); //生成8位随机数2

rx_byte($random % 256); //生成8位随机数3

rx_byte($random % 256); //生成8位随机数4

rx_byte($random % 256); //生成8位随机数5

rx_byte($random % 256); //生成8位随机数6

rx_byte($random % 256); //生成8位随机数7

rx_byte($random % 256); //生成8位随机数8

#600

$finish();

end

//定义任务,每次发送的数据10 位(起始位1+数据位8+停止位1)

task rx_byte(

input [7:0] data

);

integer i; //定义一个常量

//用 for 循环产生一帧数据,for 括号中最后执行的内容只能写 i=i+1

for(i=0; i<10; i=i+1) begin

case(i)

ZYNQ之FPGA学习----EEPROM读写测试实验