SPI 协议的理解

Posted SimonLiang

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了SPI 协议的理解相关的知识,希望对你有一定的参考价值。

一、SPI介绍

1.1技术性能:

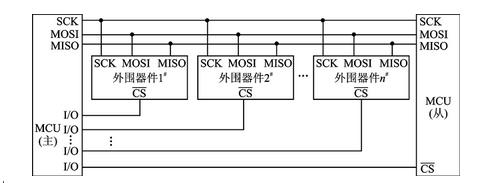

采用主从模式,一般仅支持单Master--多Slave。时钟由Master控制,在时钟移位脉冲下,数据按位传输,高位在前--底位在后(MSB first)。接口有两条单向数据线,为全双工通信。

各半导体公司推出了大量的带有SPI接口的具有各种各样功能的芯片,如RAM,EEPROM,FlashROM,A/D转换器、D/A转换器、LED/LED显示驱动器、I/O接口芯片、实时时钟、UART收发器

1.2接口定义:

SPI接口共有4根信号线,分别是:设备选择线、时钟线、串行输出数据线、串行输入数据线。

- MOSI :主设备数据输入,从设备数据输出

- MOSO :主设备数据输出,从设备数据输入

- SCLK:时钟信号,由主设备产生

- CSS:从设备使能信号,有主设备控制

1.3时钟极性和时钟相位

1.3.1时钟极性和时钟相位的基本介绍

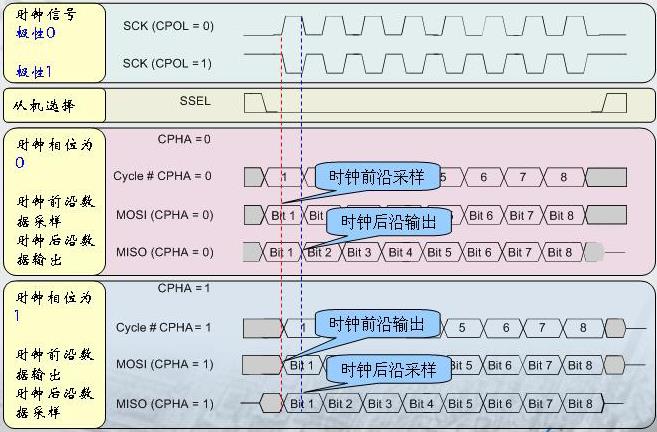

在SPI操作中,最重要的两项设置就是时钟极性(CPOL或UCCKPL)和时钟相位(CPHA或UCCKPH)。

时钟极性设置时钟空闲时的电平,时钟相位设置读取数据和发送数据的时钟沿。时钟极性(CPOL)对传输协议没有重大的影响,时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

CPOL=0,串行同步时钟的空闲状态为低电平;CPOL=1,串行同步时钟的空闲状态为高电平。 CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

1.3.2时序详解

我们来关注SCK的第一个时钟周期,在时钟的前沿采样数据(上升沿,第一个时钟沿),在时钟的后沿输出数据(下降沿,第二个时钟沿)。首先来看主器件,主器件的输出口(MOSI)输出的数据bit1,在时钟的前沿被从器件采样,那主器件是在何时刻输出bit1的呢?bit1的输出时刻实际上在SCK信号有效以前,比SCK的上升沿还要早半个时钟周期。bit1的输出时刻与SSEL信号没有关系。再来看从器件,主器件的输入口MISO同样是在时钟的前沿采样从器件输出的bit1的,那从器件又是在何时刻输出bit1的呢。从器件是在SSEL信号有效后,立即输出bit1,尽管此时SCK信号还没有起效。

所以说,主机和从机的发送数据是同时完成的,两者的接收数据也是同时完成的。所以为了保证主从机正确通信,应使得它们的SPI具有相同的时钟极性和时钟相位。

SPI接口时钟配置心得:在主设备这边配置SPI接口时钟的时候一定要弄清楚从设备的时钟要求,因为主设备这边的时钟极性和相位都是以从设备为基准的。因此在时钟极性的配置上一定要搞清楚从设备是在时钟的上升沿还是下降沿接收数据,是在时钟的下降沿还是上升沿输出数据。

1.4单片机软件模拟SPI接口

参考一下网址: http://blog.csdn.net/ce123/article/details/6905630

二、SPI与IIC

Philips(for IIC)和Motorola(for SPI) 出于不同背景和市场需求制定了这两种标准通信协议。

参考以下网址:http://blog.csdn.net/ce123/article/details/6878547

以上是关于SPI 协议的理解的主要内容,如果未能解决你的问题,请参考以下文章