时钟初始化

Posted LeoSanford

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了时钟初始化相关的知识,希望对你有一定的参考价值。

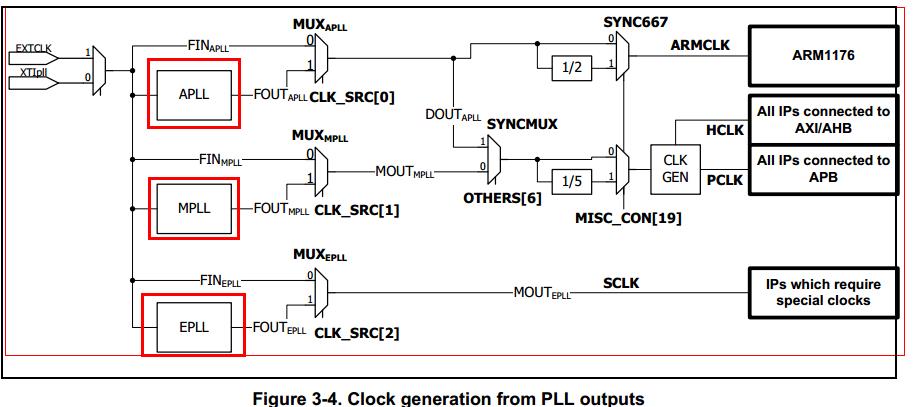

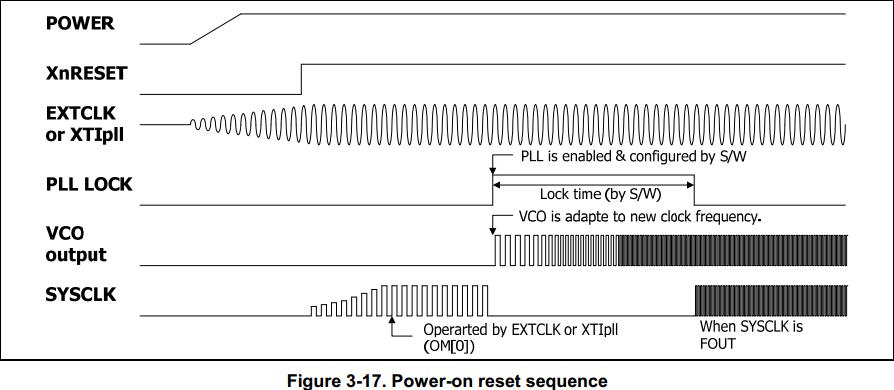

1.时钟体系的了解

所用晶振:12M

PLL的个数:APLL、MPLL、EPLL

产生的时钟及其用途:

| 时钟 | 应用场合 | 应用举例 | 所属PLL |

| ACLK | 处理器 | arm11 | APLL |

| HCLK | AHB总线 | LCD、DMA... | MPLL |

| PCLK | APB总线 | GPIO、Uart | MPLL |

| SCLK | USB总线 | USB | EPLL |

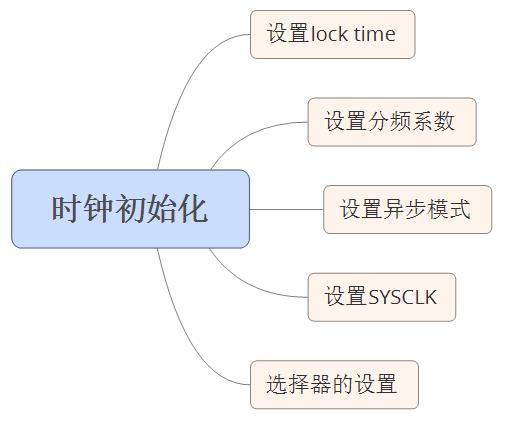

2.时钟初始化流程

注:SYCLK用于arm核

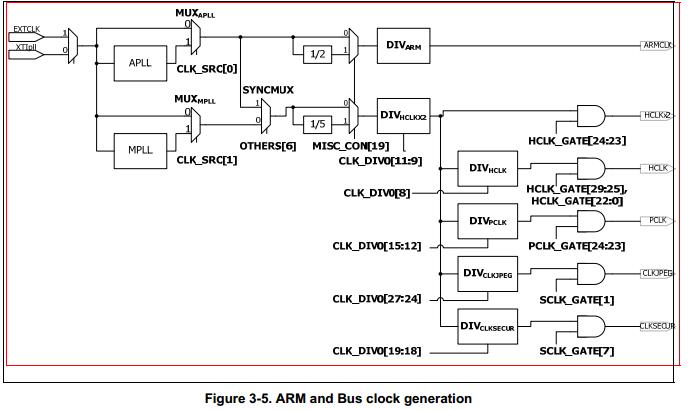

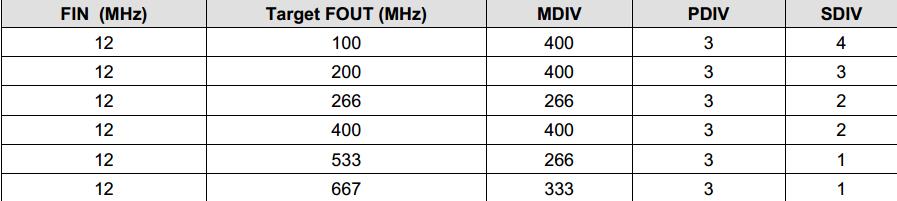

3.分频系数

DIVARM设为0,DIVHCLK2设为1,DIVHCLK设为1,DIVPCLK设为3。

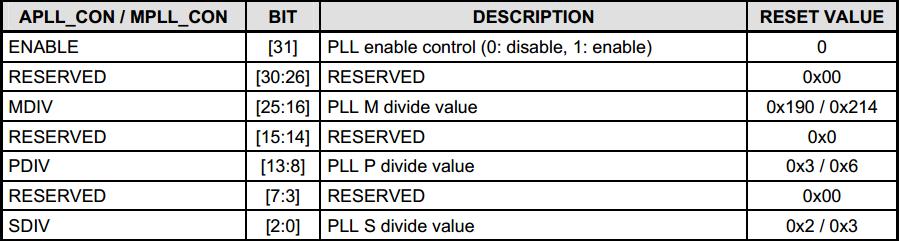

4.设置SYSCLK(APLL、MPLL)

5.汇编代码

#define CLK_DIV0 0x7e00f020 #define OTHERS 0x7e00f900 #define APLL_CON 0x7e00f00c #define MPLL_CON 0x7e00f010 #define CLK_SRC 0x7e00f01c #define DIV_VAL ((0x0<<0)|(0x1<<9)|(0x1<<8)|(0x3<<12)) #define PLL_VAL ((1<<31)|(266<<16)|(3<<8)|(1<<0)) init_clock: ldr r0,=CLK_DIV0 ldr r1,=DIV_VAL str r1,[r0] ldr r0,=OTHERS ldr r1,[r0] bic r1,r1,#0xc0 str r1,[r0] ldr r0,=APLL_CON ldr r1,=PLL_VAL str r1,[r0] ldr r0,=MPLL_CON ldr r1,=PLL_VAL str r1,[r0] ldr r0,=CLK_SRC mov r1,#0x03 str r1,[r0] mov pc,lr

以上是关于时钟初始化的主要内容,如果未能解决你的问题,请参考以下文章