U-Boot-时钟初始化

Posted _WILLPOWER_

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了U-Boot-时钟初始化相关的知识,希望对你有一定的参考价值。

6410和2440的使用晶振频率为12M,210为24M

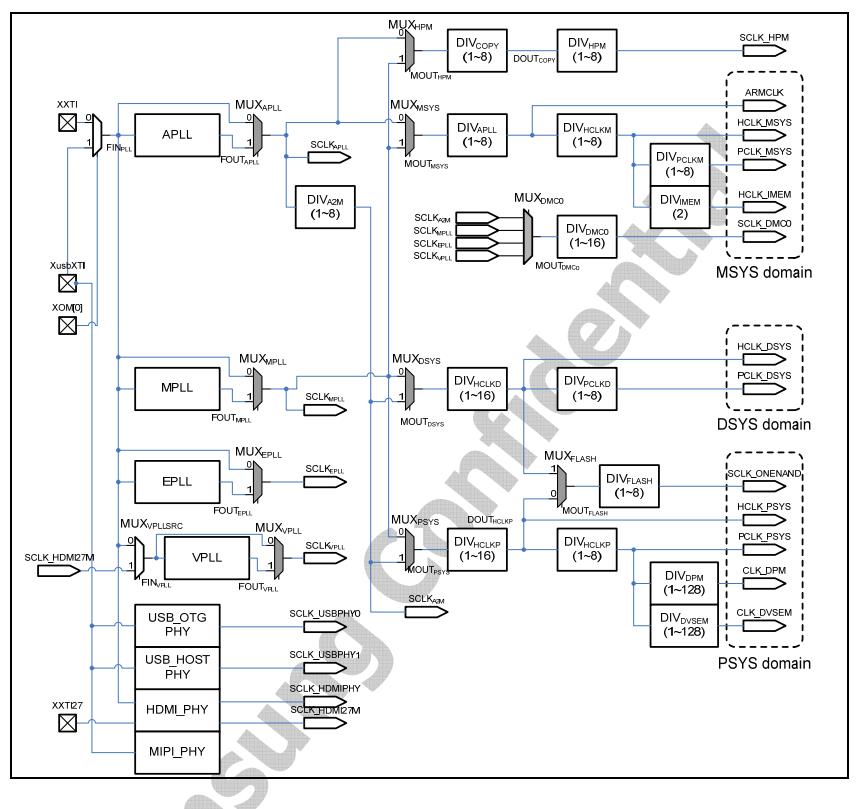

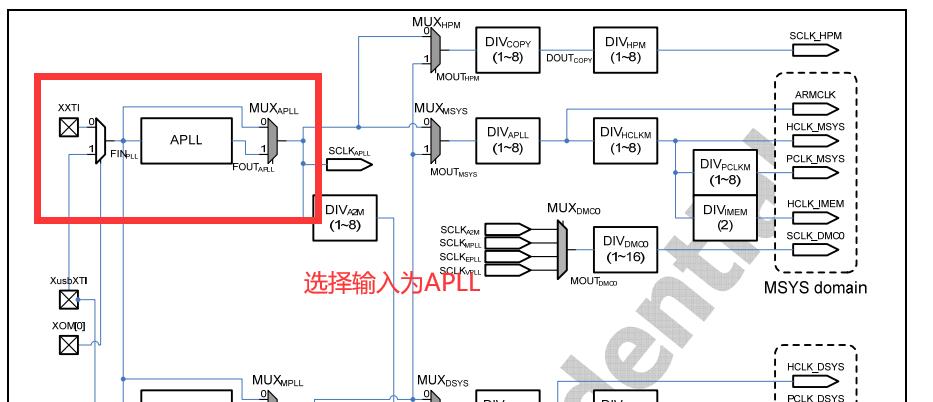

210

电路图

-

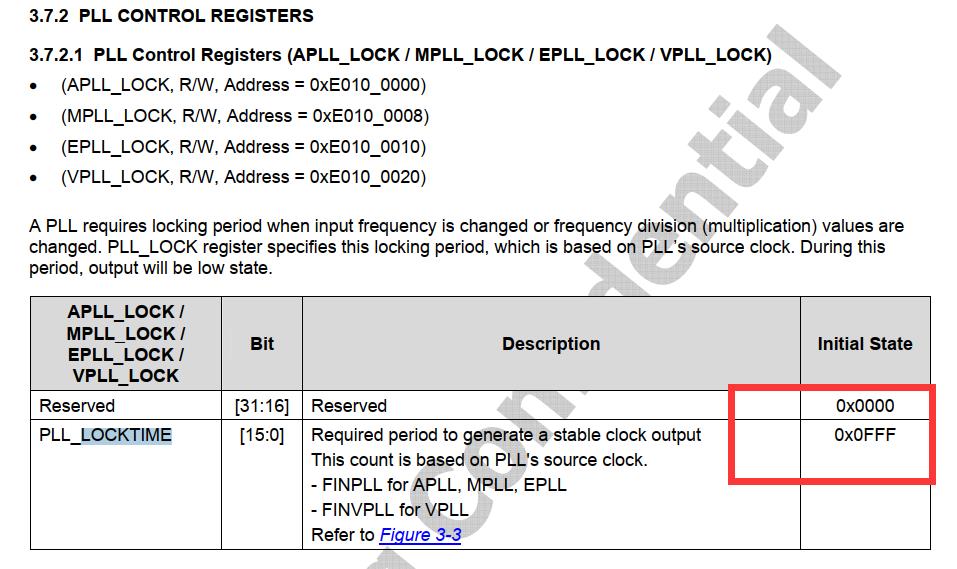

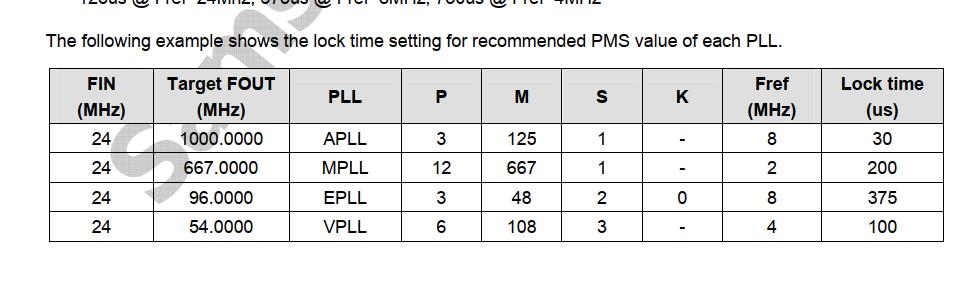

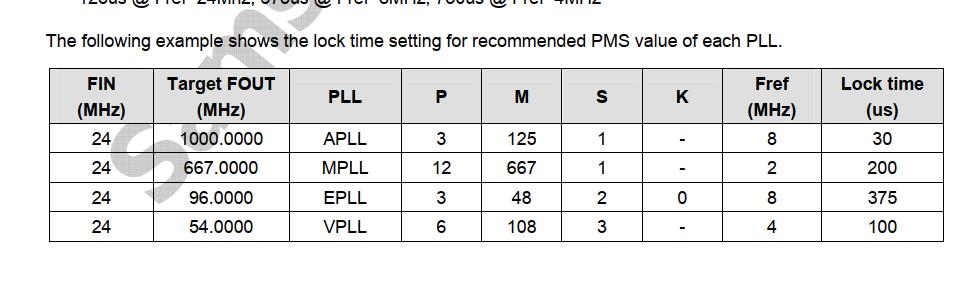

设置lock_time

当输入频率改变或频分(乘)值改变时,锁相环需要lock周期。PLL LOCK寄存器指定这个锁定周期,它基于PLL的源时钟。在此期间,输出将处于低状态。

使用初始值即可

-

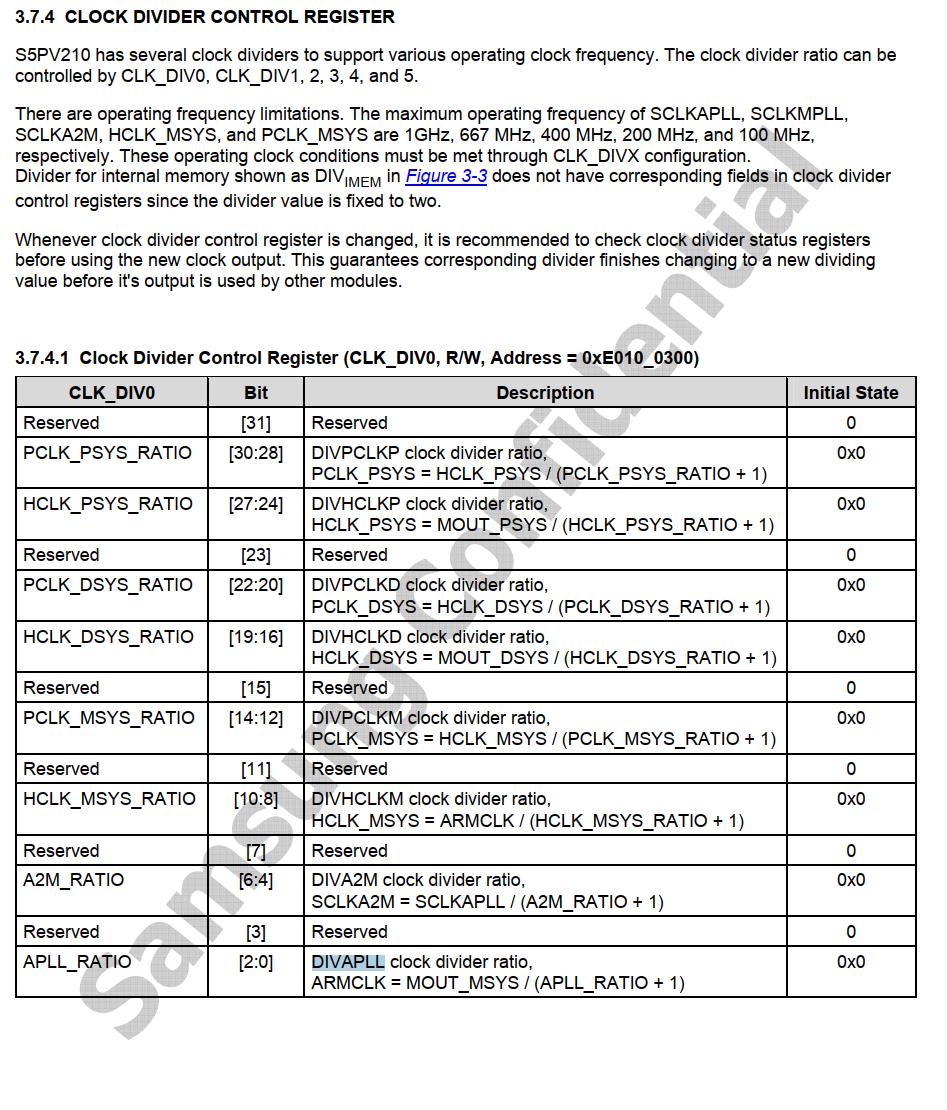

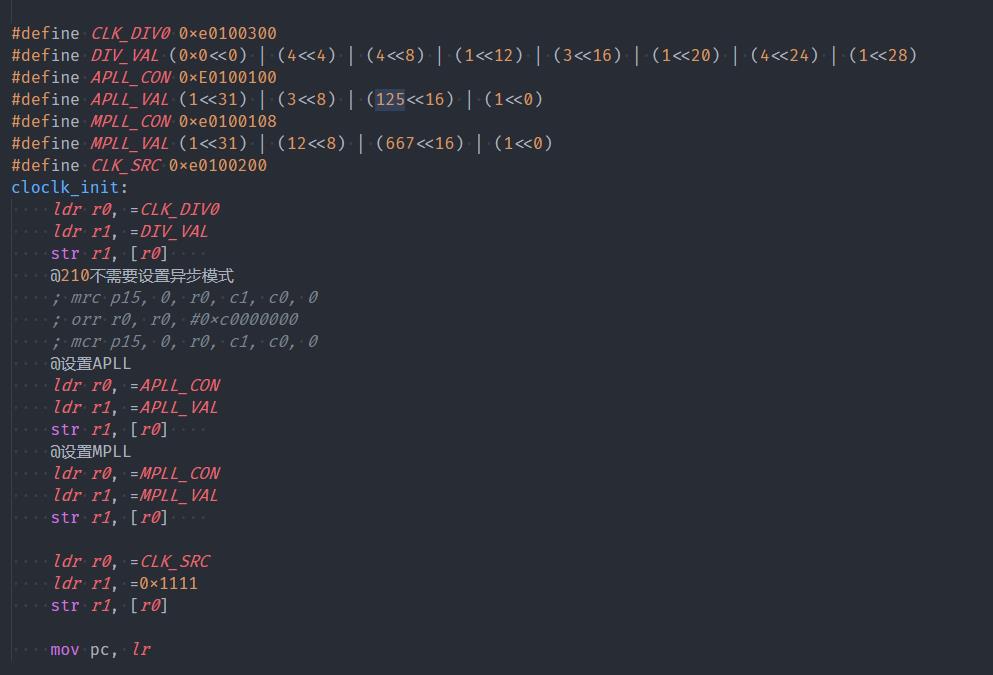

设置分频系数

参考U-Boot源码设置

#define CLK_DIV0 0xe0100300

#define DIV_VAL (0x0<<0) | (4<<4) | (4<<8) | (1<<12) | (3<<16) | (1<<20) | (4<<24) | (1<<28)

cloclk_init:

ldr r0, =CLK_DIV0

mov r1, #DIV_VAL

str r1, [r0]

-

异步工作模式

210不需要设置异步工作模式,这步跳过 -

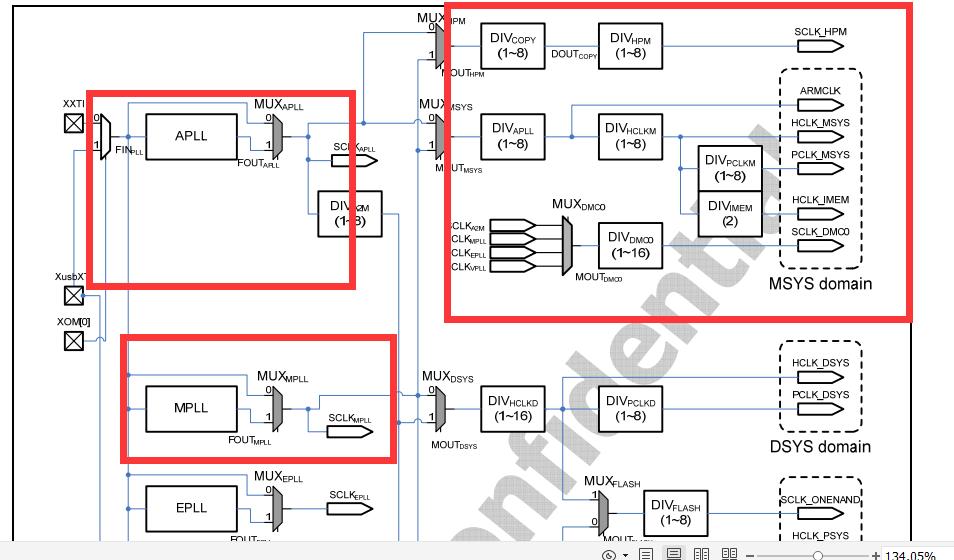

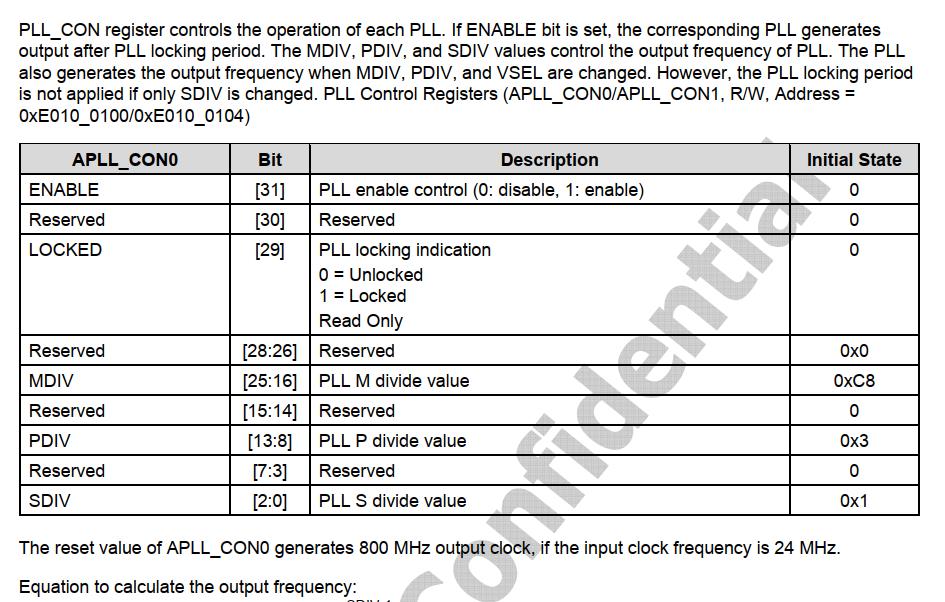

APLL和MPLL的设置

APLL设置

这里输出的频率我们需要是1000,因此P、M以及S设置为3、125、1

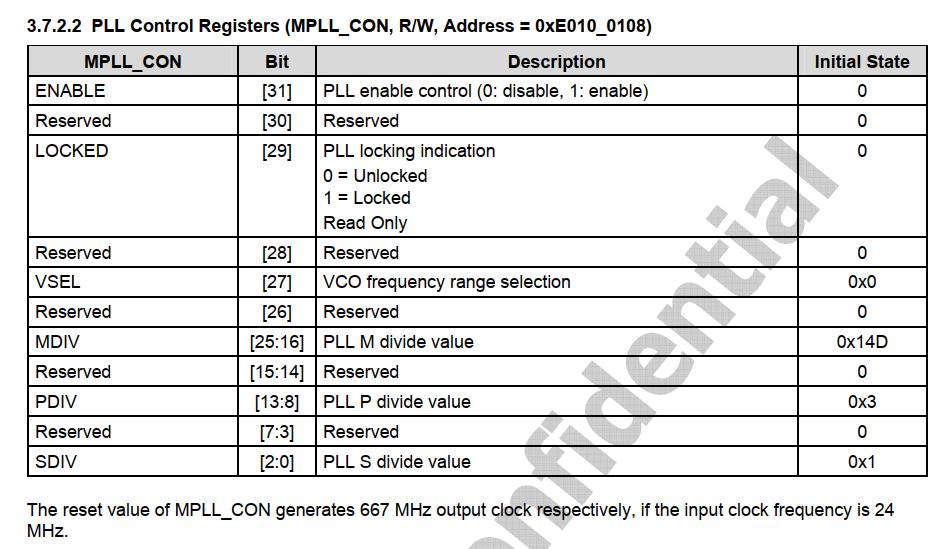

MPLL设置

P、M以及S设置为12、667、1

- 选择器

ldr r0, =CLK_SRC

ldr r1, =0x1111

str r1, [r0]

选择VPLL、MPLL、APLL因此你设置为0x1111

总体代码

#define CLK_DIV0 0xe0100300

#define DIV_VAL (0x0<<0) | (4<<4) | (4<<8) | (1<<12) | (3<<16) | (1<<20) | (4<<24) | (1<<28)

#define APLL_CON 0xE0100100

#define APLL_VAL (1<<31) | (3<<8) | (125<<16) | (1<<0)

#define MPLL_CON 0xe0100108

#define MPLL_VAL (1<<31) | (12<<8) | (667<<16) | (1<<0)

#define CLK_SRC 0xe0100200

cloclk_init:

ldr r0, =CLK_DIV0

ldr r1, =DIV_VAL

str r1, [r0]

@210不需要设置异步模式

; mrc p15, 0, r0, c1, c0, 0

; orr r0, r0, #0xc0000000

; mcr p15, 0, r0, c1, c0, 0

@设置APLL

ldr r0, =APLL_CON

ldr r1, =APLL_VAL

str r1, [r0]

@设置MPLL

ldr r0, =MPLL_CON

ldr r1, =MPLL_VAL

str r1, [r0]

ldr r0, =CLK_SRC

ldr r1, =0x1111

str r1, [r0]

mov pc, lr

以上是关于U-Boot-时钟初始化的主要内容,如果未能解决你的问题,请参考以下文章