信号的抽取和插值

Posted 大西瓜FPGA --logic3

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了信号的抽取和插值相关的知识,希望对你有一定的参考价值。

信号的抽取和插值

减少抽样率以去掉过多数据的过程称为信号的抽取(decimatim),增加抽样率以增加数据的过程称为信号的插值(interpolation)。抽取、插值及其二者相结合的使用便可实现信号抽样率的转换。

一般多速率变换传输系统结构:

抽取,可以在传输的过程中减少传输的数据量,接收端进行恢复时进行插值,将信号恢复成原始抽样率的信号。在数字信号处理中只需要改变数字采样率,一般是先进行插值再进行抽取,以免造成频率混叠,同时在抽取的前先进行预滤波,在插值后进行以个去镜像滤波。

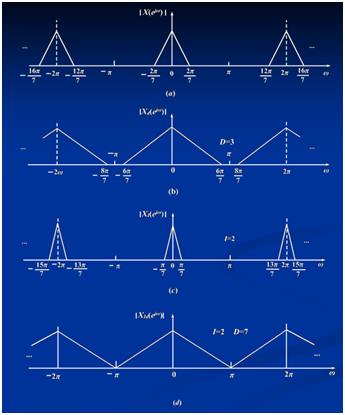

进行抽取时,原始信号的频谱被周期拓展,如果原始信号最高频率大于抽取之后采样率的一半就会发生混叠(如果是复信号,则信号最高频率大于抽取之后采样率就会发生混叠)。若抽取率为D的话,则输出的信号频率将变为原来频率的D倍,将x(n)的抽样频率减小D倍每D个抽样中取一个,D为整数, 称为抽样因子。

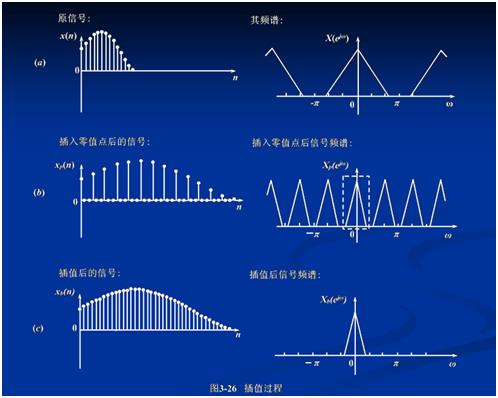

插值也会让频谱周期拓展,但由于输出信号点数增多,所以频率分量只是周期存在,不会发生混叠。如果希望将x(n)的抽样频率增加I倍,即变成I x(n) ,那么,最简单的方法就是将x(n)每两个点之间补I-1个零,I称为插值因子,插值后的信号变为原来信号频率的1/I。

Matlab中进行抽取和插值的指令为

Downsample(x,d);x为信号,D为抽取因子;

Interp(x,i);x为信号,i为插值因子;

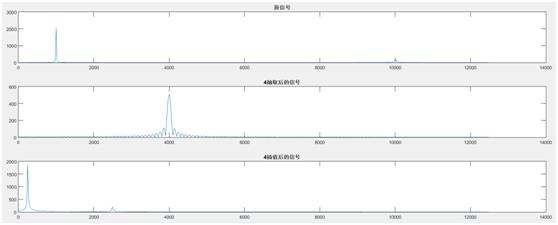

以下为对一个1k的信号分别进行4插值和4倍抽取,处理后通过matlab的FFT分析得到如下的频谱。4插值后的信号频率变为原来的1/4,4倍抽取后信号的频率变为原来的4倍。

大西瓜FPGA-->https://daxiguafpga.taobao.com

博客资料、代码、图片、文字等属大西瓜FPGA所有,切勿用于商业! 若引用资料、代码、图片、文字等等请注明出处,谢谢!

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。

以上是关于信号的抽取和插值的主要内容,如果未能解决你的问题,请参考以下文章