Xilinx Zynq-7000嵌入式系统设计与实现 学习教程

Posted schips

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Xilinx Zynq-7000嵌入式系统设计与实现 学习教程相关的知识,希望对你有一定的参考价值。

开篇体会;

Xilinx的ZYNQ系列FPGA是二种看上去对立面的思想的融合,ARM处理器的串行执行+FPGA的并行执行,着力于解决大数据处理、人工智能等复杂高性能算法处理。

新的设计工具的推出,vivado HLS,更加注重嵌入式系统的系统级建模,通过HLS工具,用户只需要编写C语言代码,就可以让工具自动转换和生成HDL代码

随着异构架构和片上系统技术的不断发展,协同设计、协同仿真和协同调试将成为未来嵌入式系统开发者必备的素质。所谓的协同,就是要求设计者同时掌握软件和硬件知识,这与传统上软件和硬件分离的设计方法有着本质的区别。

由于半导体技术的不断发展,使得电子系统从传统的PCB板级进化到芯片级,对于嵌入式系统的小型化、低功耗和可靠性的改善都提供了强大的保证。

①全可编程片上系统基础知识

以传统的现场可编程门阵列结构(Field Programmable Gate Array,FPGA)为基础,将专用的中央处理器单元(Central Processing Uint,CPU)和可编程逻辑资源集成在单个芯片中,产生了一种全新的设计平台,我们称之为全可编程片上系统(ALL Programmable System-on-chip,APSoC).

SoC的架构如下:(固化、灵活性差、专用性强、设计复杂)

APSoC的架构呢??(由词的全拼意淫,灵活性强,既有固化的又有可灵活控制的。。。)

SoC、CPU、MCU的比较?

SoC:可以集成多个功能强大的处理器内核、可以集成存储块、IO资源及其他外设、可以集成GPU\\DSP\\音频视频解码器等、可以运行不同的操作系统、用于高级应用如智能手机\\平板电脑等

CPU:单个处理器核、需要外部额外的存储器核外设支持、应用绝大多数场合

MCU:典型的只有一个处理器内核、内部包含了存储器、IO及其他外设、用于工业控制领域如嵌入式应用

APSoC的诞生背景:

在全可编程平台设计阶段,设计已经从传统上以硬件描述语言HDL为中心的硬件逻辑设计,转换到以C语言为代表的软件为中心的功能描述,所以就形成了以C语言描述嵌入式系统结构的功能,而用HDL语言描述硬件的具体实现的设计方法,这也是基于全可编程SoC和传统上基于SoC器件实现嵌入式系统设计的最大区别,即真正实现了软件和硬件的协同设计。

最大优点可实现硬件加速:

设计者可以根据需求在硬件实现和软件实现之间进行权衡,使所设计的嵌入式系统满足最好的性价比要求,例如,在实现一个嵌入式系统设计时,当使用软件实现算法成为整个系统性能的瓶颈时,设计人员可以选在在全可编程SoC内使用硬件逻辑定制协处理器引擎来高效的实现该算法,这个使用硬件逻辑实现的协处理器,可以通过AMBA接口与全可编程SoC内的ARM Cortex A9嵌入式处理器连接,此外,通过XilinX所提供的最新高级综合工具HLS,设计者很容易将软件瓶颈转换为由硬件处理。

②全可编程片上系统中的处理器类型

根据不同的需求,全可编程片上系统的处理器可以分为软核和硬核处理器。

硬核处理器:早期Xilinx将IBM公司的PowerPC硬核集成在V5系列的FPGA中,后来将ARM公司的双核Cortex-A9硬核集成在ZYNQ 7000系列的SoC芯片中

软核处理器:对于一些对处理器性能要求不是很高的需求,没有必要在硅片上专门划分一定的区域来实现专用的处理器,而是通过使用FPGA芯片内所提供的设计资源,包括LUT\\bram、触发器和互联资源,实现一个处理器的功能,这就是软核处理器,对于软核处理器,他通过HDL语言或者网表进行描述 ,通过通过综合后才能被使用。

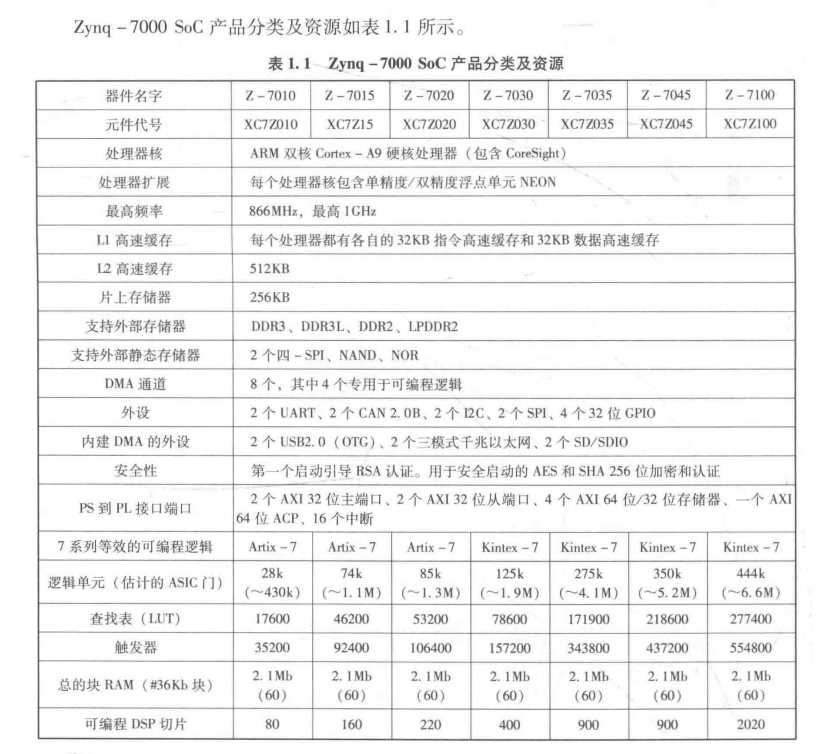

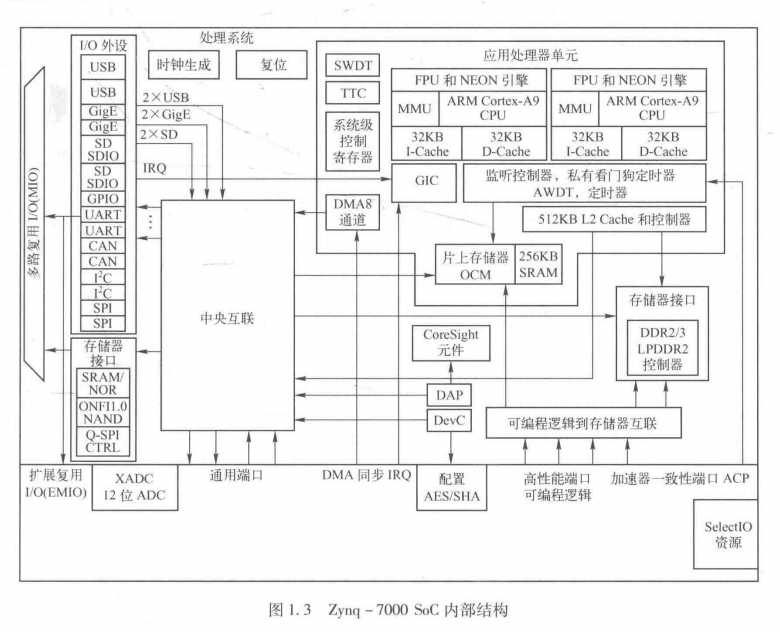

③ZYNQ-7000 SoC功能与结构

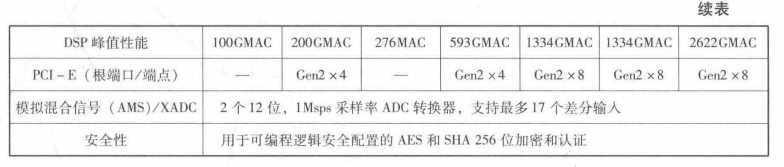

在该全可编程SoC中,双核ARM-Cortex-A9多核CPU是PS的心脏,它包含片上存储器、外部存储器接口和丰富功能的外设。

与传统的FPGA和SoC相比,ZYNQ7000不但提供了FPGA灵活性和可扩展性,也提供了专用集成电路的相关性能、功耗和易用性。

ZYNQ 7000的结构便于将定制逻辑和软件分别映射到PL和PS中,这样就可实现独一无二和差异化的系统功能。

与传统的FPGA方法不同的是,ZYNQ 7000 SoC总是最先启动PS内的处理器,这样允许PS上运行的基于软件程序用于启动系统并且配置PL,这样可以将配置PL的国政设置成启动过程的一部分或者在将来的某个时间再单独的配置PL,此外可以实现PL的完全重配置或者使用部分可重配置(PR,Partional Reconfihuration,允许动态的重新配置PL中的某一个部分,这样能够对设计进行动态的修改)。

以上是关于Xilinx Zynq-7000嵌入式系统设计与实现 学习教程的主要内容,如果未能解决你的问题,请参考以下文章

Xilinx推出低功耗-小容量-小封装ZYNQ Ultrascale+ MPSoC,特别适合用于ZYNQ-7000升级换代