在做在线远程升级的时候,一般需要两步:1、将数据写到外挂的flash中。2重新启动FPGA配置。 不过要做到远程升级,一般需要在原始程序中就考虑到加入远程升级模块,remote updata IP, 在升级的时候才可以启动远程升级功能。

远程升级之后程序加载的过程: 在进行远程升级成功以后,flash中应该会至少存储两个程序,出厂程序和升级程序。 两个程序在不同的地址空间中(出厂程序从0X0000开始存储)。在FPGA上电之后,FPGA会加载出厂程序,出厂程序在运行之后,检测到remote updata IP中的一些参数(如配置镜像参数等,remote updata IP部分会介绍到)后,将读取flash中升级程序内容的开始地址指向读取地址,然后触发重新配置(如reconfig信号有效),开始加载重新配置程序。直到无错误的加载完成。也就是整个过程会加载两次程序。

一、 如何将程序写到flash中。

在程序运行过程中,可以通过控制一些IP来将程序写到flash中,这里有两个IP可以使用:EPCS controller, ASMI .

1、 EPCS Controller:

该IP在Qsy系统中,一般需要配合Nios II来使用,需要使用者对ARM的编程有一定的基础。不过Altera 也提供了一些有关epcs操作的API,如读写,擦除等。不过在操作前会读取一下FLASH的ID来确定是EPCS还是EPCQ,或者EPCQL,还有容量是多大的。确定好Flash的类型之后就可以调用API函数对Flash操作了。网上也有例程,如锆石科技的参考例程。不过如果使用的是第三方的flash,而读取的ID不在官方flash的ID列表之后,则就会认为没有flash,也就无法读写操作了(不敢百分百确定的,但是肯定要改程序)。所以需要操作者对ARM的操作有一定的知识。

EPCS Controller IP在cyclone IV上使用的时候是需要手动绑定那四个pin的,在cyclone V上是不需要绑定的。

2、ASMI IP

该IP在IP库中,Qsys中也有,可以直接用verilog进行编程控制,网上也有中文文档:ug_altasmi_parallel_CH.pdf 。该文档会介绍如何擦除,读写flash等,只要时序控制好,EPCS/EPCQ/EPCQL的空间地址控制号就可以了。网上或官方都有参考例程,可以参考一下。

二、 如何打开下载程序文件

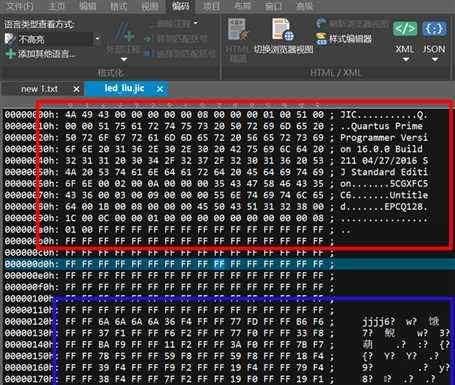

远程烧录,需要PC等通过串口或网络将程序传给FPGA,程序文件一般是jic/sof/rbf等格式的文件,那么一般软件不能打开也看不到里面的内容,可以使用UltraEdit软件来打开这些文件,而且里面还会有一部分提示。

但是这个文件会很大,比如16MB,并不是所有的都是有效的信息,我现在也不知道该写哪一些数据到flash中,以后知道了再补充吧。

三、remote updata IP

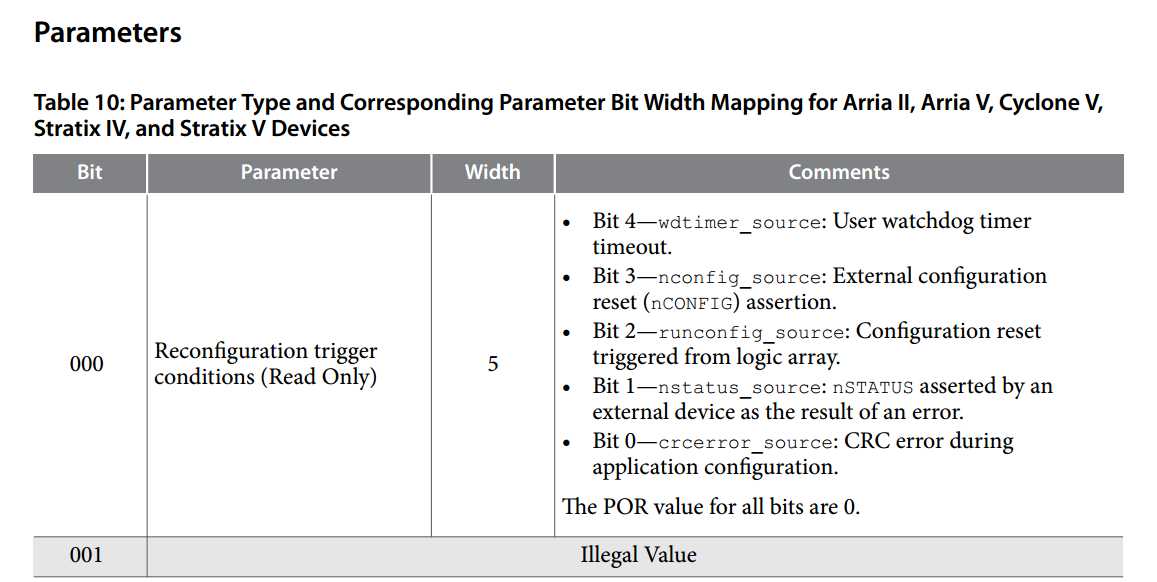

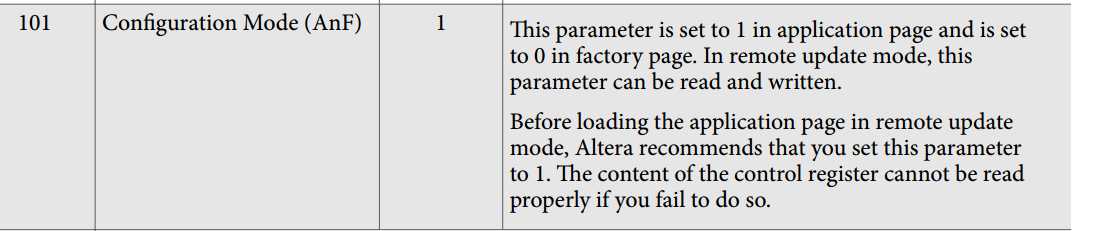

该IP在IP库和Qsys中都有,可以用verilog来控制,建议使用前也要先看下他的说明书,ug_altremote.pdf,里面对寄存器有详细的说明。

在使用过程其实是读取寄存器或者写寄存器的过程,最后一步reconfig信号就可以了。

网友给出了一个思路: read 3‘b000 (读取reconfig的条件) --》 write 3‘b101(Anf配置模式选择:出厂or镜像) --》 read Anf 3‘b101(确定一下) --》write 3‘b011 (写看门狗使能) --》

write 3‘b010(写看门狗溢出值) --》 write 3‘b100 (写看门狗溢出值) --》 reconfig 使能。然后就操作完成了,等待重新启动。

.