FPGA--pll变频

Posted caiya

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA--pll变频相关的知识,希望对你有一定的参考价值。

Altera 的 Cyclone IV 器件 PLL 具有时钟倍频和分频、相位偏移、可编程占空比和外部时钟输出,进行系统级的时钟管理和偏移控制。 Altera 的 Quartus II 软件无需任何外部器件,就可以启用 Cyclone IV PLL 和相关功能。

下面演示如和调用 Altera 提供的 ALTPLL 核来产生 不同频率的时钟, 并把时钟输出到 FPGA 外部 IO 上:

1,建立工程(具体见上面一篇博客)

2,然后打开 IP 生成向导,选择菜单 Tools->MegaWizard Plug-In Manager。

3,在 IP 向导界面的第一页选择默认的 Create a new custom megafunction variaion, 再点击 Next。

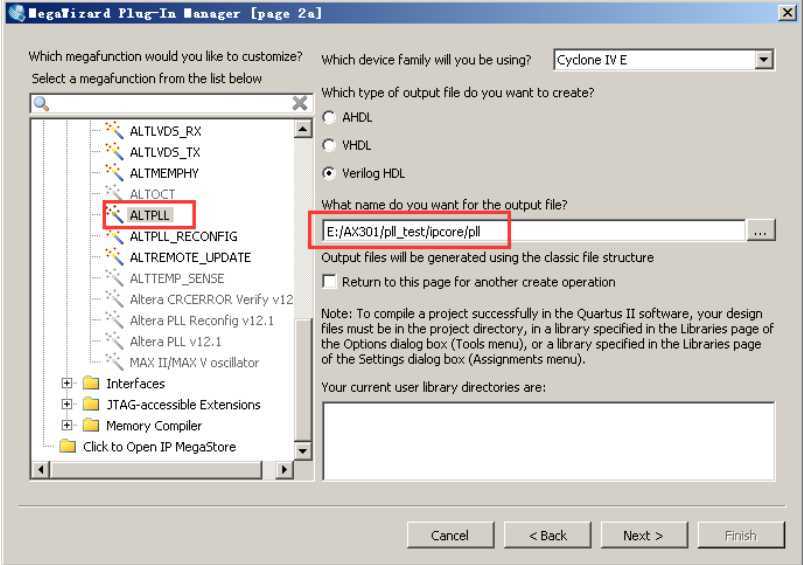

4,在 IP 向导界面的第二页的 IP 列表中选择 I/O 目录下的 ALTPLL, 然后在"What name doyou want for the output file?"栏中输入 IP 存放的目录及名称, 这里的 IP 名字我们取名为 pll。

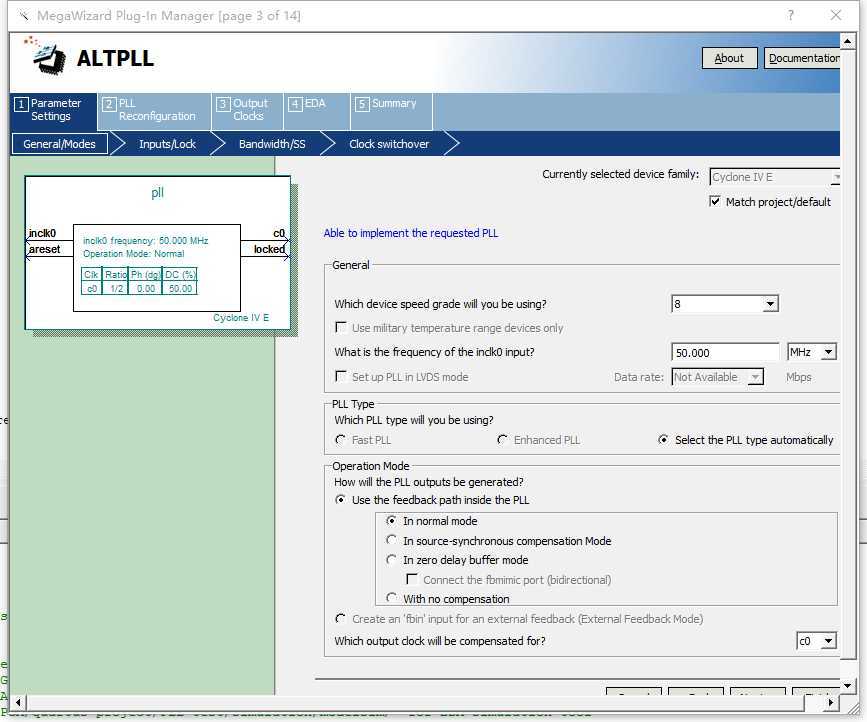

5,在 ALTPLL 配置的 Page3 界面里修改 PLL 的输入时钟为 50Mhz, 因为我们开发板上用的时钟为 50Mhz。 另外 PLL 的工作模式有四种,这里我们选择默认的 In normal mode。

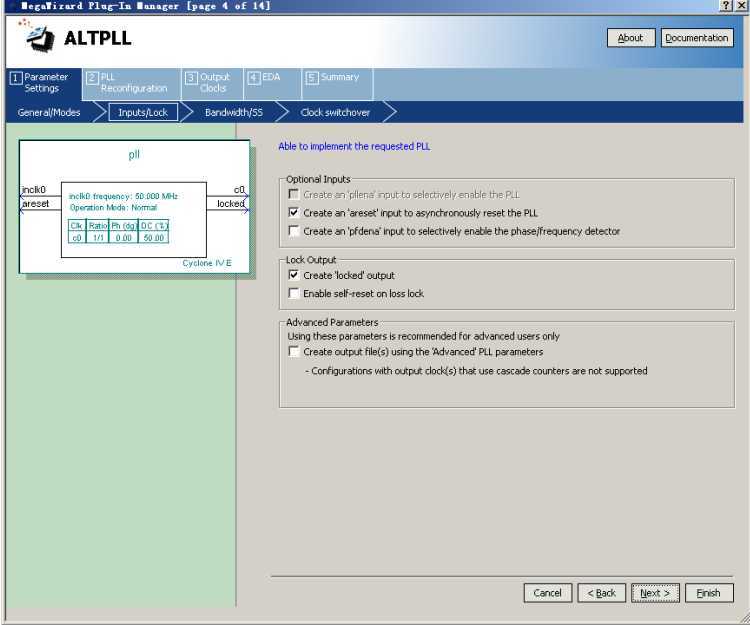

6,Page3 界面选择默认的输入和输出信号就可以。

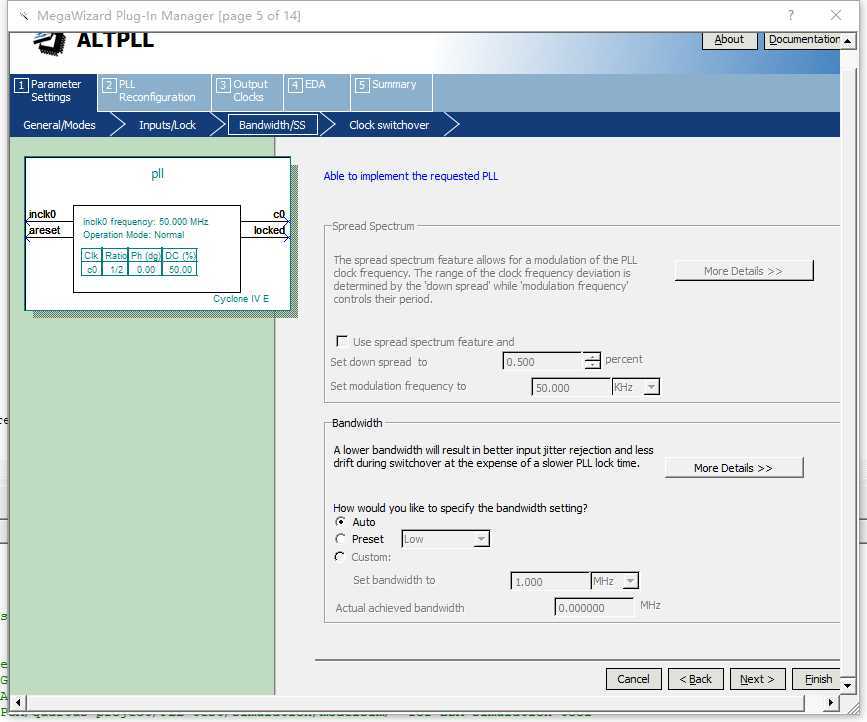

7,保持默认就好。

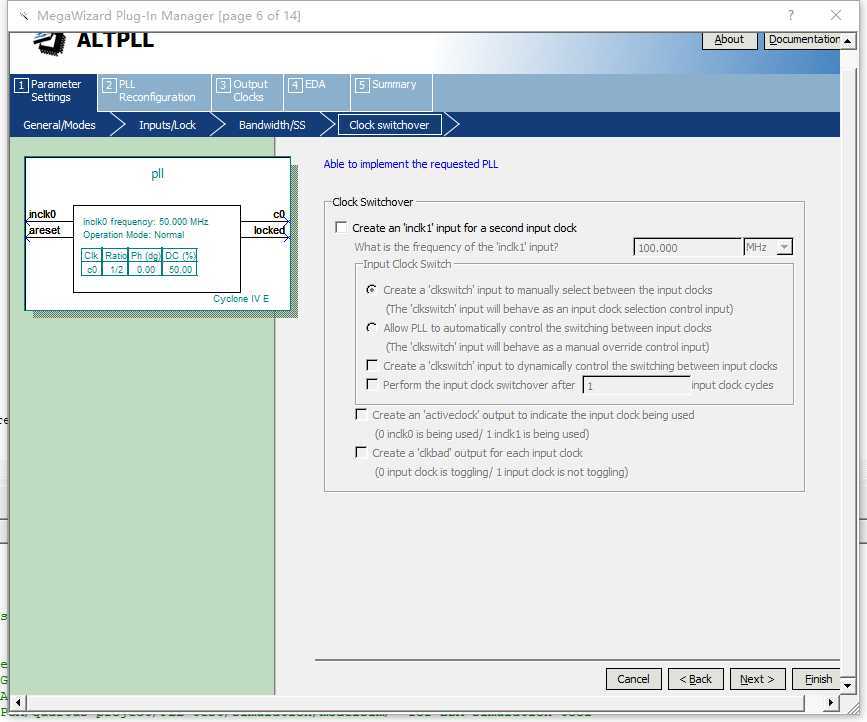

8,配置 Page6 选择输入始终 inclk1,我们这里不用,保持默认的设置,点击 Next 按钮。

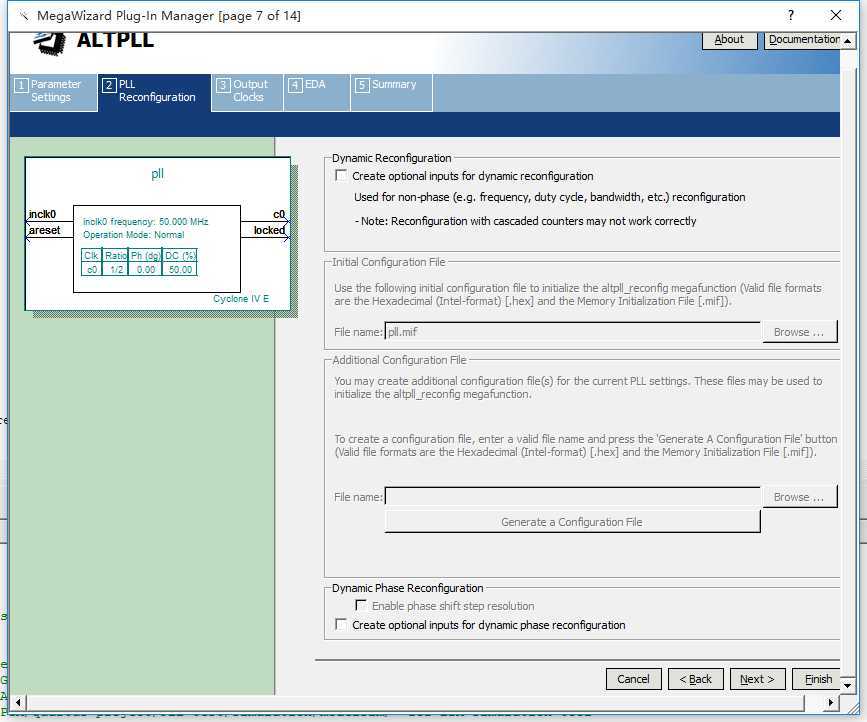

9,Page7 选择动态配置 PLL 输出,实现在线的实时配置,如果我们输出的 PLL 的频率是固定的就不需要选择。

10,在配置的第 8 个界面里选择 c0 的输出频率,这里我们直接手动输入 c0 的频率输出为 25Mhz。 软件会自动计算 VCO 的 M 值和 N 值。

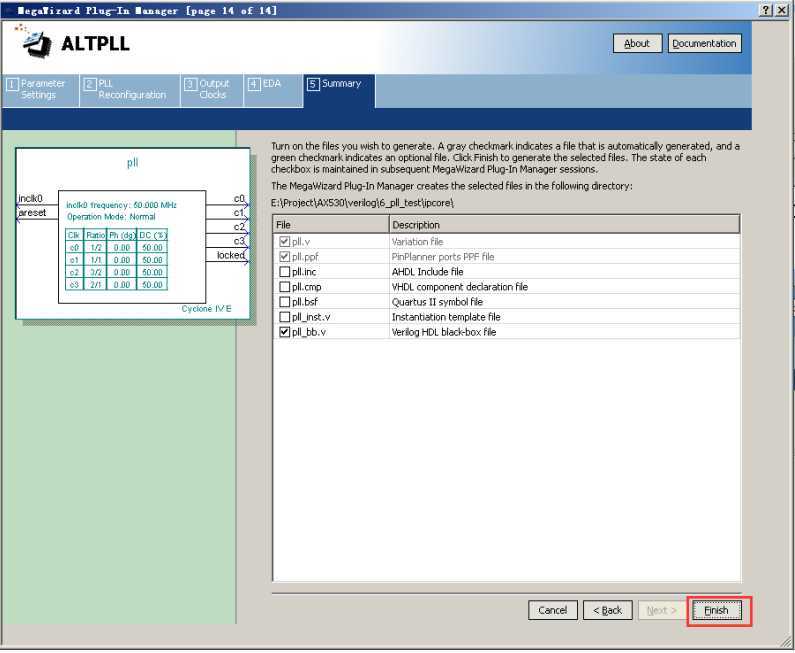

11,clk c1,c2,c3,c4都取消勾选 use this clock,这里只输出一路。然后点击finish;

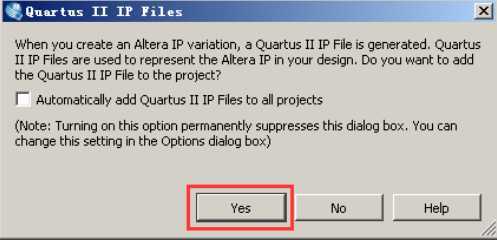

12,软件提示添加 IP 文件到工程里,我们点击 Yes 按钮。

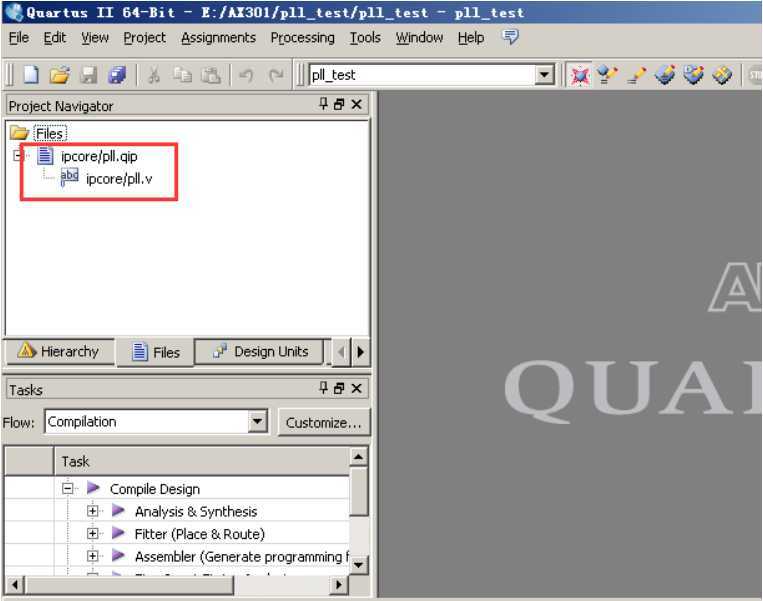

13,在 File 界面里,我们可以看到生成的 pll.qip 和 pll.v 文件已经添加到工程中。

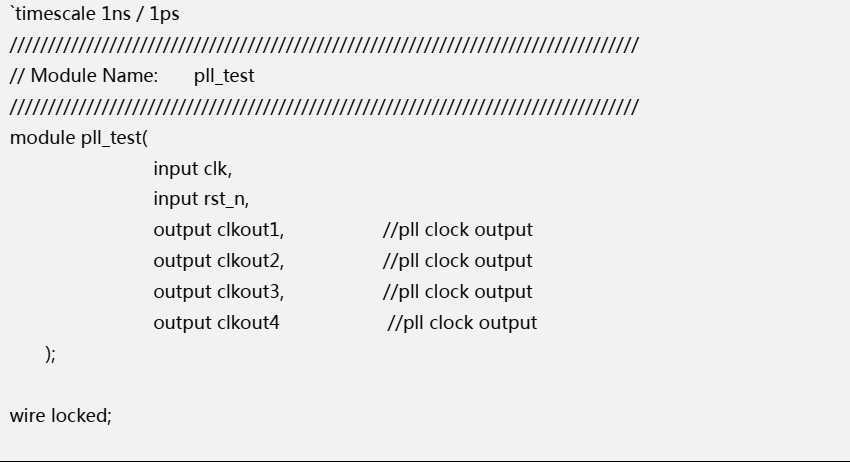

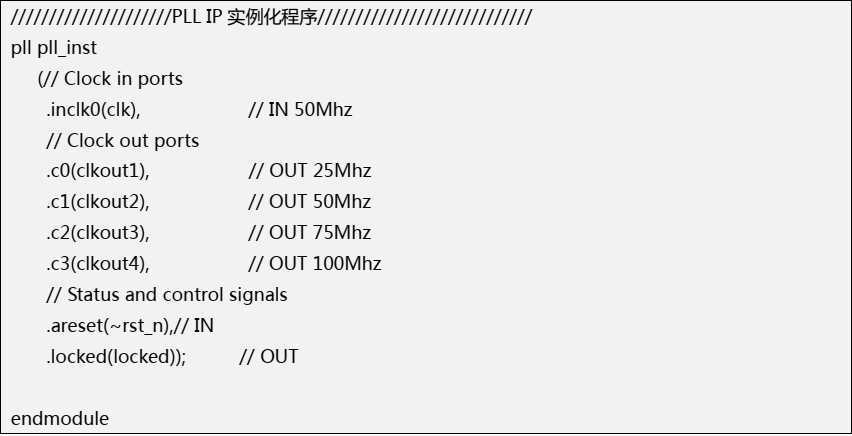

14,设计一个 verilog 文件来实例化这个 PLL IP, 编写的 verilog 代码如下。

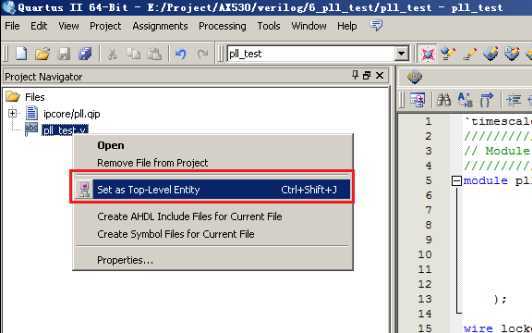

15,保存,并设置该模块为顶层;

16,配置管脚,Compile Design 编译工程,下载即可。

以上是关于FPGA--pll变频的主要内容,如果未能解决你的问题,请参考以下文章