jchdl - GSL Port

Posted wjcdx

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了jchdl - GSL Port相关的知识,希望对你有一定的参考价值。

org.jchdl.model.gsl.core.meta.Port.java

? ?

?

generated by Intellij IDEA powered by yFiles.

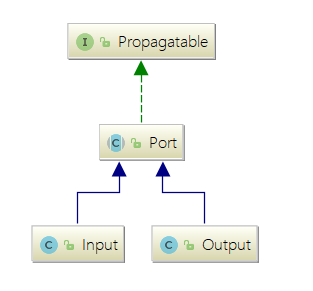

一. 类结构

? ?

?

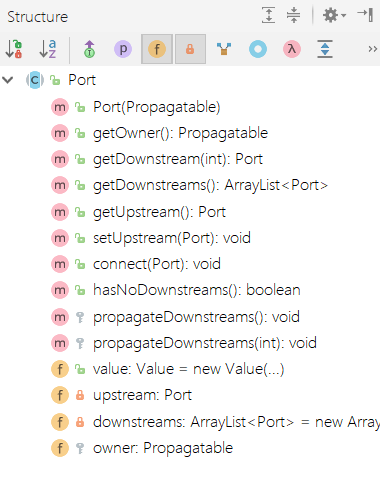

主要属性:

代表接口的值,Value类的对象,有四种值:0, 1, x, z。默认值为x。

Port的所有者,Wire的Port的所有者为Wire,Node的Port的所有者为Node。

与之相连的上级和下级Port。Port只能有一个上级,可以有多个下级。

主要方法:

连接。portA.connect(portB)则portA是portB的upstream,而portB是portA的downstream之一。

其他方法无需关心。

Port无法直接使用,需要使用它的子类,Input(port)和Output(port)。

二. Input/Output

Input/Output并无其他属性,他们实现Propagatable接口的propagate()方法。也就是说,他们向下传播值的行为不同(这个单独说明)。

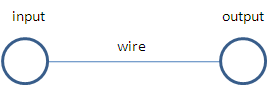

三. 线的Port

? ?

?

线有两个Port,Input和Output。Input port没有downstream,Output port没有upstream。值传播的逻辑由Wire实现,当前的实现逻辑时直接把Input port的值,赋值给Output port。

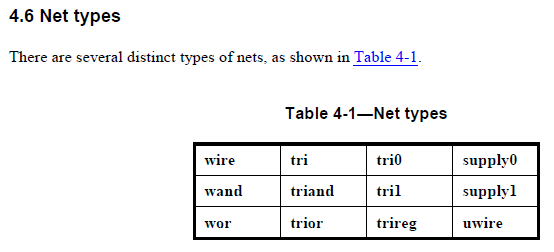

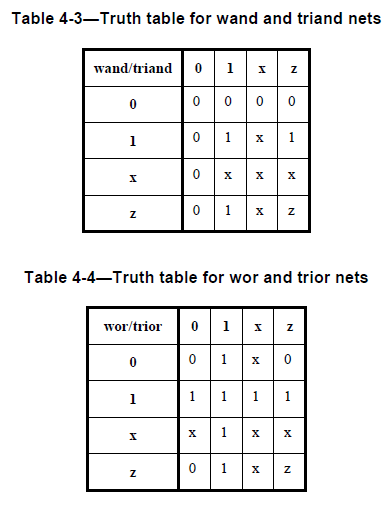

这是显而易见的吗?不是。线,不只有wire一种,Verilog规范中定义了多种Net type:

? ?

?

他们的输出值并不都等于输入值,甚至有多个输入值,如wor:

? ?

?

这里只实现了一种最普通的wire。

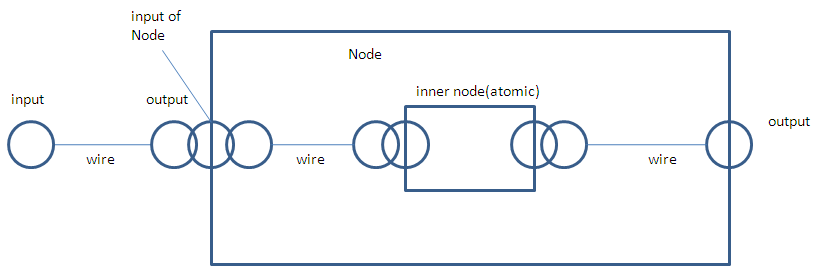

四. 节点的Port

? ?

?

节点的Input port上级总是一个Wire的Output port。

1.如果节点是一个原子节点,则该节点的Input port没有downstreams。

2.如果节点是一个复合节点,则该节点的Input的下级是线的Input port。节点Input的值由上级Wire的Output确定,然后直接赋值给下级Wire的Input。

节点 Output port的下级总是连着Wire的Input port。

1.如果该节点是一个原子节点,则该节点的Output port没有上级,他们的值由原子节点定义的逻辑,根据Input port的值最终确定。比如与门是一个原子节点,他的Output的值,是两个输入的值相与。

2.如果该节点是一个复合节点,则该节点的Output的上级是Wire的Output。节点Output的值,直接有上级Wire Output的值确定,然后传递给下级Wire的Input。

以上是关于jchdl - GSL Port的主要内容,如果未能解决你的问题,请参考以下文章

jchdl - GSL实例 - Counter

jchdl - GSL实例 - Register

jchdl - GSL Port

jchdl - GSL实例 - Shifter

jchdl - GSL实例 - Mux4

jchdl - GSL实例 - Mux4(使用Mux)