Xilinx PLL(Virtex-5)

Posted 皮皮祥的博客

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Xilinx PLL(Virtex-5)相关的知识,希望对你有一定的参考价值。

1. 概述

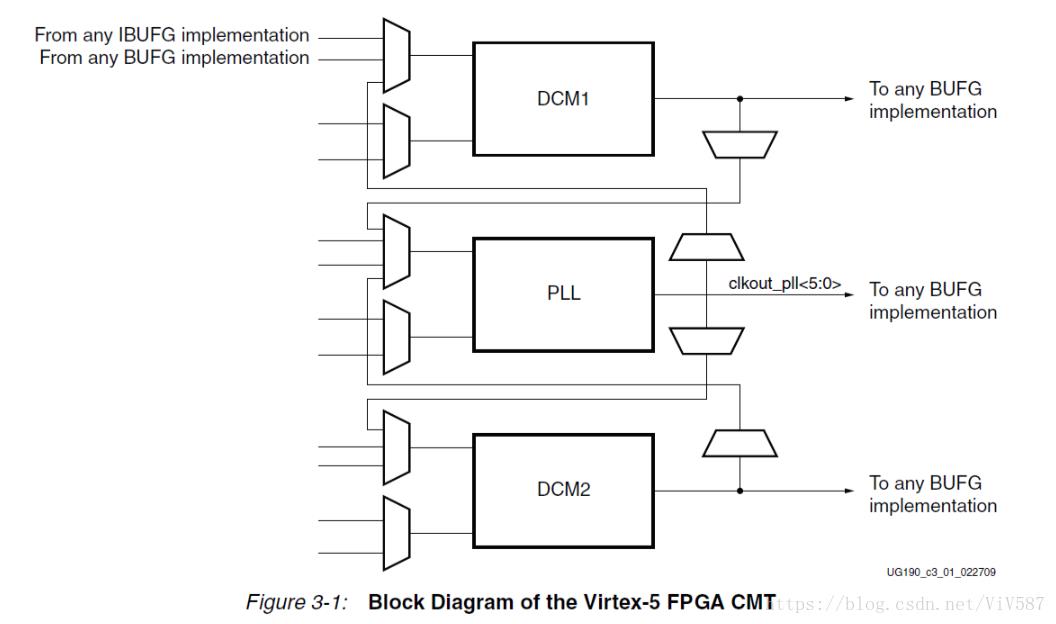

1.1 CMT

Xilinx Virtex-5 FPGA根据不同型号分别有1、2、6个时钟管理片(Clock Management Tile,CMT),每个CMT由一个PLL和两个DCM组成。CMT包含专有路由来连接同一个CMT中的DCM和PLL,使用专有路由可以改进时钟路径。CMT如下图:

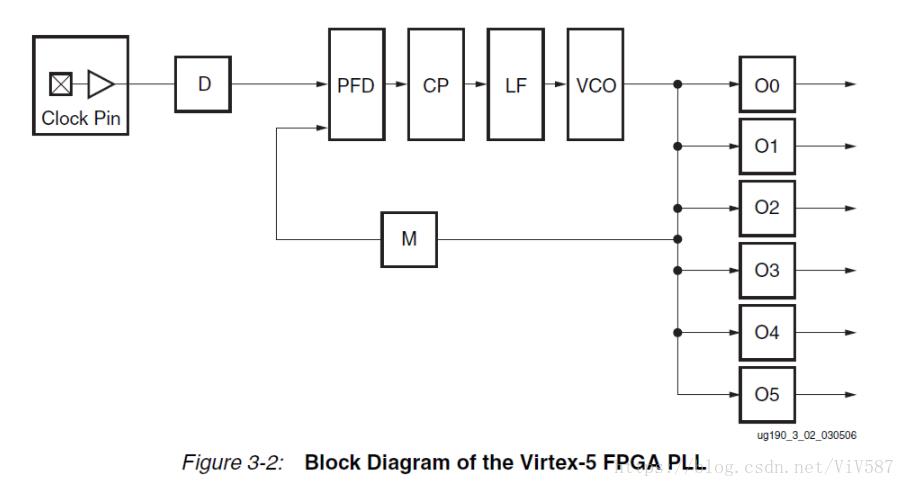

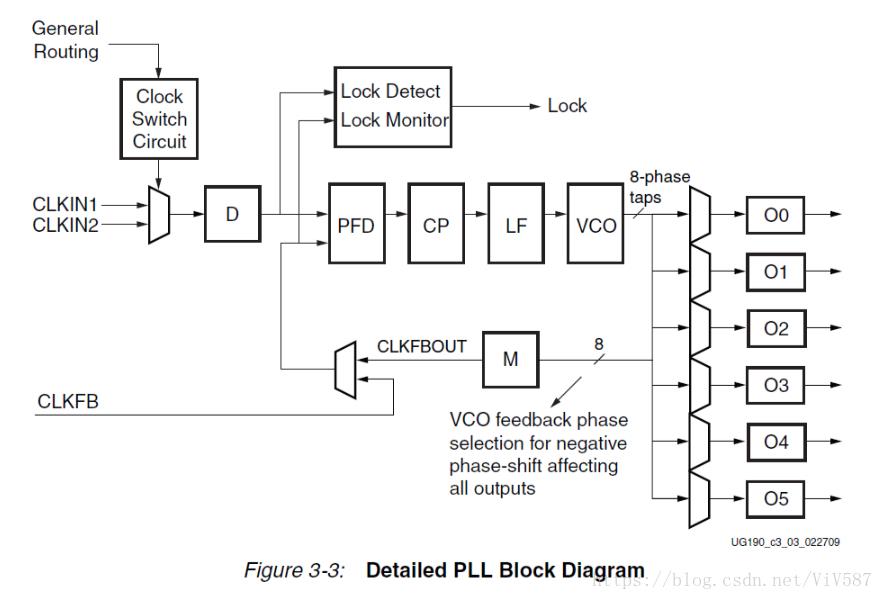

1.2 PLL

PLL框图如下图:

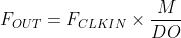

PLL时钟输入来源为:IBUFG、BUFG、IBUF、PLL outputs、DCM outputs。PFD(Phase-Frequency Detector)为相位频率检测器,CP(Charge Pump)为驱动电荷泵,LF(Loop Filter)环路滤波器,VCO为压控振荡器。D、M、O0~O5为可编程计数器,用于分频。PFD比较参考时钟与反馈时钟的相位和频率,产生与两个时钟相位频率成比例的信号来驱动CP和LF产生VCO的参考电压,通过反馈使得参考时钟与反馈时钟频率相位相同。相关公式如下:

2. 一般用法说明

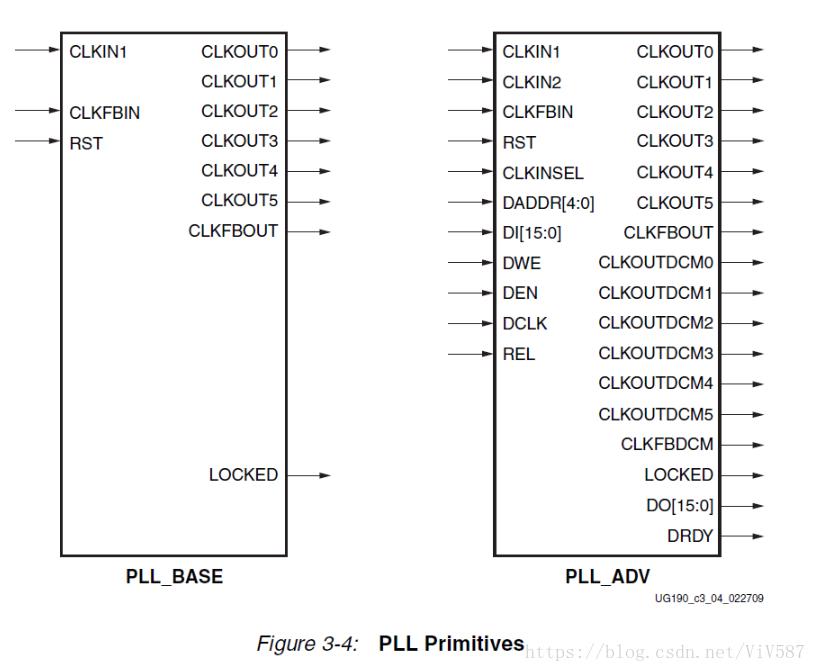

2.1 PLL原语

PLL_BASE原语:PLL_BASE提供时钟偏移校正(Clock deskew)、频率合成(frequency synthesis)、粗略相移(coarse phase shifting)、占空比(duty cycle programming)等功能。

PLL_ADV原语:PLL_ADV提供PLL_BASE的所有功能,还提供输入时钟切换、与同CMT的DCM连接、动态重配置的功能。

接下来讨论时钟网络偏移校正(clock network deskew)、频率合成(frequency synthesis)、降低抑制(jitter reduction)三种模式。

2.2 时钟网络偏移校正(clock network deskew)

PLL和DLL能够补偿时钟网络延迟。将与参考时钟CLKIN频率匹配的时钟输出(通常是CLKFBIN)连接到BUFG并反馈到反馈输入端口CLKFBIN,在这种情况下,所有时钟都与参考时钟具有确定的相位关系。

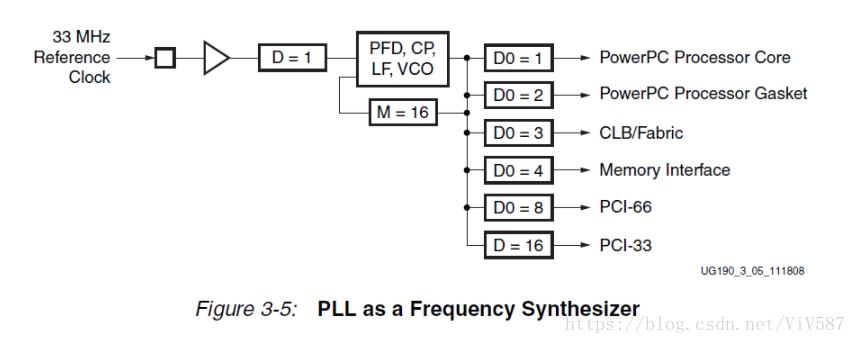

2.3 独立的频率合成(frequency synthesis only)

此模式下,PLL不用于校正时钟网络,而用于为其他模块生成时钟。此模式下,将PLL的反馈路径设为INTERNAL,这样能将所有路由保持在本地,并能减少抖动。此模式下,参考时钟与输出时钟之间没有相应的相位关系,但输出时钟之间具有相应的时钟关系。如下图:

2.4 抖动滤波器(jitter filter)

PLL能减少参考时钟的固有抖动,PLL能够单独作为抖动滤波器实例化,在外部时钟驱动另一个模块之前滤除抖动。作为抖动滤波器,通常假设PLL为缓冲器,并在时钟输出端口上再生输入频率。通常将BANDWIDTH属性设为Low能实现更大的抖动滤波,但会导致PLL的静态偏移增大。

2.5 限制

PLL在VCO工作范围、最小和最大输入频率、占空比、相移等方面有一些限制。

VCO工作范围:详见DS202.Table 74.PLL Specification。

最小和最大输入频率:详见DS202.Table 74.PLL Specification。

占空比:在给定工作频率之后,只能实现部分离散值的占空比。

相移:相移分辨率(Phase Shift)PS=1/(8FVCO)或PS=D/(8MFIN)。由于VCO能提供8个相移(每个45°),因而VCO频率越高,相移分辨率越小。相移分辨率范围1/(8FVCO_MIN)~1/(8FVCO_MAX)。

2.6 PLL设计

两种方法产生PLL:GUI接口(PLL Wizard)、PLL原语。

需要如下信息:1、参考时钟周期

2、输出时钟频率(最多可以有六个)

3、输出时钟占空比(默认为50%)

4、输出时钟相移(相对于最快输出时钟的周期数)

5、PLL所需带宽(默认为OPTIMIZED)

6、补偿模式

7、参考时钟抖动

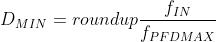

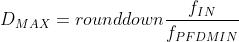

输入时钟确定:第一步确定输入时钟。输入频率给D和M值带来的约束如下:

M和D值的确定:输入时钟的确定会产生一些可能的M和D值,下一步是确定最佳的M和D值。首先基于VCO目标频率(VCO理想工作频率)确定起始M值。

目的是使D和M的值尽可能小,同时保持VCO值尽可能高。

2.7 PLL端口

CLKIN1(Input):通用时钟输入。

CLKIN2(Input):辅助时钟输入,用于动态切换PLL参考时钟。

CLKFBIN(Input):反馈时钟输入。

CLKINSEL(Input):控制输入选择器状态,High=CLKIN1,Low=CLKIN2。

RST(Input):异步复位信号,输入条件改变时,需要复位。

DADDR[4:0](Input):动态重配置地址输入总线,为动态重配置提供重配置地址。 不使用时,必须为所有位分配零。

DI[15:0](Input):动态重配置数据输入总线,提供重配置数据。 不使用时,所有位必须设置为零。

DWE(Input):动态重配置写使能输入端口,提供写使能控制信号以将DI数据写入DADDR地址。 不使用时,必须绑低。

DEN(Input):动态重配置使能,提供使能控制信号以访问动态重配置功能。 不使用时,必须绑低。

DCLK(Input):动态重配置端口参考时钟。

REL(Input):在PLL模式下,保持未连接或低电平。

CLKOUT[0:5](Output):用户可配置时钟输出。输入时钟和输出时钟是相位对齐的。

CLKFBOUT(Output):PLL专用反馈输出。

CLKOUTDCM[0:5](Ouput):用户可配置时钟输出,只能连接到与PLL相同的CMT内的DCM。

CLKFBDCM(Output):应该是用于连接到DCM反馈时钟输入端口。

LOCKED(Output):指示PLL实现相位对齐和频率匹配。若输入时钟停止或违反了相位对齐,则LOCKED置为无效,LOCKED置为无效后必须复位PLL。

DO[15:0](Ouput):动态重配置输出总线,在使用动态重配置时提供PLL数据输出。

DRDY(Output):动态重配置就绪输出,为PLL动态重配置功能提供对DEN信号的响应。

2.8 PLL属性

COMPENSATION(String):SYSTEM_SYNCHRONOUS(Default)、SOURCE_SYNCHRONOUS、INTERNAL、EXTERNAL、DCM2PLL、PLL2DCM

指定输入时钟的PLL相位补偿。

BANDWIDTH(String):HIGH、LOW、OPTIMIZED(Default)

指定影响PLL的抖动、相位裕度和其他特性的PLL编程算法。

CLKOUT[0:5]_DIVIDE(Integer):1(Default) ~ 128

与CLKFBOUT_MULT和DIVCLK_DIVIDE值组合将决定输出频率。

CLKOUT[0:5]_PHASE(Real):-360.0 ~ 360.0 0.0(Default)

以度数偏移量指定相移。

CLKOUT[0:5]_DUTY_CYCLE(Real):0.01 ~ 0.99 0.50(Default)

以百分比形式指定占空比。

CLKFBOUT_MULT(Integer):1(Default) ~ 64

与CLKOUT#_DIVIDE值和DIVCLK_DIVIDE值一起确定输出频率。

DIVCLK_DIVIDE(Integer):1(Default) ~ 52

输入频率分频。

CLKFBOUT_PHASE(Real):0.0(Default) ~ 360.0

指定反馈时钟输出的相位偏移,反馈时钟相移会导致所有输出时钟的负相移。

REF_JITTER(Real):0.000 ~ 0.999 0.100(Default)

允许指定参考时钟上的预期抖动,以便更好地优化PLL性能。如果未知,BANDWIDTH值为OPTIMIZED将会为输入时钟选择最佳参数。如果已知,则应根据输入时钟上预期抖动的UI百分比(最大峰值到峰值)来指定提供的值。

CLKIN1_PERIOD(Real):1.408 ~ 52.630 0.000(Default)

指定PLL CLKIN1输入的输入周期(ns)。 分辨率降至ps。 此信息是强制性的,必须提供。默认值0.000为了强制用户输入正确的值。

CLKIN2_PERIOD(Real):1.408 ~ 52.630 0.000(Default)

指定PLL CLKIN2输入的输入周期(ns)。 分辨率降至ps。 此信息是强制性的,必须提供。默认值0.000为了强制用户输入正确的值。

CLKOUT[0:5]_DESKEW_ADJUST(String):PPC 、NONE(Default)

在PPC440系统中使用PLL时使用的固定延迟。

RESET_ON_LOSS_OF_LOCK(String):FALSE(Default)

必须设置为FALSE。

2.9 PLL CLKIN1和CLKIN2的使用

CLKIN1是PLL的通用输入。 CLKIN2端口用于在工作期间在CLKIN1和CLKIN2之间动态切换,由CLKINSEL端口选择。 如果同时使用CLKIN1和CLKIN2,并且PLL输入时钟由全局时钟引脚驱动,则两个时钟信号引脚的放置有几个限制。 CLKIN1只能来自IBUFG [4-0]。 CLKIN2只能来自IBUFG [9-5]。 此外,CLKIN2必须根据CLKIN1的值映射到特定位置。 这些规则如下:

当PLL输入时钟由全局时钟树(BUFGs)驱动时,两个时钟输入必须连接到相同的时钟输入类型。 用IBUFG驱动一个PLL时钟输入,用BUFG驱动另一个PLL时钟输入是不可能的。

下表列出了Virtex-5 FPGA全局时钟IBUFG引脚与CLKIN1和CLKIN2的关系。

2.10 PLL时钟输入信号

PLL时钟源可以来自多个来源,包括:

IBUFG: 全局时钟输入缓冲器,PLL将补偿此路径的延迟。

BUFGCTRL:内部全局时钟缓冲器,PLL不会补偿此路径的延迟。

IBUF:不建议使用,因为PLL无法补偿一般路由的延迟。 IBUF时钟输入必须在路由到PLL之前路由到BUFG。

DCMOUT:PLL的任何DCM输出都将补偿此路径的延迟。

2.11 计数器控制

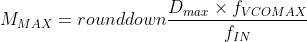

PLL输出计数器使用DIVIDE,DUTY_CYCLE和PHASE的组合提供各种合成时钟。下图说明了计数器设置如何影响计数器输出。

2.12 时钟移位

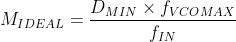

通过在参考或反馈路径中选择八个相位之一来插入延迟,可以移位PLL输出时钟。下图比较了无延迟、延迟插入反馈路径、延迟插入参考路径的情况下的时钟边沿。

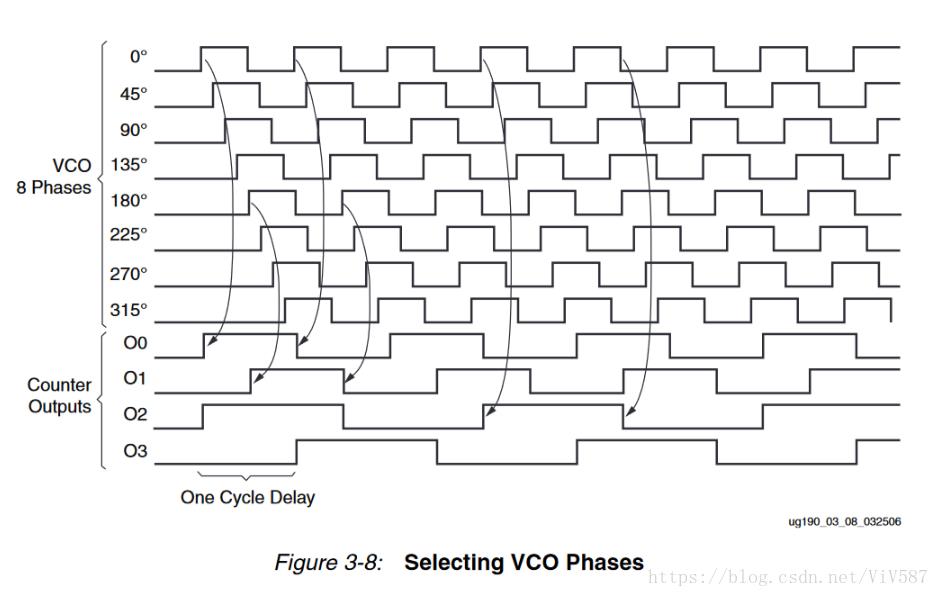

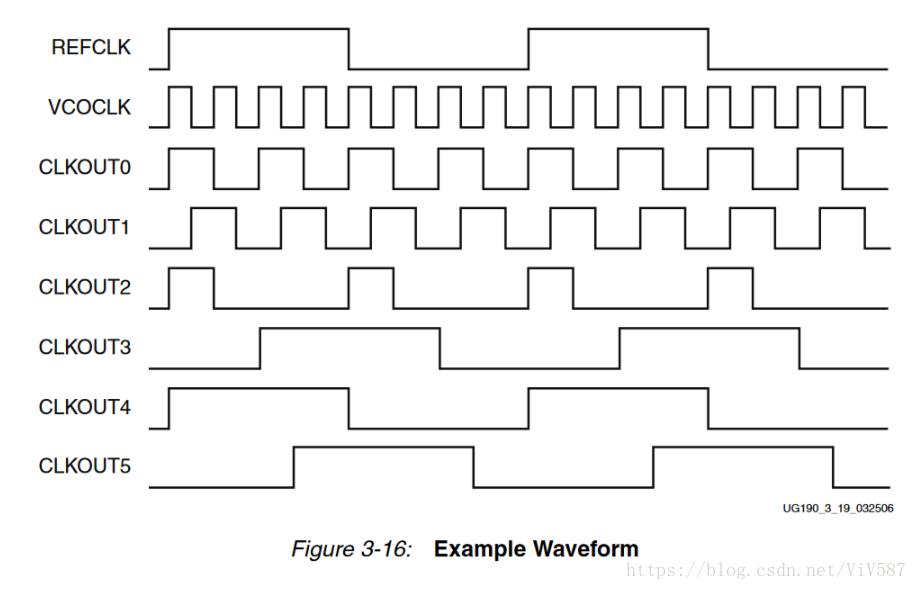

3. 详细的VCO和输出计数器波形

下图显示了8个VCO相位输出和4个不同的计数器输出。

4. 参考时钟切换

PLL参考时钟的动态切换可以使用CLKINSEL引脚,切换是异步完成的。在使用CLKINSEL来切换时钟时,PLL应保持在复位状态,以免出现窄脉冲。如下图:

当输入时钟或反馈时钟丢失时,PLL将输出更低或更高频率的时钟, 频率增加/减少会导致输出时钟频率变为原始配置的六倍。

5. PLL使用模型

这里介绍几种PLL的使用模型。

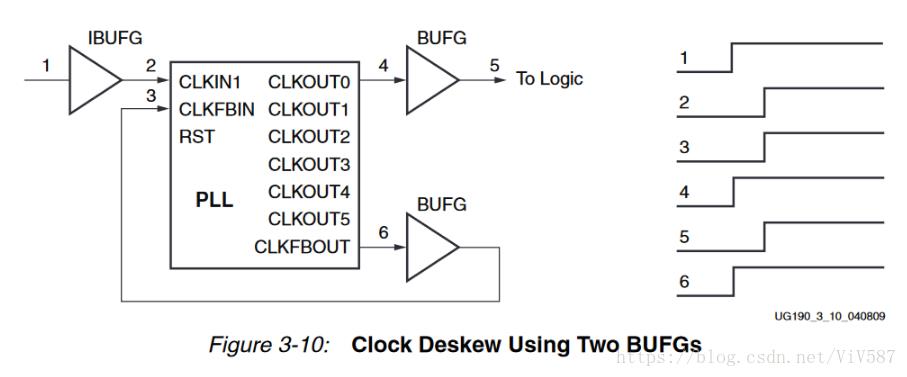

5.1 时钟网络偏移校正(Clock Network Deskew)

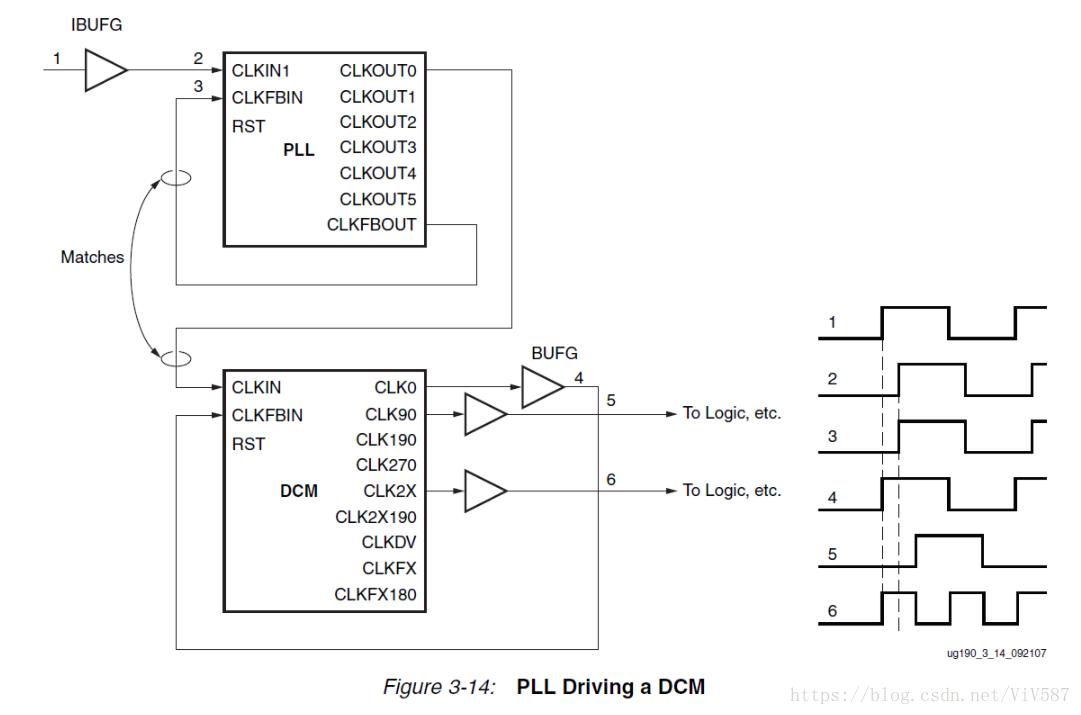

PLL的主要用途之一是用于时钟网络偏移校正。下图显示了此模式下的PLL,相关的时钟波形显示在右侧。其中1、4、6对齐,2、3、5对齐,它们之间延迟了一个BUFG延迟的时间。

反馈的实现有一个限制,即PFD的两个输入频率必须相同,满足以下公式:

5.2 带内部反馈的PLL(PLL with Internal Feedback)

当PLL用作频率合成器或抖动滤波器且PLL输入时钟和PLL输出时钟之间不需要相位关系时,PLL反馈可以在PLL内部。此时PLL的性能将会增加。如下图:

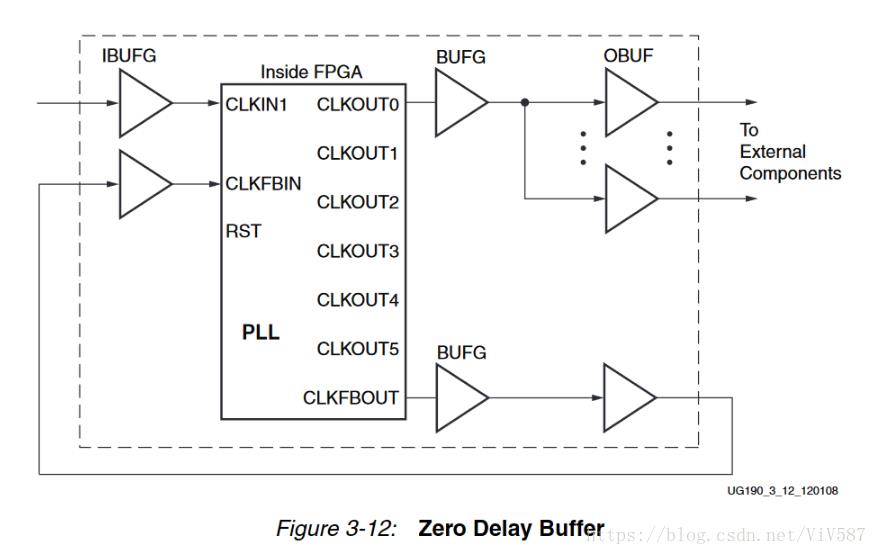

5.3 零延迟缓冲(Zero Delay Buffer)

PLL还可用于生成零延迟缓冲时钟。如下图:

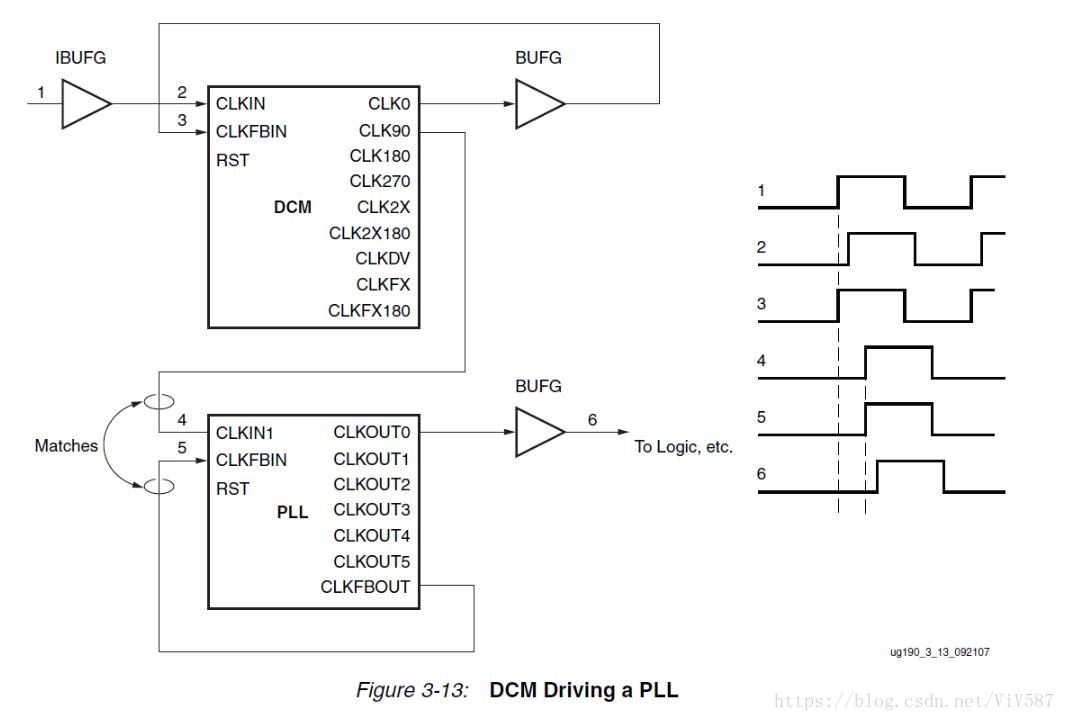

5.4 DCM驱动PLL

DCM能够生成精确的相移时钟,但是DCM无法降低参考时钟的抖动,PLL可以降低一个DCM输出时钟的抖动。当DCM输出用于直接驱动PLL时,DCM和PLL必须位于同一个CMT块内,这是首选实现,因为它在本地专用路由上产生最小量的噪声。也可以通过将DCM连接到BUFG然后连接到PLL的CLKIN输入来建立连接。如下图,相关波形在右侧。

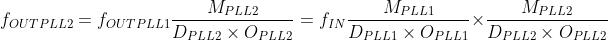

5.5 PLL驱动DCM

减少时钟抖动的第二个选择是使用PLL驱动DCM,在输入时钟抖动进入DCM之前清除,这将改善所有DCM输出的抖动,但DCM自身产生的抖动仍将传递到时钟输出。PLL和DCM应位于同一CMT块中,因为PLL和DCM之间存在专用资源以支持零延迟模式。当PLL和DCM不在同一个CMT块中时,需通过BUFG来阻止歪斜的可能。一个PLL可以驱动多个DCM。

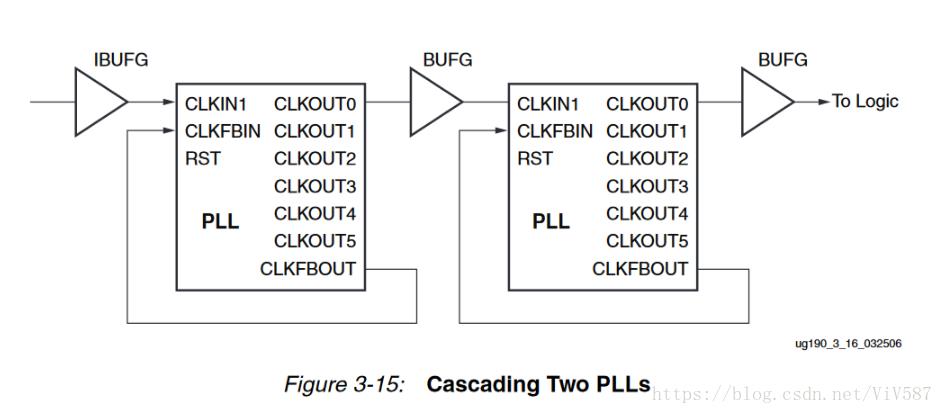

5.6 PLL和PLL连接

PLL可以级联,以产生更大范围的时钟频率。级联PLL需将第一个PLL的输出连接到BUFG,再连接到第二个PLL的CLKIN引脚。 此路径提供最低的设备抖动。第二PLL的输出时钟与输入时钟之间的相位关系是不确定的。如下图:

6. 应用指南

PLL可以在很大的范围内产生可配置输出集,而DCM只具有基于参考时钟的固定数量的预定输出,但当应用需要精细相移或动态可变相移时,DCM可能是更好的解决方案。

PLL应用示例:

CLKOUT0_PHASE = 0; CLKOUT0_DUTY_CYCLE = 0.5; CLKOUT0_DIVIDE = 2;

CLKOUT1_PHASE = 90; CLKOUT1_DUTY_CYCLE = 0.5; CLKOUT1_DIVIDE = 2;

CLKOUT2_PHASE = 0; CLKOUT2_DUTY_CYCLE = 0.25; CLKOUT2_DIVIDE = 4;

CLKOUT3_PHASE = 90; CLKOUT3_DUTY_CYCLE = 0.5; CLKOUT3_DIVIDE = 8;

CLKOUT4_PHASE = 0; CLKOUT4_DUTY_CYCLE = 0.5; CLKOUT4_DIVIDE = 8;

CLKOUT5_PHASE = 135; CLKOUT5_DUTY_CYCLE = 0.5; CLKOUT5_DIVIDE = 8;

CLKFBOUT_PHASE = 0; CLKFBOUT_MULT = 8;

DIVCLK_DIVIDE = 1;

CLKIN1_PERIOD = 10.0;

以上是关于Xilinx PLL(Virtex-5)的主要内容,如果未能解决你的问题,请参考以下文章

安装xilinx ise后,会出现多个应用程序比如vivado,vivado HLS, xilin

xilinx的Spartan 6系列的PLL的DRP功能的IP核找不到

[Xilinx]Modelsim独立仿真Vivado生成的PLL核

[从零开始学习FPGA编程-53]:高阶篇 - 基于IP核的FPGA开发-PLL锁相环IP核的原理与配置(Xilinx)