xilinx fpga 上电配置后 pll的锁相状态

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了xilinx fpga 上电配置后 pll的锁相状态相关的知识,希望对你有一定的参考价值。

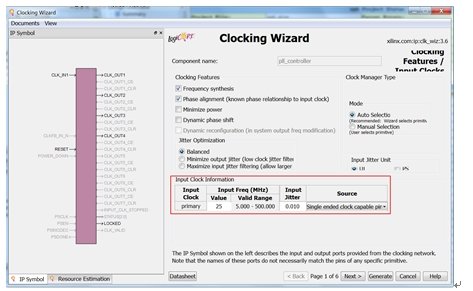

参考技术A 如图所示,在弹出的PLL配置页面Page1中,主要设置“Input Clock Information”下的输入时钟频率,这里我们在“Value”下输入“25”MHz。其他的配置通常使用默认即可,大家也可以点击右下角的“Datasheet”查看文档,确认相关设置的具体含义。

在page2中,如图所示,我们设置CLK_OUT1的输出时钟频率为12.5(单位:MHz),同时勾选CLK_OUT2、CLK_OUT3和CLK_OUT4,并且分别设置它们的频率为25、50和100(MHz)。

Page3中,如图所示,勾选“RESET”和“LOCKED”这两个接口。RESET即整个PLL的复位信号,LOCKED则是PLL输出时钟正常工作的指示信号。

完成上面的配置,在Page5中,如图所示,所有相关的配置信息都在此罗列出来了,供review。

与此同时,如图所示,在PLL配置页面的右侧,所有可用于连接到我们的逻辑中的信号接口也都一览无余,非常直观。

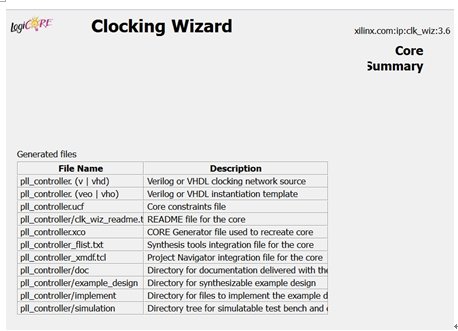

最后,在page6中,如图所示,PLL模块配置完成后,将会生成的所有相关源文件都罗列出来了。

我们可以点击PLL配置页面右下角的“Generate”生成当前配置。

如图所示,在“Design à Implementation”中出现了刚刚配置的pll_controller模块,选中它,然后在“Processes”中,我们可以双击“View HDL Instantiation Template”打开PLL文件的例化模板。

如图所示,这边是pll_controller的例化模板,我们把它复制到我们的设计模块中,然后更改“()”内的信号名称,和我们的模块信号名称一致。具体请参考设计实例的源代码。

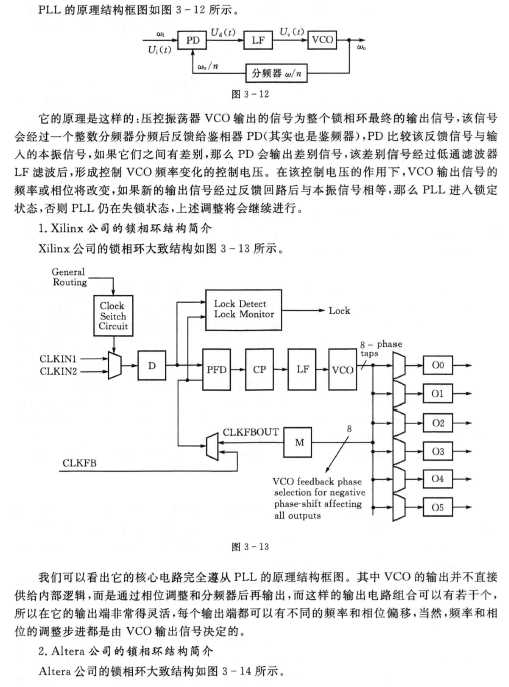

FPGA006_2 优化设计FPGA全局时钟管理模块什么是PLL?

PLL :Phase Locked Loop

中文:锁相环

以上是关于xilinx fpga 上电配置后 pll的锁相状态的主要内容,如果未能解决你的问题,请参考以下文章

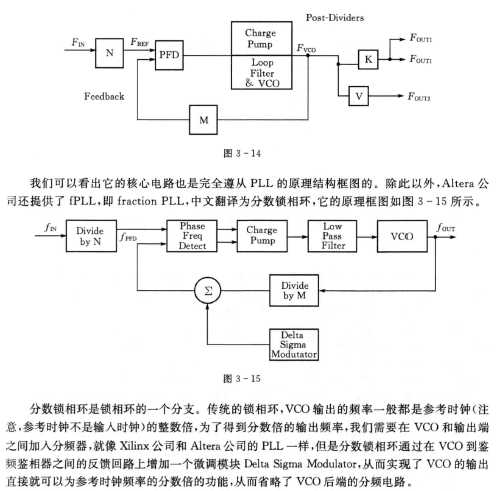

[从零开始学习FPGA编程-54]:高阶篇 - 基于IP核的FPGA开发-PLL锁相环IP核的原理与配置(Altera)