fpga实操训练(锁相环pll)

Posted 嵌入式-老费

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了fpga实操训练(锁相环pll)相关的知识,希望对你有一定的参考价值。

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

锁相环pll是fpga区别于stm32、soc很重要的一个特征。通常来说,输入的晶振一般是25m、50m这样的,不一定能满足功能的开发。这个时候就需要对时钟进行倍频,或者分频处理。fpga上面配置pll非常简单,就算不懂得pll的实现原理,也完全也不影响自己的使用。

为了验证pll有没有成功,我们可以通过led点灯的方法,只通过修改clk0的输出,就可以判断pll是不是真的发挥了作用。

1、准备led_test项目

led_test项目的创建和之前其他fpga测试项目一样,没有什么特别之处。

2、配置pll

首先从IP Catalog中添加ALTPLL,

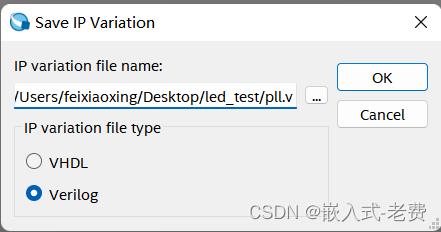

选择ALTPLL之后,单击弹出窗口,保存为pll.v文件,

输入input时钟,我们的时钟是50M,所以这里修改成50,

以上是关于fpga实操训练(锁相环pll)的主要内容,如果未能解决你的问题,请参考以下文章