部分小容量芯片引脚封装共用问题

Posted wchmcu

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了部分小容量芯片引脚封装共用问题相关的知识,希望对你有一定的参考价值。

1、PA1、PA2为外部晶振输入,如果程序内部使用的时外部晶振,单没有外接晶振,芯片将以HSI(8M)运行,会导致延时与外设时序错误。如果需要使用外部晶振,需要关闭PA1、PA2的GPIO功能。具体配置

/* Close PA0-PA1 GPIO function */

RCC->APB2PCENR |= RCC_AFIOEN;

AFIO->PCFR1 |= (1<<15);

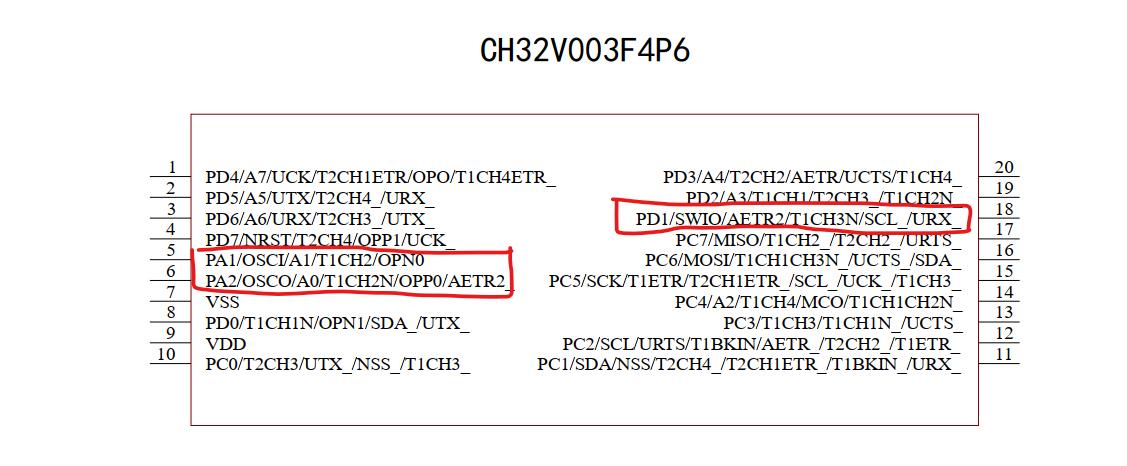

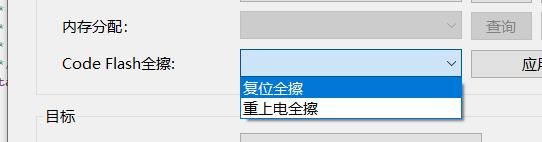

2、PD1单线仿真下载线SWDIO与串口RX等共用,程序中如有使用此引脚将会导致再次下载出现 芯片状态错误 ,此时应使用LINKE-1V2以上版本通过复位全擦或者重上电全擦清空代码方可重新下载。具体操作参照 https://www.wch.cn/bbs/thread-95971-1.html

注 :对于芯片一上电就关闭SWD功能,此功能无效,因为清空代码的功能需要在SWD功能还未关闭时通过SWD引脚输出控制信号。如芯片没有引出BOOT,此时芯片真成砖了。建议代码中有关闭SWD功能的需求时,在之前使用延时几个ms。

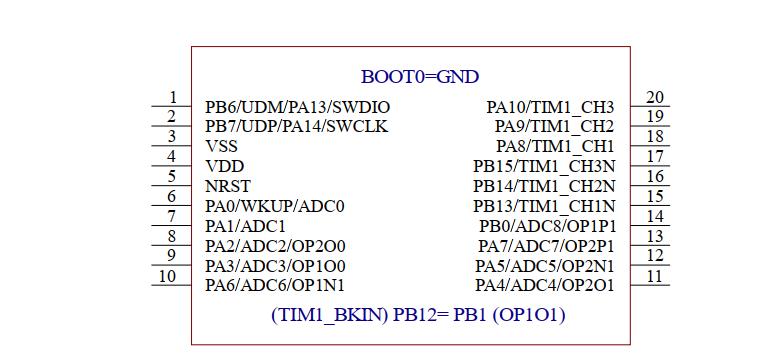

二、CH32V203、以F8P6封装为例:

1、PB6与SWDIO、PB7与SWCLK共用,SWD内部电路引脚SWCLK内部有一个40K的下拉电阻,导致I2C的SDA引脚(PB7)上拉电阻拉不到3.3V(10K上拉此时分压大约2.8V),程序中此时应该通过关闭SWD功能 ,并配置PA13、PA14为开漏输出并置一方可正常,此时USB与PA13 、PA14 引脚上不要外接电路,以免影响I2C通信,同理如要使用USB功能,其他功能不可使用且不接外围电路。

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA|RCC_APB2Periph_AFIO , ENABLE );

GPIO_PinRemapConfig(GPIO_Remap_SWJ_Disable, ENABLE);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_13;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_OD;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init( GPIOA, &GPIO_InitStructure );

GPIO_SetBits(GPIOA, GPIO_Pin_13);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_14;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_OD;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init( GPIOA, &GPIO_InitStructure );

GPIO_SetBits(GPIOA, GPIO_Pin_14);

以上是关于部分小容量芯片引脚封装共用问题的主要内容,如果未能解决你的问题,请参考以下文章