SDRAM简介

Posted 学工科的皮皮志^_^

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了SDRAM简介相关的知识,希望对你有一定的参考价值。

文章目录

前言

了解SDRAM之前我们先了解一下ROM、RAM、DRAM、SRAM和FLASH的一些基础知识

参考博文:ROM、RAM、DRAM、SRAM和FLASH的区别

ROM和RAM指的都是半导体存储器,ROM在系统停止供电的时候仍然可以保持数据,而RAM通常都是在掉电之后就丢失数据,典型的RAM就是计算机的内存。

RAM有两大类,一种称为静态RAM(Static RAM/SRAM),SRAM速度非常快,是目前读写最快的存储设备了,但是它也非常昂贵,所以只在要求很苛刻的地方使用,譬如CPU的一级缓冲,二级缓冲。另一种称为动态RAM(Dynamic RAM/DRAM),DRAM保留数据的时间很短,速度也比SRAM慢,不过它还是比任何的ROM都要快,但从价格上来说DRAM相比SRAM要便宜很多,计算机内存就是DRAM的。

DRAM分为很多种,常见的主要有FPRAM/FastPage、EDORAM、SDRAM、DDR RAM、RDRAM、SGRAM以及WRAM等,这里介绍其中的一种DDR RAM。

DDR RAM(Date-Rate RAM)也称作DDR SDRAM,这种改进型的RAM和SDRAM是基本一样的,不同之处在于它可以在一个时钟读写两次数据,这样就使得数据传输速度加倍了。这是目前电脑中用得最多的内存。在很多高端的显卡上,也配备了高速DDR RAM来提高带宽,这可以大幅度提高3D加速卡的像素渲染能力。

一、内存的工作原理

内存工作原理:

内存是用来存放当前正在使用的(即执行中)的数据和程序,我们平常所提到的计算机的内存指的是动态内存(即DRAM),动态内存中所谓的==“动态”==,指的是当我们将数据写入DRAM后,经过一段时间,数据会丢失,因此需要一个额外设电路进行内存刷新操作。

具体的工作过程是这样的:一个DRAM的存储单元存储的是0还是1取决于电容是否有电荷,有电荷代表1,无电荷代表0。但时间一长,代表1的电容会放电,代表0的电容会吸收电荷,这就是数据丢失的原因;刷新操作定期对电容进行检查,若电量大于满电量的1/2,则认为其代表1,并把电容充满电;若电量小于1/2,则认为其代表0,并把电容放电,藉此来保持数据的连续性。

ROM也有很多种,PROM是可编程的ROM,PROM和EPROM(可擦除可编程ROM)两者区别是,PROM是一次性的,也就是软件灌入后,就无法修改了,这种是早期的产品,现在已经不可能使用了,而EPROM是通过紫外光的照射擦出原先的程序,是一种通用的存储器。另外一种EEPROM是通过电子擦出,价格很高,写入时间很长,写入很慢。

1.1 FLASH

FLASH存储器又称闪存,它结合了ROM和RAM的长处,不仅具备电子可擦除可编程(EEPROM)的性能,还不会断电丢失数据同时可以快速读取数据(NVRAM的优势),U盘和MP3里用的就是这种存储器。在过去的20年里,嵌入式系统一直使用ROM(EPROM)作为它们的存储设备,然而近年来Flash全面代替了ROM(EPROM)在嵌入式系统中的地位,它用作存储Bootloader以及操作系统或者程序代码,或者直接当硬盘使用(U盘)。

目前Flash主要有NOR Flash和NADN Flash。

二、SDRAM内存模组与基本结构

接下来我们回归正题,回到SDRAM,我们平时看到的 SDRAM 都是以模组形式出现,为什么要做成这种形式呢?这首先要接触到两个概念:

物理 Bank 与芯片位宽。

2.1、物理 Bank

传统内存系统为了保证 CPU 的正常工作,必须一次传输完 CPU 在一个传输周期内所需要的数据。而CPU 在一个传输周期能接受的数据容量就是 CPU 数据总线的位宽,单位是 bit(位)。当时控制内存与 CPU之间数据交换的北桥芯片也因此将内存总线的数据位宽等同于 CPU 数据总线的位宽,而这个位宽就称之为物理 Bank(Physical Bank,下文简称 P-Bank)的位宽。所以,那时的内存必须要组织成 P-Bank 来与 CPU打交道。

资格稍老的玩家应该还记得 Pentium 刚上市时, 需要两条 72pin 的 SIMM 才能启动, 因为一条 72pin -SIMM 只能提供 32bit 的位宽,不能满足 Pentium 的 64bit 数据总线的需要。直到 168pin-SDRAM DIMM 上市后,才可以使用一条内存开机。下面将通过芯片位宽的讲述来进一步解释 P-Bank 的概念。 不过要强调一点, P-Bank 是 SDRAM 及以前传统内存家族的特有概念, 在RDRAM 中将以通道 (Channel)取代,而对于像 Intel E7500 那样的并发式多通道 DDR 系统,传统的 P-Bank 概念也不适用。

说了那么多总结就是内存要组成一个和CPU数据总线位宽相同的东西才能和CPU进行数据传输,而由这个由多个内存构成的东西就是物理bank.

2 2、芯片位宽

上文已经讲到SDRAM内存系统必须要组成一个P-Bank的位宽, 才能使CPU正常工作, 那么这个P-Bank位宽怎么得到呢?这就涉及到了内存芯片的结构。

每个内存芯片也有自己的位宽,即每个传输周期能提供的数据量。理论上,完全可以做出一个位宽为64bit 的芯片来满足 P-Bank 的需要,但这对技术的要求很高,在成本和实用性方面也都处于劣势。所以芯片的位宽一般都较小。台式机市场所用的 SDRAM 芯片位宽最高也就是 16bit,常见的则是 8bit。这样,为了组成 P-Bank 所需的位宽,就需要多颗芯片并联工作。对于 16bit 芯片,需要 4 颗(4×16bit=64bit)。对于 8bit 芯片,则就需要 8 颗了。

以上就是芯片位宽、芯片数量与 P-Bank 的关系。P-Bank 其实就是一组内存芯片的集合,这个集合的容量不限,但这个集合的总位宽必须与 CPU 数据位宽相符。随着计算机应用的发展,一个系统只有一个P-Bank 已经不能满足容量的需要。所以,芯片组开始可以支持多个 P-Bank,一次选择一个 P-Bank 工作,这就有了芯片组支持多少(物理)Bank 的说法。而在 Intel 的定义中,则称 P-Bank 为行(Row),比如845G 芯片组支持 4 个行, 也就是说它支持 4 个 P-Bank。 另外, 在一些文档中, 也把 P-Bank 称为 Rank (列) 。

三、 SDRAM的逻辑Bank与芯片容量表示方法

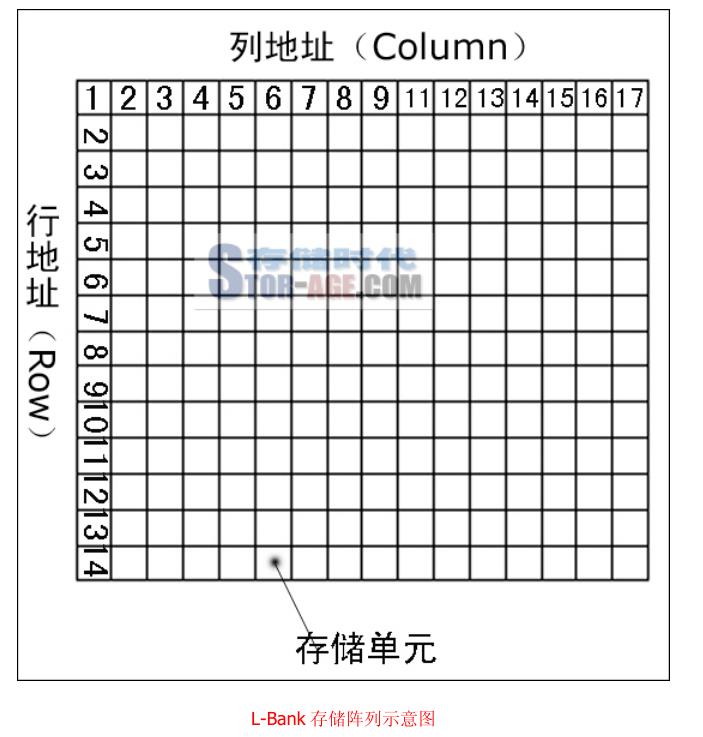

讲完 SDRAM 的外在形式,就该深入了解 SDRAM 的内部结构了。这里主要的概念就是逻辑 Bank。简单地说,SDRAM 的内部是一个存储阵列。因为如果是管道式存储(就如排队买票),就很难做到随机访问

了。 阵列就如同表格一样,将数据“填”进去,你可以把它想象成一张表格。和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理。对于内存,这个单元格可称为存储单元,那么这个表格(存储阵列)叫什么呢?它就是逻

辑 Bank(Logical Bank,下文简称 L-Bank)。

由于技术、成本等原因,不可能只做一个全容量的 L-Bank,而且最重要的是,由于 SDRAM 的工作原理限制,==单一的 L-Bank 将会造成非常严重的寻址冲突,大幅降低内存效率(在后文中将详细讲述)。所以人们在 SDRAM 内部分割成多个 L-Bank,较早以前是两个,目前基本都是 4 个,这也是 SDRAM 规范中的最高 L-Bank 数量。==到了 RDRAM 则最多达到了 32 个,在最新 DDR-Ⅱ的标准中,L-Bank 的数量也提高到了 8 个。

这样,在进行寻址时就要先确定是哪个 L-Bank,然后再在这个选定的 L-Bank 中选择相应的行与列进行寻址。可见对内存的访问,一次只能是一个 L-Bank 工作,而每次与北桥交换的数据就是 L-Bank 存储阵列中一个“存储单元”的容量。在某些厂商的表述中,将 L-Bank 中的存储单元称为 Word(此处代表位的集合而不是字节的集合)。

从前文可知,SDRAM 内存芯片一次传输率的数据量就是芯片位宽,那么这个存储单元的容量就是芯片的位宽(也是 L-Bank 的位宽),但要注意,这种关系也仅对 SDRAM 有效,原因将在下文中说明。

3.1 内存芯片的容量

现在我们应该清楚内存芯片的基本组织结构了。那么内存的容量怎么计算呢?显然,内存芯片的容量就是所有 L-Bank 中的存储单元的容量总合。计算有多少个存储单元和计算表格中的单元数量的方法一样:

==存储单元数量= 行数× 列数(得到一个 L-Bank 的存储单元数量)×L-Bank 的数量 ==

在很多内存产品介绍文档中, 都会用M×W的方式来表示芯片的容量 (或者说是芯片的规格/组织结构) 。M 是该芯片中存储单元的总数,单位是兆(英文简写 M,精确值是 1048576,而不是 1000000),W 代表每个存储单元的容量,也就是 SDRAM 芯片的位宽(Width),单位是 bit。计算出来的芯片容量也是以 bit。

为单位,但用户可以采用除以 8 的方法换算为字节(Byte)。比如 8M×8,这是一个 8bit 位宽芯片,有 8M个存储单元,总容量是 64Mbit(8MB)。

不过,M×W 是最简单的表示方法。下图则是某公司对自己内存芯片的容量表示方法,这可以说是最正规的形式之一。

我们可以计算一下,结果可以发现这三个规格的容量都是 128Mbits,只是由于位宽的变化引起了存储单元的数量变化。从这个例子就也可以看出,在相同的总容量下,位宽可以采用多种不同的设计。

四、SDRAM的引脚与封装

内存芯片要想工作,必须要与内存控制器有所联系,同时对于一个电气元件,电源供应也是必不可少的,而且数据的传输要有一个时钟作为触发参考。因此,SDRAM 在封装时就要留出相应的引脚以供使用。电源与时钟的引脚就不必多说了,现在我们可以想象一下,至少应该有哪些控制引脚呢?

我们从内存寻址的步骤缕下来就基本明白了,从中我们也就能了解内存工作的大体情况。这里需要说明的是,与 DIMM 一样,SDRAM 有着自己的业界设计规范,在一个容量标准下,SDRAM 的引脚/信号标准不能只考虑一种位宽的设计,而是要顾及多种位宽,然后尽量给出一个通用的标准,小位宽的芯片也许会空出一些引脚,但高位宽的芯片可能就全部用上了。不过容量不同时,设计标准也会有所不同,一般的容量越小的芯片所需要的引脚也就越小。

1、 首先,我们知道内存控制器要先确定一个 P-Bank 的芯片集合,然后才对这集合中的芯片进行寻址操作。因此要有一个片选的信号,它一次选择一个 P-Bank 的芯片集(根据位宽的不同,数量也不同)。被选中的芯片将同时接收或读取数据,所以要有一个片选信号。

2、 接下来是对所有被选中的芯片进行统一的L-Bank的寻址, 目前SDRAM中L-Bank的数量最高为 4 个,

所以需要两个L-Bank地址信号(2*2=4)。

3、 最后就是对被选中的芯片进行统一的行/列(存储单元)寻址。地址线数量要根据芯片的组织结构分别设计了。但在相同容量下,行数不变,只有列数会根据位宽的而变化,位宽越大,列数越少,因为所需的存储单元减少了。

4、 找到了存储单元后,被选中的芯片就要进行统一的数据传输,那么肯定要有与位宽相同数量的数据 I/O 通道才行,所以肯定要有相应数量的数据线引脚。

现在我们就基本知道了内存芯片的一些信号引脚,下图就是一个简单的 SDRAM 示意图,大家可以详细看看。

根据 SDRAM 的官方规范,台式机上所用的 SDRAM 在不同容量下的各种位宽封装标准如下:

总结

上文我们已经了解了 SDRAM 所用到的基本信号线路,下面就看看它们在 SDRAM 芯片内部是怎么“布置”的,并从这里开始深入了解内存的基本操作与过程,在这一节中我们将接触到有天书之称的时序图。这里就不深究了(tips:我也看不懂)

上文出处来自:《高手进阶,终极内存技术指南》,大家感兴趣一定看一下,讲的很好。我这里做个简介。

参考博文:

SDRAM详细介绍

相信我,SDRAM真的不难----汇总篇(直达链接)

以上是关于SDRAM简介的主要内容,如果未能解决你的问题,请参考以下文章