问一个关于FPGA配置的问题:书上说,FPGA上电后,nCONFIG管脚被拉低,请问是怎么拉低的?这是一个输入管脚

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了问一个关于FPGA配置的问题:书上说,FPGA上电后,nCONFIG管脚被拉低,请问是怎么拉低的?这是一个输入管脚相关的知识,希望对你有一定的参考价值。

如果是输出管脚就可以理解为是FPGA将其自动拉低的,旦这是一个输入管脚啊,如何做到的呢?

这是一个输入管脚, 但在其外部应该加的有下拉电阻.在整个系统初始上过程中,如CPU/DSP等还没有完成初始化来配置此管脚的时候,该管脚被拉低. 参考技术A 你看的这句话是来ALTERA FPGA的培训教材吧,呵呵。这种下载方式是PS(被动串行),需要FPGA旁外挂个CPLD或微处理器来协作完成,nCONFIG当然作为CPLD的输出,这个时序由CPLD来保证。下载方式分主动,被动和JTAG方式,具体描述你可以看前面一页几种下载方式。 参考技术B 计算机通过Jtag将其拉低,do u understand?

SoC FPGA开发板的FPGA配置数据下载和固化

小梅哥编写,未经许可,严禁用于任何商业用途

2018年7月2日星期一

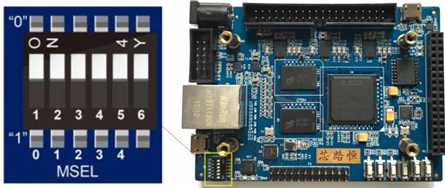

AC501-SoC开发板在上电时能够根据启动设置开关的设置,选择从EPCS或者HPS中启动。具体是通过EPCS还是HPS启动,由一个6位拨码开关通过设置不同的值来决定。

|

配置方式 |

MSEL0~4 |

MSEL5 |

描述 |

|

AS |

5’b10110 |

未使用 |

FPGA从EPCS配置 |

|

FPPx32/ Compression Enabled /Fast POR |

5’b10101 |

未使用 |

FPGA从HPS软件配置,在U-Boot阶段读取存储在SD卡上的rbf文件,然后配置FPGA |

|

FPPx16/ Compression Disable /Fast POR |

5’b11111 |

未使用 |

FPGA从HPS软件配置,在U-Boot阶段读取存储在SD卡上的rbf文件,然后配置FPGA |

AC501-SoC开发板支持两种方式来配置FPGA:

1、使用JTAG编程:此种方式下,FPGA的配置bit流文件直接被下载入Cyclone V SoC FPGA中,下载之后FPGA就会按照该配置文件的信息运行。但是一旦FPGA的供电被关闭了,配置信息也就丢失了。

2、使用AS方式:AS方式全称为主动串行配置(Active Serial configuration),此种方式下FPGA的配置bit流文件会被下载进串行配置器件(EPCS)中,EPCS是一种SPI接口的Nor Flash存储器,即使掉电之后,数据依然存在不会丢失。当开发板下次上电时,如果MSEL设置了从EPCS中启动,则Cyclone V SoC FPGA会自动从EPCS中加载配置数据。

AC501-SoC开发板上设计了标准的IDC3-10的USB Blaster接口,使用USB Blaster,实现PC连接FPGA和HPS,并完成配置bit流的传输以及运行调试。和传统的单芯片纯FPGA方式不同,Cyclone V SoC FPGA上的JTAG链同时连接了FPGA和HPS。因此在使用JTAG配置FPGA时过程也有一定的差别。接下来以一个具体的例子分别讲解配置sof到FPGA中和烧写jic格式的配置文件到EPCS中。

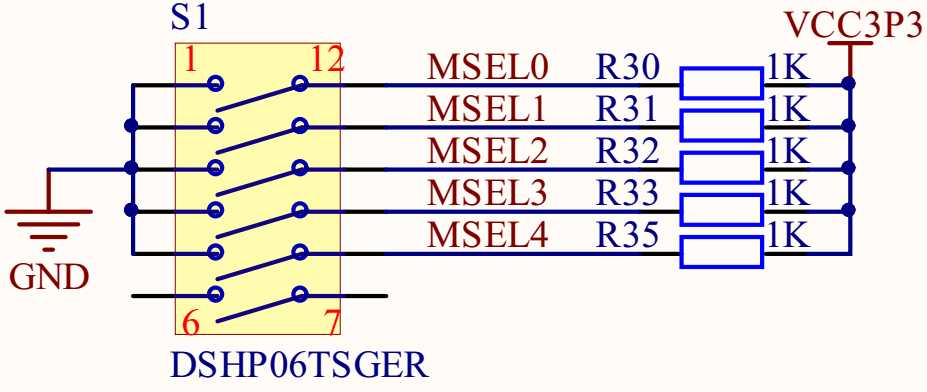

打开一个FPGA工程,如本例以FPGA的LED测试工程“led”为例,在菜单栏中依次点击Tools > Programmer或直接点击Programer图标以打开下载界面。打开之后,软件可能会默认搜索到工程下的led.sof文件并添加进来了,如下图所示。如果没有添加也没有关系,因为添加的内容我们后面操作时也会手动将其删除的。

如果Hardware Setup一栏没有自动找到USB Blaster,则可能需要检查USB Blaster是否正常连接且已经安装好了驱动。如果USB Blaster就绪了,此刻我们直接点击Start来下载添加的sof文件是会失败的,这是因为JTAG链上连接了FPGA和HPS两个设备,下载器不知道需要将文件下载到哪个设备中。

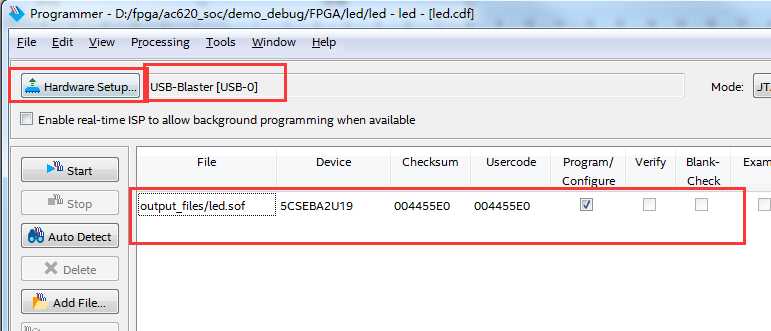

首先点击左侧的Auto Detect按钮,以使用JTAG链检测其连接的设备型号。会提示同一个JTAG ID对应的多个设备,根据我们使用的器件型号为5CSEBA2,因此选择第一个然后OK。

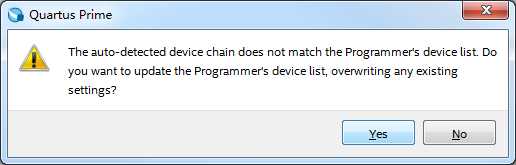

此时软件会提示自动检测到的设备和Programer中已经添加的设备不匹配,询问是否更新,点击YES更新即可,如下图所示。

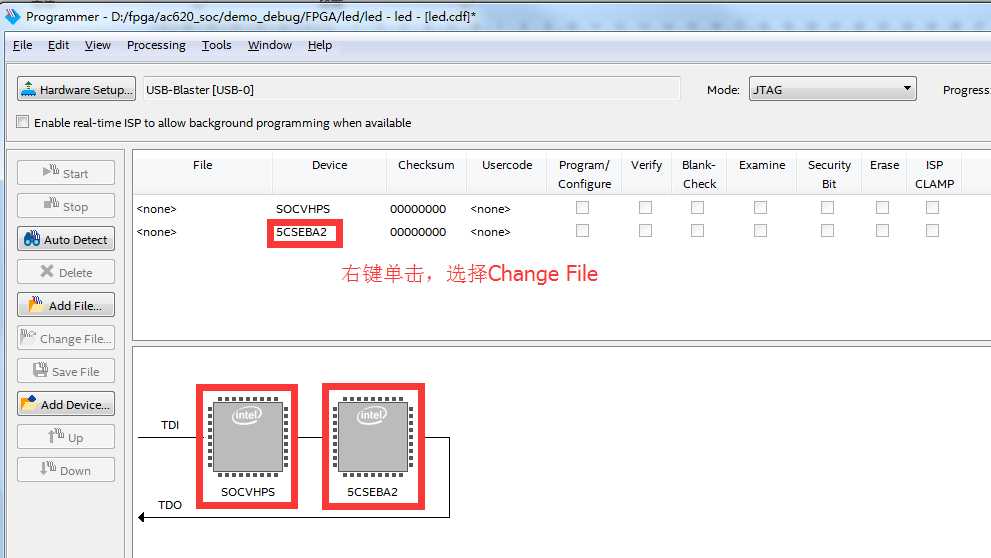

更新完成后可以看到,Programer窗口的下方展示了JTAG链上的设备关系,如下图所示。主要是TDI这个信号线,首先进入SOCVHPS中,然后从SOCVHPS的TDO端口流出,进入FPGA(5CSEBA2)的TDI端口,再从FPGA的TDO端口流出,回到JTAG接口的TDO信号上。选中Device一栏中的5CSEBA2项,右键单击,在弹出的对话框中选择Change File,然后找到sof文件并添加。

点击sof文件对应的Program/Configure复选框以选中,然后点击Start按钮,就可以开始配置sof文件到FPGA中了。配置完成后,可以看到开发板上的两个FPGA_LED灯分别闪烁,其中FPGA_LED0的闪烁频率是FPGA_LED1的两倍。

通过以上方式,完成了sof文件下载到FPGA中的功能。但是此时下载的数据是保存在FPGA的SRAM中的,掉电之后数据就丢失了,为了能够实现FPGA上电自动配置的功能,可以将配置数据bit文件转化为jic文件,烧写到EPCS存储器中,并设置FPGA从EPCS中启动,这样FPGA下次上电时就能够自动从EPCS中加载配置数据了,无需再用JTAG下载。接下来讲解AC501-SoC开发板上所用Cyclone V SoC FPGA器件的jic文件生成以及烧写方式。

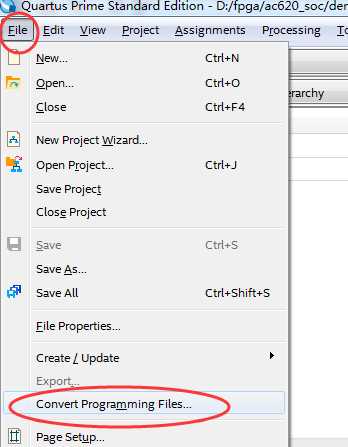

同样还是打开一个设计好的FPGA工程,如led,然后在菜单栏中依次点击File > Convert Programming Files,如下图所示。

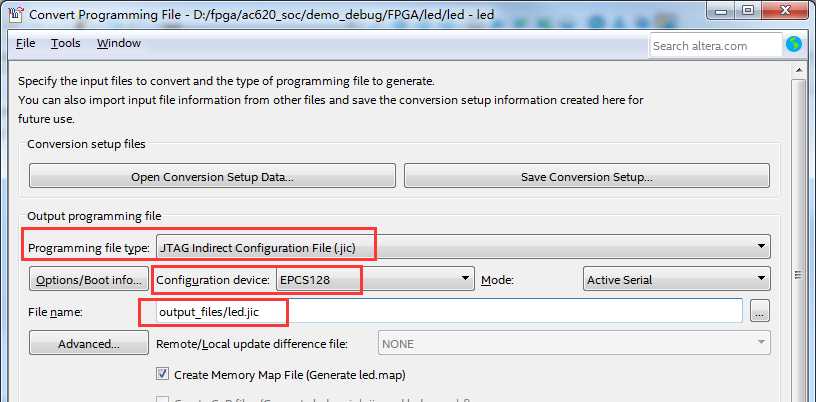

在打开的窗口中,选择Programming file type为JTAG Indirect Configuration File(jic)、Configuration device为EPCS16,注意,是EPCS128,不是EPCQ128,File name设置一个有辨识度的名字,例如led.jic,如下图所示:

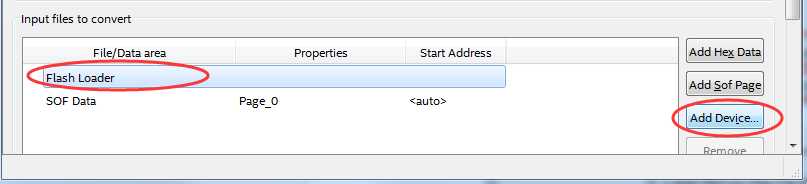

选中下方的Flash Loader,然后点击右侧的Add Device,如下图所示:

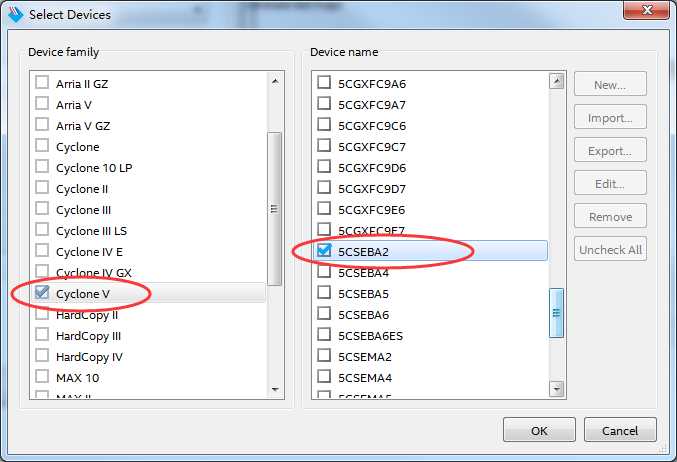

在弹出的对话框中选择AC501-SoC开发板上使用的FPGA器件5CSEBA2,然后点击OK。

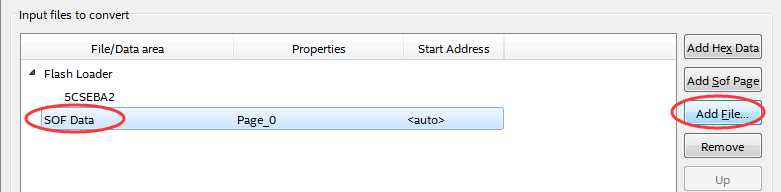

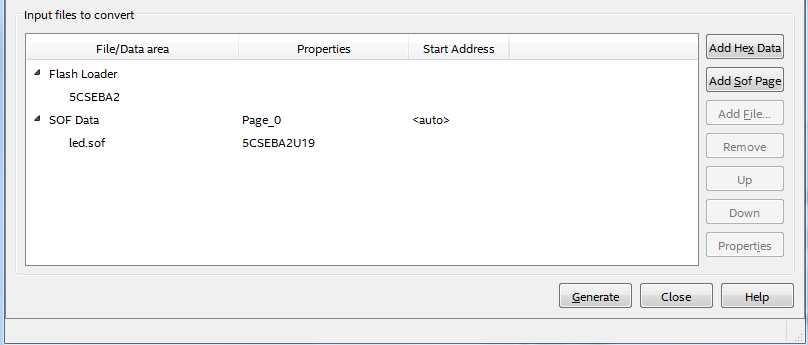

选中SOF Data选项,然后点击右侧的Add File,添加led.sof并确认。

添加好之后,点击右下角的Generate按钮,就能生成jic文件了。

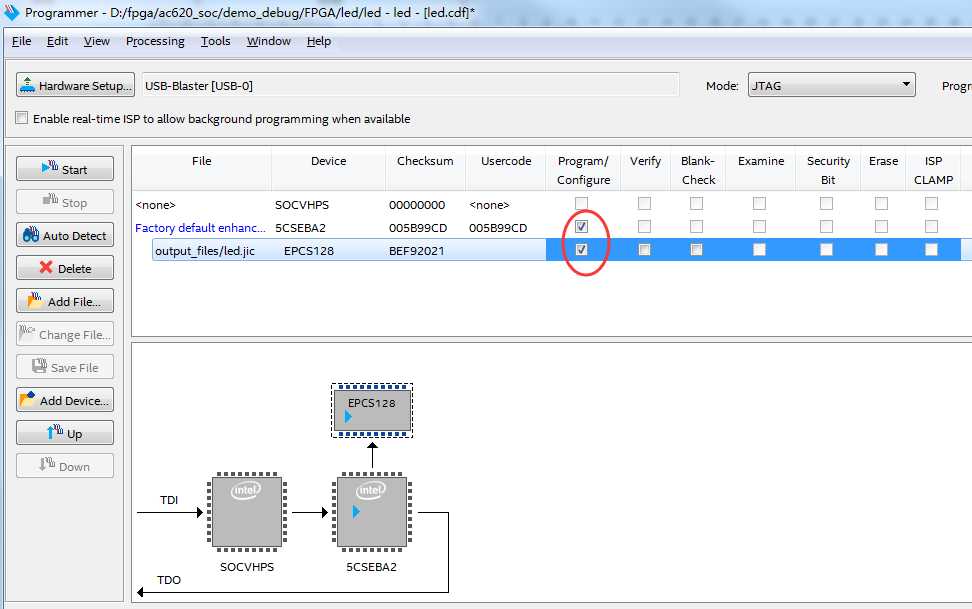

烧写时,依然是先通过Auto Detect检测器件,然后选中FPGA器件右击以Change File,只是添加File的时候,选择刚刚generate好的led.jic文件。勾选Program/Configure选项,然后点击Start,就能够完成烧写到EPCS的功能了。

以上是关于问一个关于FPGA配置的问题:书上说,FPGA上电后,nCONFIG管脚被拉低,请问是怎么拉低的?这是一个输入管脚的主要内容,如果未能解决你的问题,请参考以下文章