三叔学FPGA系列之二:Cyclone V中的POR配置初始化,以及复位

Posted zuilangsanshu

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了三叔学FPGA系列之二:Cyclone V中的POR配置初始化,以及复位相关的知识,希望对你有一定的参考价值。

对于FPGA内部的复位,之前一直比较迷,这两天仔细研究官方数据手册,解开了心中的诸多疑惑,感觉自己又进步了呢.....

一、关于POR(Power-On Reset )

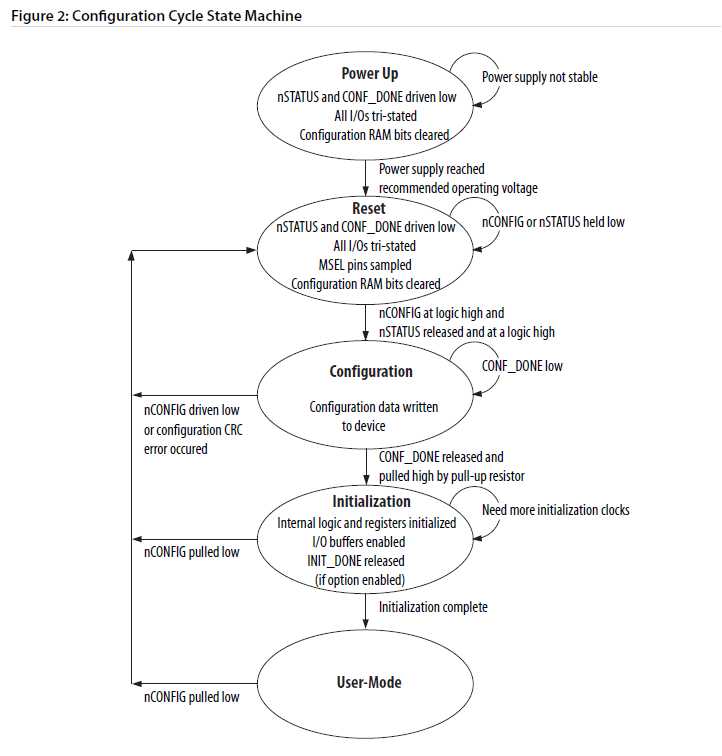

FPGA在上电工作时,会先进入复位模式,将所有RAM位清除,并通过内部弱上拉电阻将用户I/O置为三态。接着依次完成 配置、初始化工作,如果这一切都顺利,就进入用户模式,FPGA会根据用户所编写的时序逻辑开始工作。

二、FPGA上电工作过程详解

从第一条我们知道,FPGA从上电到进入用户模式,会有一个过程。就不放时序图恶心人了,直接上干货,如图1所示。

图1

过程详解

- 上电触发一个复位事件,拉低nCONFIG、nSTATUS、CONF_DONE、INIT_DONE引脚,清除RAM位,三态用户I/O,进入复位;

- 复位过程中,控制逻辑检测所有供电电压,当他们在规定时间达到规定值,并稳定下来,则进入配置,否则就需要用户通过重新拉低nCONFIG足够时间等待电压达标,优秀的电源设计对数字电路是很重要的;

- 复位顺利完成,则依次释放nCONFIG、nSTATUS,让它们被上拉电阻拉高,进入配置,配置模式必须和MSEL[4:0]的设置必须匹配,编写的逻辑电路由quartus生成配置文件,在这个时候烧写到FPGA中,这过程叫做配置,常用的配置方式有JTAG在线模式,和EPCS/EPCQ配置模式;

- 配置成功,则释放CONF_DONE,进入初始化,初始化是按照用户意图将各寄存器置位成预期值;

- 初始化完成,则释放INIT_DONE,进入用户模式,系统按照既定时序开始运转。

*****注意*****

- 电源不稳,后面一切免谈,电源质量好,后面一切应该也顺利;

- 设计硬件电路时,nCONFIG、nSTATUS、CONF_DONE必须上拉,因为初始化完成就万事大吉了,所以INIT_DONE不用管,配置完成后当做普通I/O用;

- MSEL[4:0]设置;

- 设计硬件电路时,要注意配置FLASH和FPGA连接,以及JTAG端口的设计,硬件错了就白瞎;

三、关于FPGA的复位

如前所述,我们已经知道,每次上电工作,FPGA必定进行复位、初始化等操作。所以理论上,后续工作工程中,FPGA是不需要复位的,尤其是全局复位。但是,一方面为了保险起见应该进行局部复位和寄存器初始化(在时序过程中的任意时刻赋值),保证寄存器中的值是我们期望的值,而且某些IP核在工作前也必须复位;另一方面,电路中难免出现亚稳态等,使系统工作异常,这就需要形成一种机制,触发一个复位事件,使系统进入 “复位—>配置—>初始化—>用户模式” 这一过程。

所以有:

- 在 “三叔学FPGA系列之一:Cyclone V中的时钟资源” 一文中一提到,全局时钟布线资源通常非常有限,而全局复位用的也是全局时钟的布线资源,所以能不用全局复位尽量别用,用局部复位就行了,也就是不要在所有always中都用同一个rst_n,可以通过内部逻辑生成多个局部复位信号rstn0,rstn1,rstn2.....

- 在硬件电路设计时,Cyclone V以前的FPGA都有RESET引脚,但设计手册中别没有说这个引脚一定要用作复位,可以当做普通I/O用,在Cyclone V中RESET引脚被取消了。我的理解是:RESET引脚的作用有两点,一是为了在系统运行过程中出现异常时,可以手动按钮之类的触发一个复位事件,使系统复位;二是采用电容延时的方式,强制增加上电复位时间,确保复位成功。当上诉两方面都没有太大必要的情况下,RESET引脚就没什么用了,所以Intel牛B,在Cyclone V中直接去掉RESET引脚(个人猜想,未到技术区求证);

- 再次说明,RESET≠全局复位,实现全局复位有一万种方法,比如通过内部逻辑,或者通过matlab控制串口等等;

- 关于是否使用全局复位,网上众说纷纭,Intel也没有官方说法。我的理解是,看个人的系统情况。比如:全局时钟本来就紧张,那么就pass全局复位,用局部复位,反之资源充足,用全局复位。

四、验证后再来更新

关于第三节的内容,很多都是我个人的猜想,但是也是参考了官方手册,以及个人项目开发中的经验,准确率十之八九,后续验证后再来更新。

以上是关于三叔学FPGA系列之二:Cyclone V中的POR配置初始化,以及复位的主要内容,如果未能解决你的问题,请参考以下文章