英伟达用AI设计GPU:最新H100已经用上,比传统EDA减少25%芯片面积

Posted QbitAl

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了英伟达用AI设计GPU:最新H100已经用上,比传统EDA减少25%芯片面积相关的知识,希望对你有一定的参考价值。

白交 发自 凹非寺

量子位 | 公众号 QbitAI

英伟达终于揭晓:

H100竟有近13000条电路,是AI设计的?!

在最新论文中,他们介绍了如何用深度强化学习agent设计电路的方法。

据研究人员称,这种方法还属业内首次。

值得一提的是,这篇文章包含参考文献在内,仅有短短6页。

不少网友表示,太酷了!

靠玩游戏来学习构建电路架

随着摩尔定律变慢,开发其他技术来提高芯片性能变得愈发重要。

设计更小、更快、功耗更低的算术电路,就是其中的方式之一。

基于这样的背景,研究人员提出了PrefixRL——用深度强化学习优化并行前缀电路。

据研究人员介绍,他们不仅证明了AI可以从头开始设计电路,而且比EDA工具设计得更小、更快。

最新英伟达Hopper架构就拥有13000个AI设计电路的实例。

来具体看看这项研究。

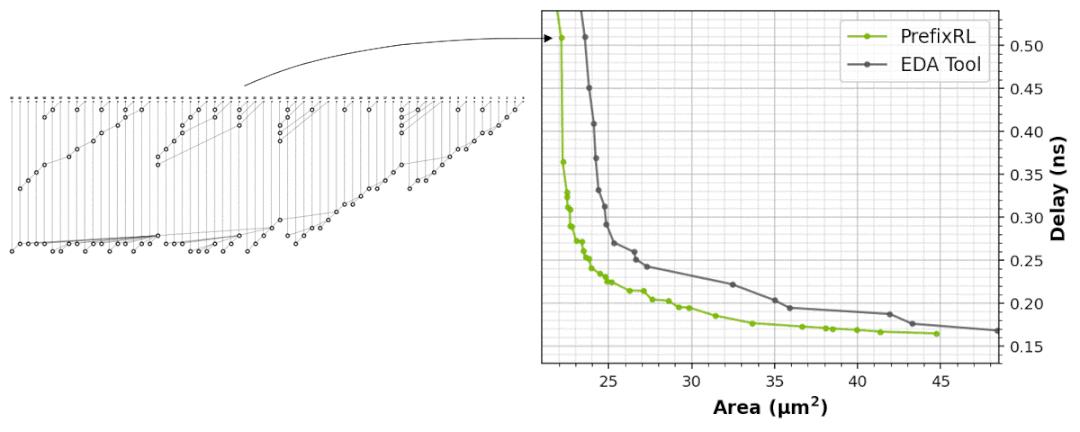

本文主要研究了一种流行的并行前缀电路,着重讨论了电路的两大特性:电路面积和延迟。

已有的优化基本思路,是使用电路发生器将前缀图形转换为带有导线和逻辑门的电路,再用物理综合工具进一步优化。

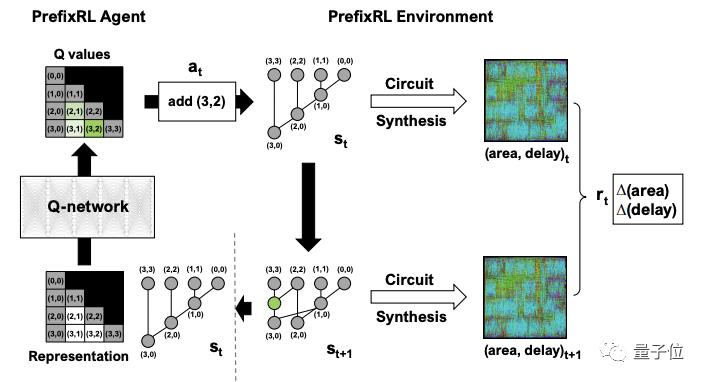

他们将算术电路设计看作是一个强化学习任务,训练一个agent来优化两大特性。

对于前缀电路,还设计了一个环境。

在这个环境中agent玩构建电路架构(前缀图形)的游戏,可以从中添加or删除节点,会因为电路面积最小化和低延迟而获得奖励。

研究人员使用Q-Learning算法来训练agent。

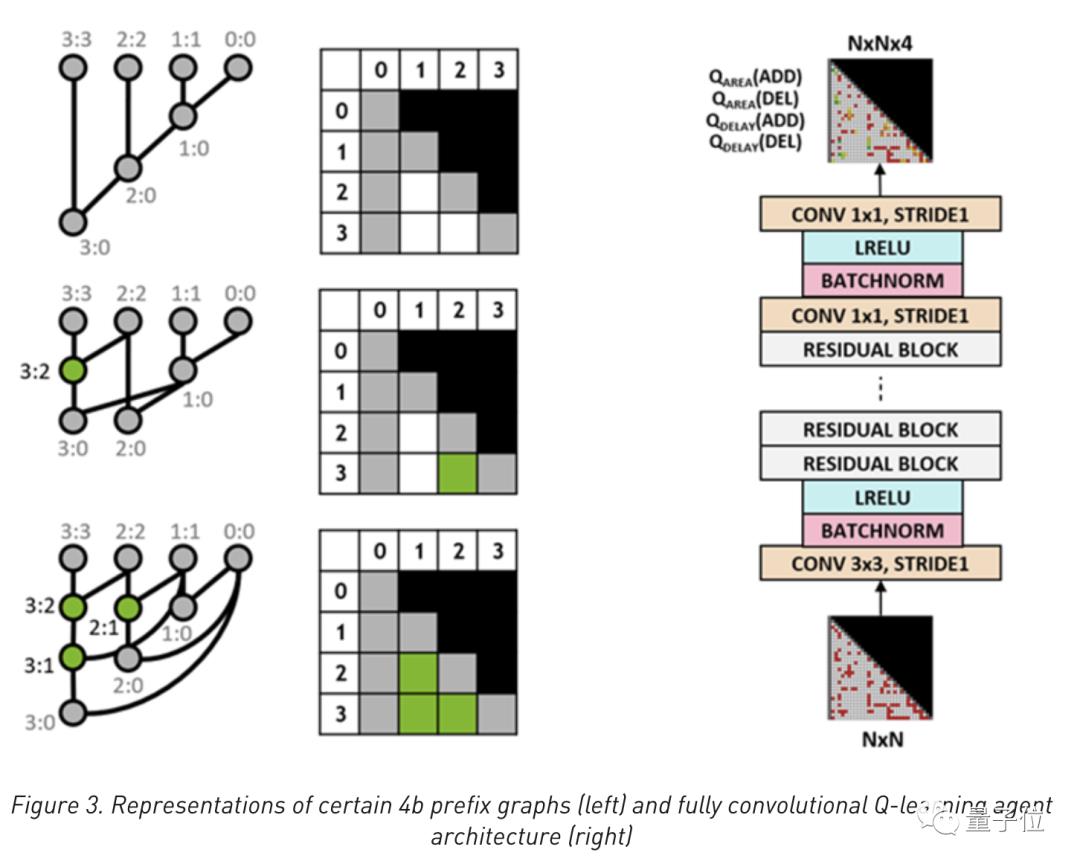

首先将前缀图表示成网格,网格中的每个元素都映射到电路中的节点。

输入和输出均为网格,只不过输入网格中的每个元素表示节点是否存在,输出每个元素则表示用于添加或删除节点的Q值。

在实际训练中,PrefixRL是一项计算要求很高的任务:物理模拟每个GPU需要256个CPU,训练64b用例花费超32000个GPU小时。

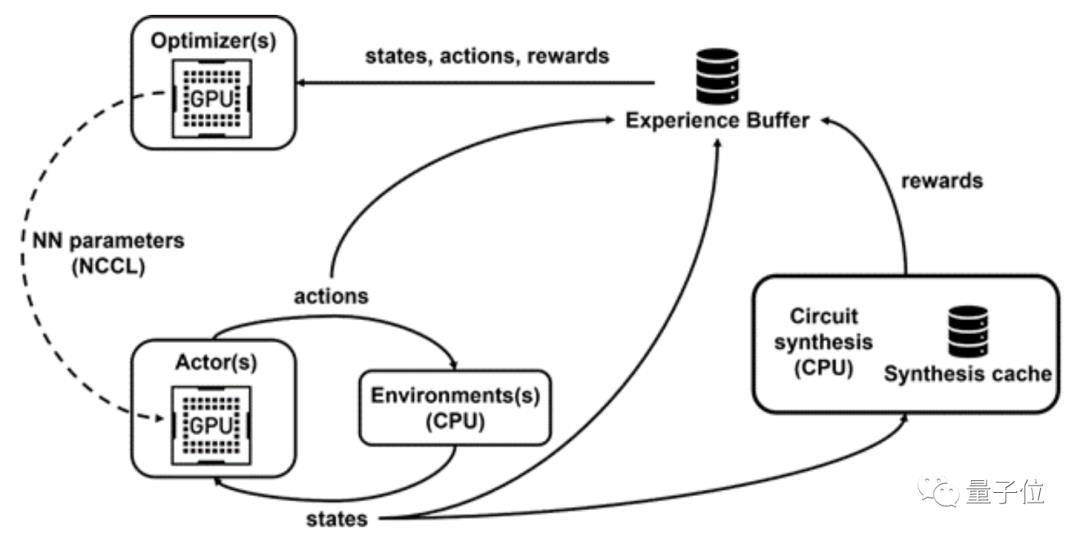

为此,研究人员还开发了个分布式强化学习训练平台Raptor。

结果显示,在相同延迟、效能下PrefixRL加法器面积比EDA工具加法器面积减少了25%。

研究团队

本次研究来自英伟达应用深度学习研究小组。

他们希望这个方法有希望让AI应用到实际电路设计问题当中去。

近年来,AI设计芯片这件事儿很多科技公司都已经在展开。

最典型如谷歌,去年6月在Nature上发表了一篇文章:A graph placement methodology for fast chip design。

文中表示,AI能在6个小时内生成芯片设计图,而且比人类设计得更好。

还有像三星、新思、cadence等企业也都有相应的解决方案。

前阵子在英伟达GTC大会上,首席科学家、计算机架构大师Bill Dally就分享了AI在芯片设计上的几种应用。

包括预测电压降、预测寄生参数、布局布线、自动化标准单元迁移。

不过,即便进展频频,也有不少质疑的声音出现,比如,设计能力跟人类比还差点。

对于AI设计芯片这事儿,你怎么看?

参考链接:

[1]https://developer.nvidia.com/blog/designing-arithmetic-circuits-with-deep-reinforcement-learning/

[2]https://arxiv.org/pdf/2205.07000.pdf

[3]https://twitter.com/rjrshr/status/1545446397759016962

[4]https://www.hpcwire.com/2022/04/18/nvidia-rd-chief-on-how-ai-is-improving-chip-design/

以上是关于英伟达用AI设计GPU:最新H100已经用上,比传统EDA减少25%芯片面积的主要内容,如果未能解决你的问题,请参考以下文章

英伟达用AI给自家纪录片配音,情绪节奏稳稳拿捏,不说根本听不出来

未来诺贝尔奖得颁给AI?英伟达Hopper H100 性能更新/华为造车即将来袭 | 一周AI新鲜事...