ICC中进行P&R后导出网表并导入Cadence中进行仿真的流程(转)

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ICC中进行P&R后导出网表并导入Cadence中进行仿真的流程(转)相关的知识,希望对你有一定的参考价值。

参考技术A 在ICC中输出门级网表,记得 write_verilog 的时候加 -pg 选项,并且在 write_verilog 之前加 hdl verilog -hierachy ,使得生成的网表层次关系正确。使用 V2LVS 命令将门级网表转换成SPICE网表, V2LVS 要加 -i 的选项,使得生成的网表PIN符合SPICE规范。生成后的网表最好去掉最前面的“ .include... ”,把SPICE网表库直接拷贝添加到刚生成的SPICE网表中去,这样在第3步中进行导入的时候,reference library可以直接写PDK的管子模型库。

将第2步产生的Spice网表在Cadence中用 CDL import 的方式导入,导入后,给顶层模块创建完Symbol,就可以调用其搭建testbench然后在Analog Enviroment中使用 Spectre/Ultrasim 进行仿真了。

三原理图生成网表并导入PCB

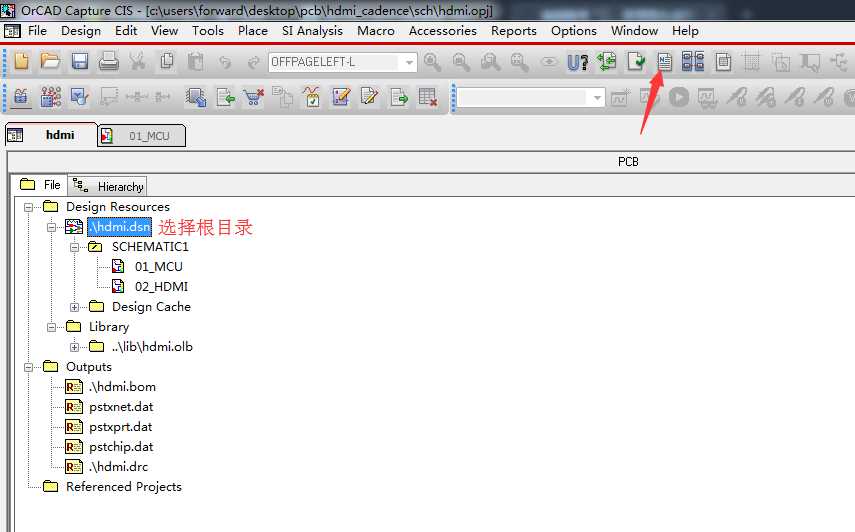

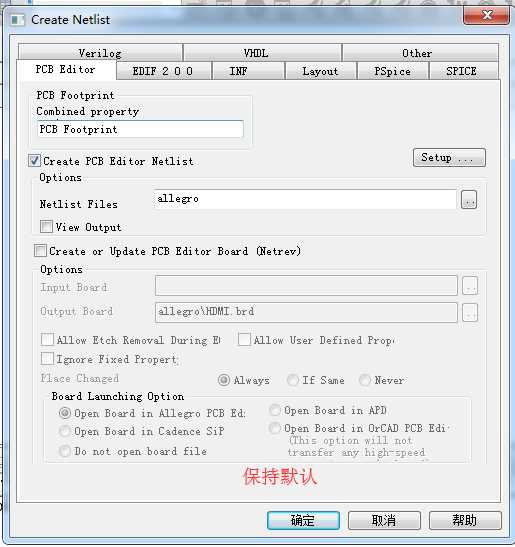

1.生成网表

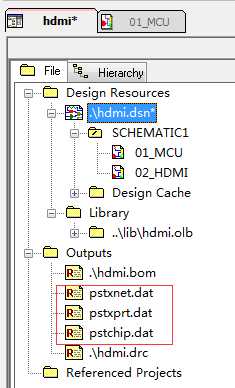

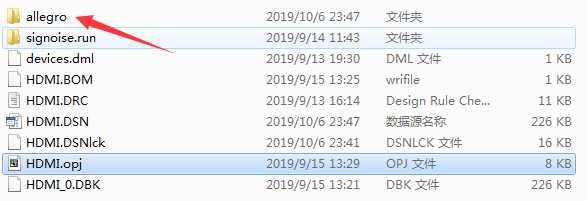

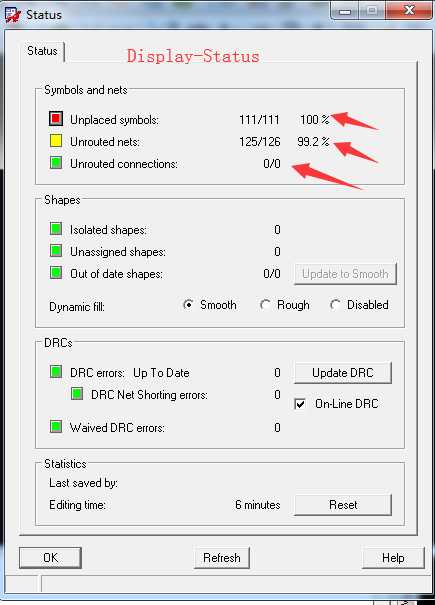

2.成功标志

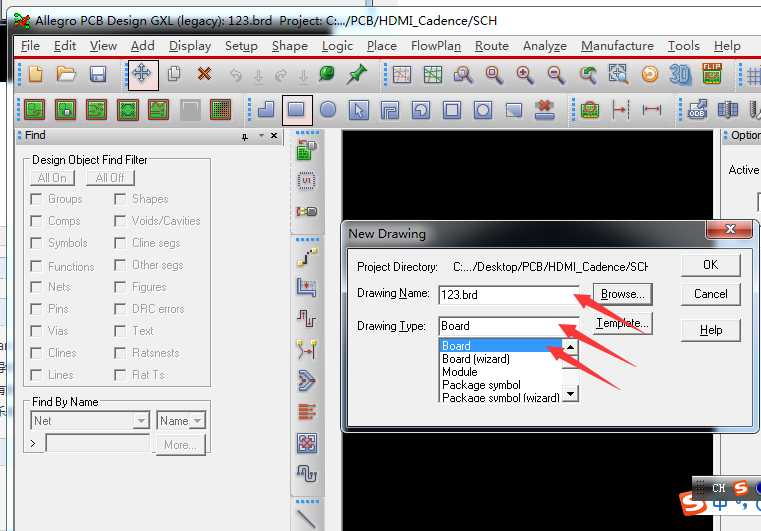

3.新建PCB文件

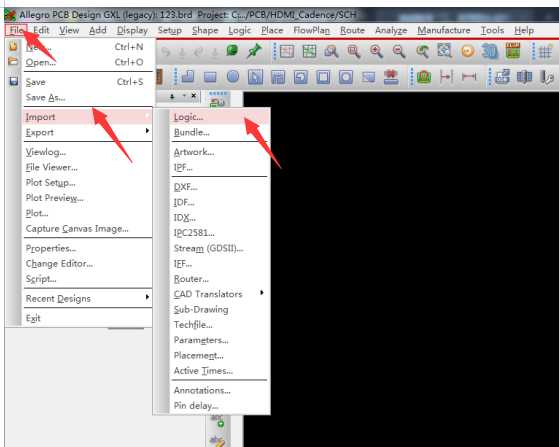

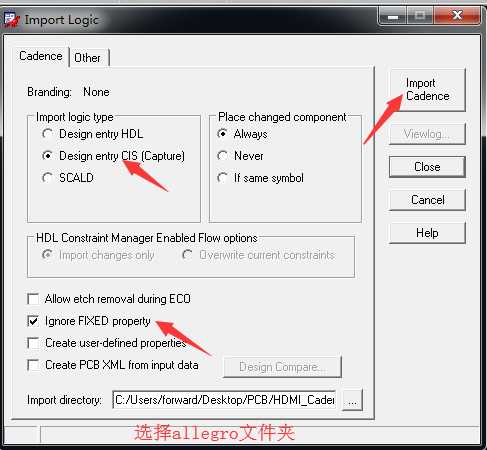

4.导入网表至PCB

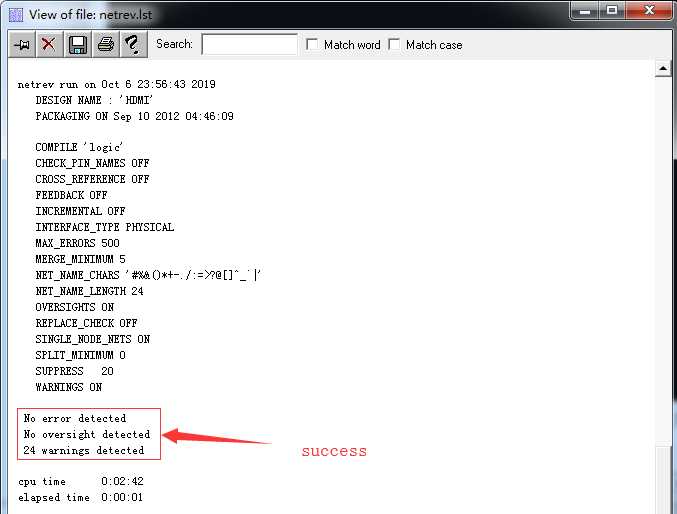

5.导入网表成功标志

以上是关于ICC中进行P&R后导出网表并导入Cadence中进行仿真的流程(转)的主要内容,如果未能解决你的问题,请参考以下文章