ethercat主站 FPGA高实时带加密实现32轴

Posted 专注DSP+ARM+FPGA

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ethercat主站 FPGA高实时带加密实现32轴相关的知识,希望对你有一定的参考价值。

信迈ethercat主站 FPGA高实时带加密实现32轴

性能优势

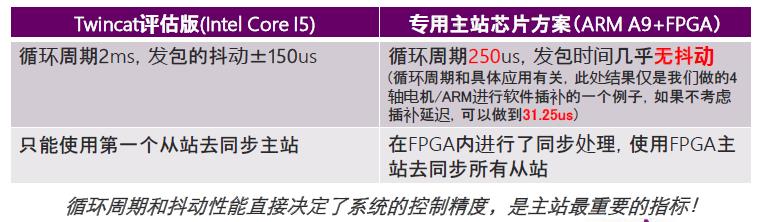

- 更快的循环周期,可以达到31.25us

- 更低的抖动,抖动时间小于0.004us

- 同步性能好,主站和各个从站设备可以达到远小于1us的时钟同步精度(4轴实测50ns)

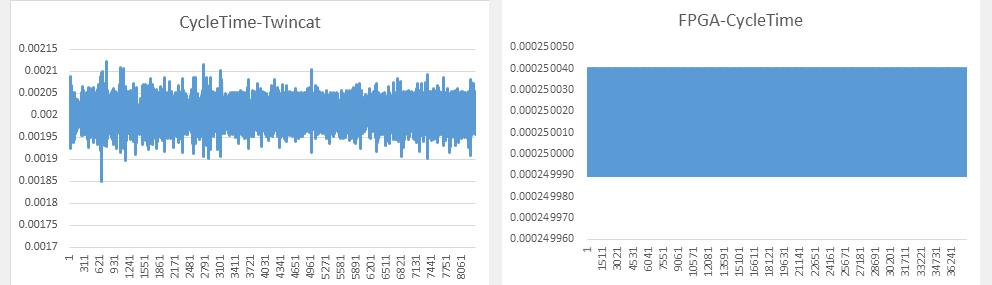

性能对比:

更多性能对比总结:

以上是关于ethercat主站 FPGA高实时带加密实现32轴的主要内容,如果未能解决你的问题,请参考以下文章

基于 ARM + FPGA 的 EtherCAT 主站设计及实现

基于linux+xenomai实时系统Ethercat主站PCIE加速卡

基于 FPGA verilog 的 Ethercat 主站工程代码

基于ZYNQAM5728AM5708AM437xAM335xSTM32+FPGA等平台提供了开源EtherCAT主站IgH案例