NXP(I.MX6uLL)DDR3实验——DDR3重要时间参数时钟配置与原理图简析

Posted 行稳方能走远

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了NXP(I.MX6uLL)DDR3实验——DDR3重要时间参数时钟配置与原理图简析相关的知识,希望对你有一定的参考价值。

DDR3 关键时间参数

大家在购买DDR3 内存的时候通常会重点观察几个常用的时间参数:

1、传输速率

比如1066MT/S、1600MT/S、1866MT/S 等,这个是首要考虑的,因为这个决定了DDR3 内存的最高传输速率。

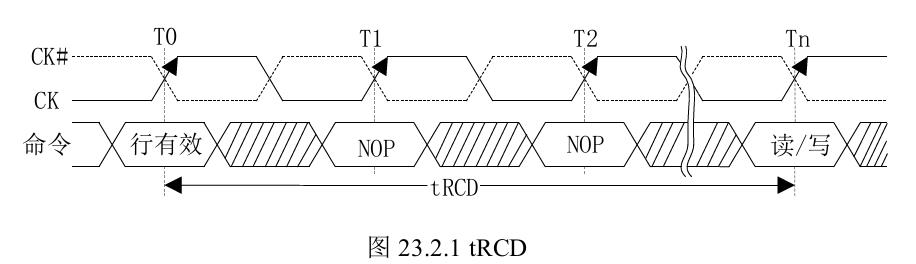

2、tRCD 参数

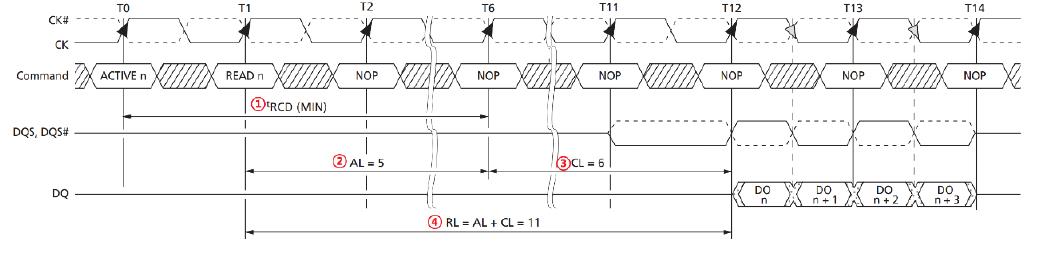

tRCD 全称是RAS-to-CAS Delay,也就是行寻址到列寻址之间的延迟。DDR 的寻址流程是先指定BANK 地址,然后再指定行地址,最后指定列地址确定最终要寻址的单元。BANK 地址和行地址是同时发出的,这个命令叫做“行激活”(Row Active)。行激活以后就发送列地址和具体的操作命令(读还是写),这两个是同时发出的,因此一般也用“读/写命令”表示列寻址。在行有效(行激活)到读写命令发出的这段时间间隔叫做tRCD,如图23.2.1 所示:

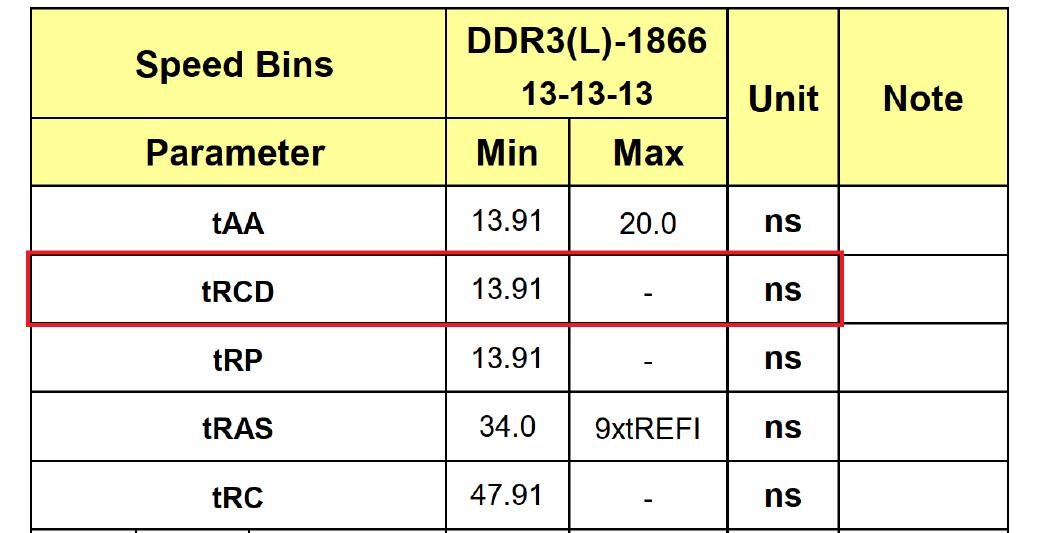

一般DDR3 数据手册中都会给出tRCD 的时间值,比如正点原子所使用的

NT5CC256M16EP-EK 这个DDR3,tRCD 参数如图23.2.2 所示:

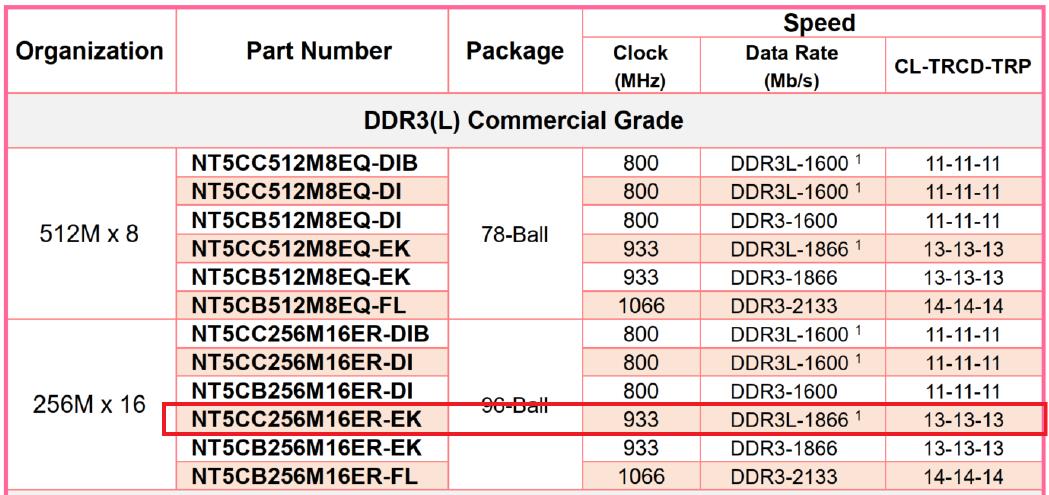

从图23.2.2 可以看出,tRCD 为13.91ns,这个我们在初始化DDR3 的时候需要配置。有时候大家也会看到“13-13-13”之类的参数,这个是用来描述CL-tRCD-TRP 的,如图23.2.3 所示:

从图23.2.3 可以看出,NT5CC256M16ER-EK 这个DDR3 的CL-TRCD-TRP 时间参数为“13-13-13”。因此tRCD=13,这里的13 不是ns 数,而是CLK 时间数,表示13 个CLK 周期。

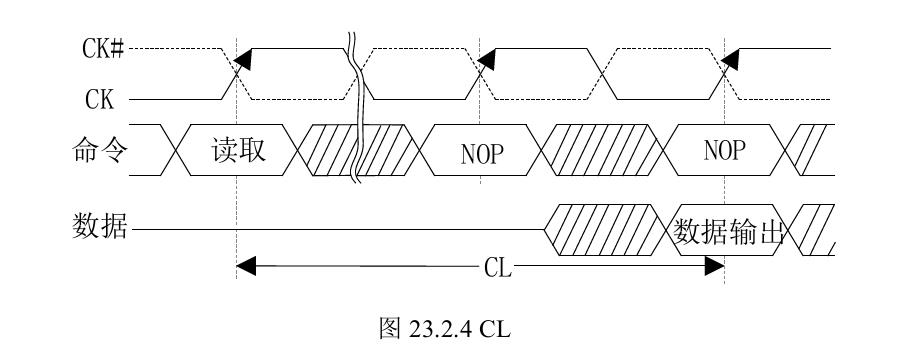

3、CL 参数

当列地址发出以后就会触发数据传输,但是数据从存储单元到内存芯片IO 接口上还需要一段时间,这段时间就是非常著名的CL(CAS Latency),也就是列地址选通潜伏期,如图23.2.4 所示:

CL 参数一般在DDR3 的数据手册中可以找到,比如NT5CC256M16EP-EK 的CL 值就是13个时钟周期,一般tRCD 和CL 大小一样。

4、AL 参数

在DDR 的发展中,提出了一个前置CAS 的概念,目的是为了解决DDR 中的指令冲突,它允许CAS 信号紧随着RAS 发送,相当于将DDR 中的CAS 前置了。但是读/写操作并没有因此提前,依旧要保证足够的延迟/潜伏期,为此引入了AL(Additive Latency),单位也是时钟周期数。AL+CL 组成了RL(Read Latency),从DDR2 开始还引入了写潜伏期WL(Write Latency),WL 表示写命令发出以后到第一笔数据写入的潜伏期。引入AL 以后的读时序如图23.2.5 所示:

图32.2.5 就是镁光DDR3L 的读时序图,我们依次来看一下图中这四部分都是什么内容:

①、tRCD,前面已经说过了。

②、AL。

③、CL。

④、RL 为读潜伏期,RL=AL+CL。

5、tRC 参数

tRC 是两个ACTIVE 命令,或者ACTIVE 命令到REFRESH 命令之间的周期,DDR3L 数据手册会给出这个值,比如NT5CC256M16EP-EK 的tRC 值为47.91ns,参考图23.2.2。

6、tRAS 参数

tRAS 是ACTIVE 命令到PRECHARGE 命令之间的最小时间,DDR3L 的数据手册同样也会给出此参数,NT5CC256M16EP-EK 的tRAS 值为34ns,参考图23.2.2。

I.MX6U MMDC 控制器简介

MMDC 控制器

学过STM32 的同学应该记得,STM32 的FMC 或FSMC 外设用于连接SRAM 或SDRAM,对于I.MX6U 来说也有DDR 内存控制器,否则的话它怎么连接DDR 呢?MMDC 就是I.MX6U的内存控制器,MMDC 是一个多模的DDR 控制器,可以连接16 位宽的DDR3/DDR3L、16 位宽的LPDDR2,MMDC 是一个可配置、高性能的DDR 控制器。MMDC 外设包含一个内核(MMDC_CORE)和PHY(MMDC_PHY),内核和PHY 的功能如下:

MMDC 内核:内核负责通过AXI 接口与系统进行通信、DDR 命令生成、DDR 命令优化、读/写数据路径。

MMDC PHY:PHY 负责时序调整和校准,使用特殊的校准机制以保障数据能够在400MHz被准确捕获。

MMDC 的主要特性如下:

- ①、支持DDR3/DDR3Lx16、支持LPDDR2x16,不支持LPDDR1MDDR 和DDR2。

- ②、支持单片256Mbit~8Gbit 容量的DDR,列地址范围:8-12 位,行地址范围11-16bit。2个片选信号。

- ③、对于DDR3,最大支持8bit 的突发访问。

- ④、对于LPDDR2 最大支持4bit 的突发访问。

- ⑤、MMDC 最大频率为400MHz,因此对应的数据速率为800MT/S。

- ⑥、支持各种校准程序,可以自动或手动运行。支持ZQ 校准外部DDR 设备,ZQ 校准DDR I/O 引脚、校准DDR 驱动能力。

MMDC 控制器信号引脚

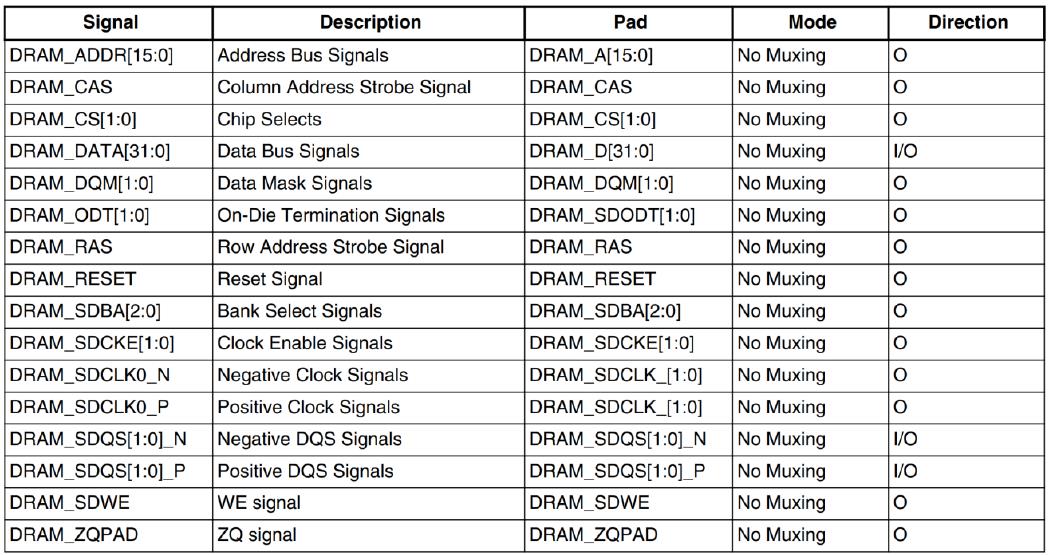

我们在使用STM32 的时候FMC/FSMC 的IO 引脚是带有复用功能的,如果不接SRAM 或SDRAM 的话FMC/FSMC 是可以用作其他外设IO 的。但是,对于DDR 接口就不一样了,因为DDR 对于硬件要求非常严格,因此DDR 的引脚都是独立的,一般没有复用功能,只做为DDR引脚使用。I.MX6U 也有专用的DDR 引脚,如图23.3.2.1 所示:

由于图23.3.2.1 中的引脚是DDR 专属的,因此就不存在所谓的DDR 引脚复用配置,只需要设置DDR 引脚的电气属性即可,注意,DDR 引脚的电气属性寄存器和普通的外设引脚电气属性寄存器不同!

MMDC 控制器时钟源

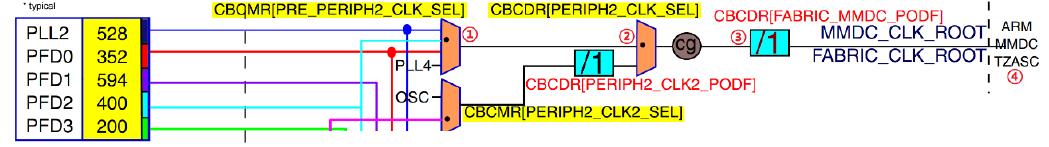

前面说了很多次,I.MX6U 的DDR 或者MDDC 的时钟频率为400MHz,那么这400MHz 时钟源怎么来的呢?这个就要查阅I.MX6ULL 参考手册的《Chapter 18 Clock Controller Module(CCM)》章节。MMDC 时钟源如图23.3.3.1 所示:

图23.3.3.1 就是MMDC 的时钟源路径图,主要分为4 部分,我们依次来看一下每部分所组的工作:

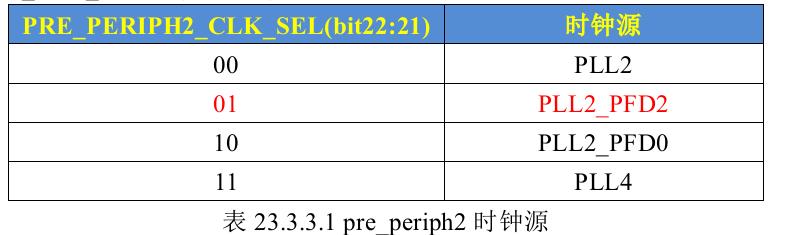

①、pre_periph2 时钟选择器,也就是periph2_clkd 的前级选择器,由CBCMR 寄存器的PRE_PERIPH2_CLK_SEL 位(bit22:21)来控制,一共有四种可选方案,如表23.3.3.1 所示:

从表23.3.3.1 可以看出,当PRE_PERIPH2_CLK_SEL 为0x1 的时候选中PLL2_PFD2 为pre_periph2 时钟源。在前面的《第十六章主频和时钟配置》中我们已经将PLL2_PFD2 设置为396MHz(约等于400MHz),I.MX6U 内部boot rom 就是设置PLL2_PFD2 作为MMDC 的最终时钟源,这就是I.MX6U 的DDR 频率为400MHz 的原因。

②、periph2_clk 时钟选择器,由CBCDR 寄存器的PERIPH2_CLK_SEL 位(bit26)来控制,当为0 的时候选择pll2_main_clk 作为periph2_clk 的时钟源,当为1 的时候选择periph2_clk2_clk作为periph2_clk 的时钟源。这里肯定要将PERIPH2_CLK_SEL 设置为0,也就是选择pll2_main_clk 作为periph2_clk 的时钟源,因此periph2_clk=PLL2_PFD0=396MHz。

③、最后就是分频器,由CBCDR 寄存器的FABRIC_MMDC_PODF 位(bit5:3)设置分频值,可设置0~ 7,分别对应1~8 分频,要配置MMDC 的时钟源为396MHz,那么此处就要设置为1分频,因此FABRIC_MMDC_PODF=0。

以上就是MMDC 的时钟源设置,I.MX6U 参考手册一直说DDR 的频率为400MHz,但是实际只有396MHz,就和NXP 宣传自己的I.MX6ULL 有800MHz 一样,实际只有792MHz。

ALPHA 开发板DDR3L 原理图

ALPHA 开发板有EMMC 和NAND 两种核心板,EMMC 核心板使用的DDR3L 的型号为NT5CC256M16EP-EK,容量为512MB。NAND 核心板使用的DDR3L 型号为NT5CC128M16JR-EK,容量为256MB,这两种型号的DDR3L 封装一摸一样,有人可能就有疑问了,容量不同的话地址线是不同的,比如行地址和列地址线数就不同,没错!但是DDR3L 厂商为了方便选择

将不同容量的DDR3 封装做成一样,没有用到的地址线DDR3L 芯片会屏蔽掉。而且,根据规定,所有厂商的DDR 芯片IO 一摸一样,不管是引脚定义还是引脚间距,但是芯片外形大小可能不同。因此只要做好硬件,可以在不需要修改硬件PCB 的前提下,随意的更换不同容量、不同品牌的DDR3L 芯片,极大的方便了我们的芯片选型。

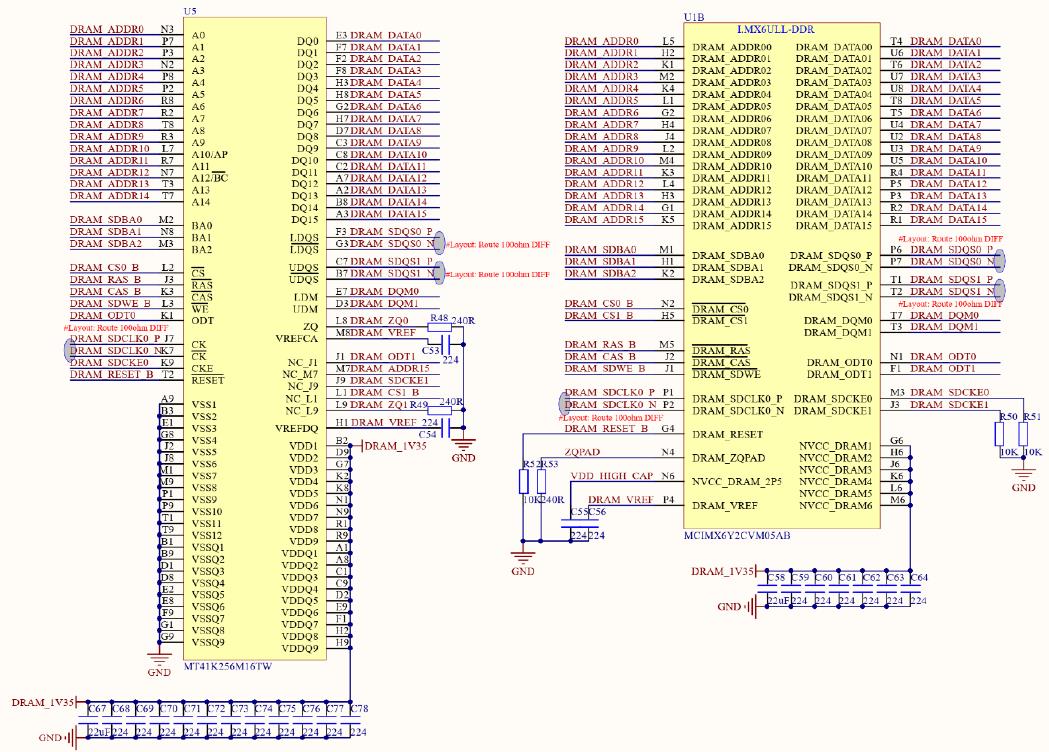

正点原子ALPHA 开发板EMMC 和NAND 核心板的DDR3L 原理图一样,如图23.4.1 所示:

图23.4.1 中左侧是DDR3L 原理图,可以看出图中DDR3L 的型号为MT41K256M16TW,这个是镁光的512MB DDR3L。但是我们实际使用的512MB DDR3L 型号为NT5CC256M16EP-EK,不排除以后可能会更换DDR3L 型号,更换DDR3L 芯片是不需要修改PCB。图23.4.1 中右边的是I.MX6U 的MMDC 控制器IO。

以上是关于NXP(I.MX6uLL)DDR3实验——DDR3重要时间参数时钟配置与原理图简析的主要内容,如果未能解决你的问题,请参考以下文章

i.MX6ULL系统移植 | 移植NXP官方 linux 5.4 内核