NXP(I.MX6uLL)DDR3实验——DDR3初始化校准超频测试

Posted 行稳方能走远

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了NXP(I.MX6uLL)DDR3实验——DDR3初始化校准超频测试相关的知识,希望对你有一定的参考价值。

ddr_stress_tester 简介

NXP 提供了一个非常好用的DDR 初始化工具,叫做ddr_stress_tester。此工具已经放到了开发板光盘中,路径为:5 、开发工具->5 、NXP 官方DDR 初始化与测试工具->ddr_stress_tester_v2.90_setup.exe.zip,我们简单介绍一下ddr_stress_tester 工具,此工具特点如

下:

①、此工具通过USB OTG 接口与开发板相连接,也就是通过USB OTG 口进行DDR 的初始化与测试。

②、此工具有一个默认的配置文件,为excel 表,通过此表可以设置板子的DDR 信息,最后生成一个.inc 结尾的DDR 初始化脚本文件。这个.inc 文件就包含了DDR 的初始化信息,一般都是寄存器地址和对应的寄存器值。

③、此工具会加载.inc 表里面的DDR 初始化信息,然后通过USB OTG 接口向板子下载DDR 相关的测试代码,包括初始化代码。

④、对此工具进行简单的设置,即可开始DDR 测试,一般要先做校准,因为不同的PCB其结构肯定不同,必须要做一次校准,校准完成以后会得到两个寄存器对应的校准值,我们需要用这个新的校准值来重新初始化DDR。

⑤、此工具可以测试板子的DDR 超频性能,一般认为DDR 能够以超过标准工作频率10%~20%稳定工作的话就认定此硬件DDR 走线正常。

⑥、此工具也可以对DDR 进行12 小时的压力测试。

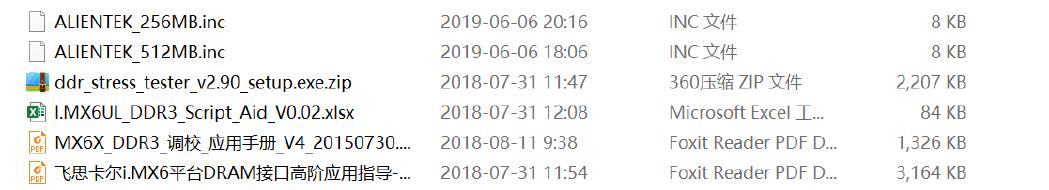

我们来看一下正点原子开发板光盘里面5、开发工具->6、NXP 官方DDR 初始化与测试工具目录下的文件,如图23.5.1.1 所示:

我们依次来看一下图23.5.1.1 中的这些文件的作用:

- ①、ALIENTEK_256MB.inc 和ALIENTEK_512MB.inc,这两个就是通过excel 表配置生成的,针对正点原子开发板的DDR 配置脚本文件。

- ②、ddr_stress_tester_v2.90_setup.exe.zip 就是我们要用的ddr_stress_tester 软件,大家自行安装即可,一定要记得安装路径。

- ③、I.MX6UL_DDR3_Script_Aid_V0.02.xlsx 就是NXP 编写的针对I.MX6UL 的DDR 初始化execl 文件,可以在此文件里面填写DDR 的相关参数,然后就会生成对应的.inc 初始化脚本。

- ④、最后两个PDF 文档就是关于I.MX6 系列的DDR 调试文档,这两个是NXP 编写的。

DDR3L 驱动配置

1、安装ddr_stress_tester

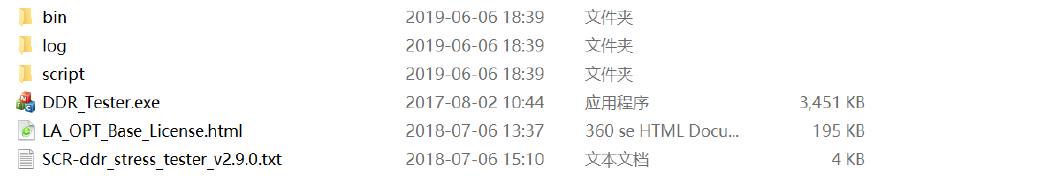

首先要安装ddr_stress_testr 软件,安装方法很简单,这里就不做详细的讲解了。但是一定要记得安装路径!因为我们要到安装路径里面找到测试软件。比如我安装到了D:\\Program Files (x86)里面,安装完成以后就会在此目录下生成一个名为ddr_stress_tester_v2.90 的文件夹,此文件夹就是DDR 测试软件,进入到此文件夹中,里面的文件如图23.5.2.1 所示:

图23.5.2.1 中的DDR_Tester.exe 就是我们稍后要使用的DDR 测试软件。

2、配置DDR3L,生成初始化脚本

将开发板光盘中的:5 、开发工具->5 、NXP 官方DDR 初始化与测试工具

->I.MX6UL_DDR3_Script_Aid_V0.02.xlsx 文件拷贝到ddr_stress_testr 软件安装目录中,完成以后如图23.5.2.2 所示:

I.MX6UL_DDR3_Script_Aid_V0.02.xlsx 就是NXP 为I.MX6UL 编写的DDR3 配置excel 表,虽然看名字是为I.MX6UL 编写的,但是I.MX6ULL 也是可以使用的。

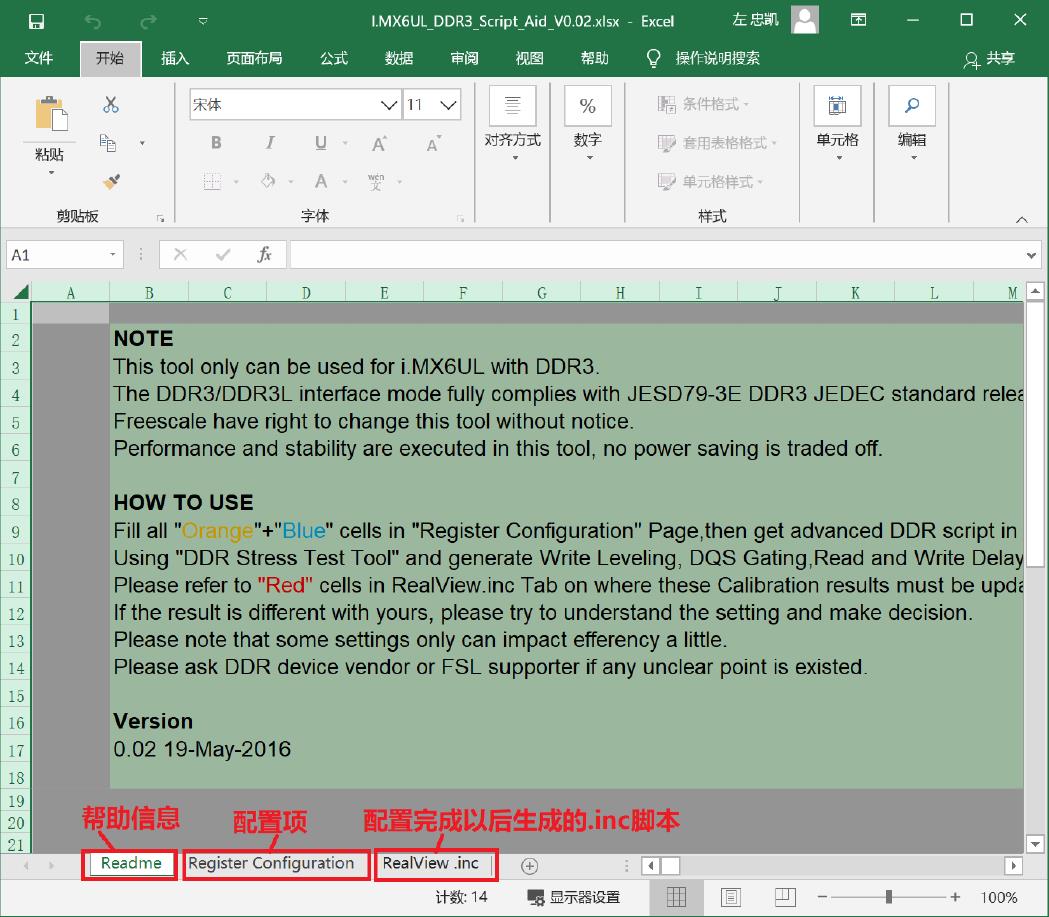

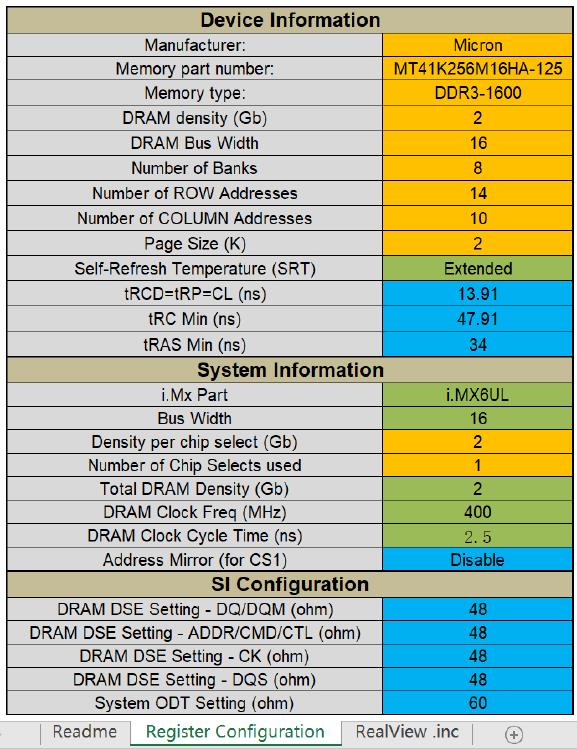

打开I.MX6UL_DDR3_Script_Aid_V0.02.xlsx,打开以后如图23.5.2.3 所示:

图23.5.2.3 中最下方有三个选项卡,这三个选项卡的功能如下:

- ①、Readme 选项卡,此选项卡是帮助信息,告诉用户此文件如何使用。

- ②、Register Configuration 选项卡,顾名思义,此选项卡用于完成寄存器配置,也就是配置DDR3,此选项卡是我们重点要讲解的。

- ③、RealView.inc 选项卡,当我们配置好Register Configuration 选项卡以后,RealView.inc选项卡里面就保存着寄存器地址和对应的寄存器值。我们需要另外新建一个后缀为.inc 的文件来保存RealView.inc 中的初始化脚本内容,ddr_stress_testr 软件就是要使用此.inc 结尾的初始化脚本文件来初始化DDR3。

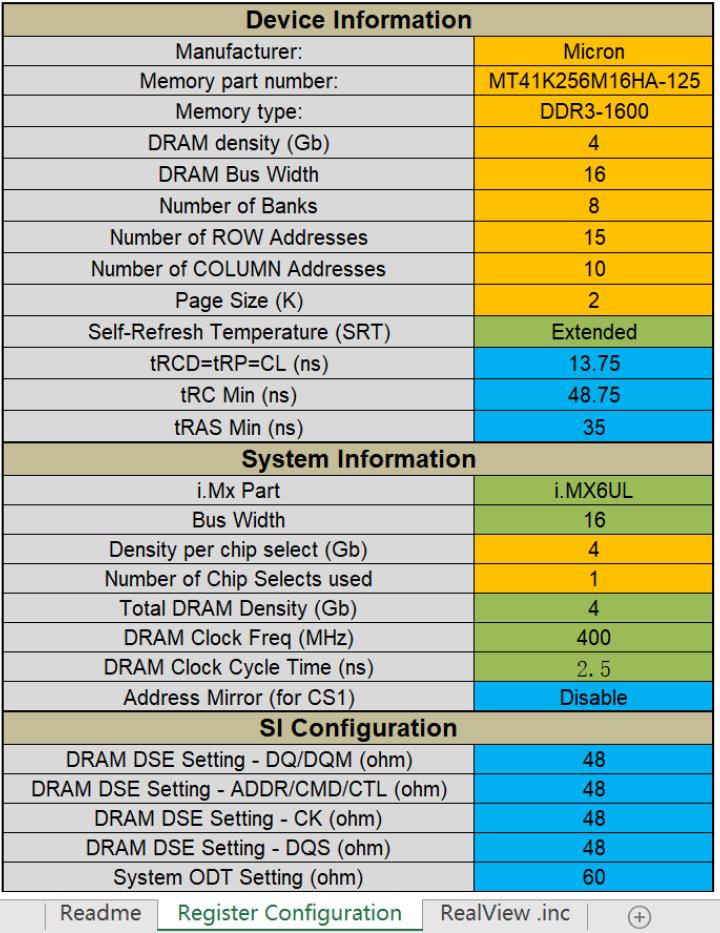

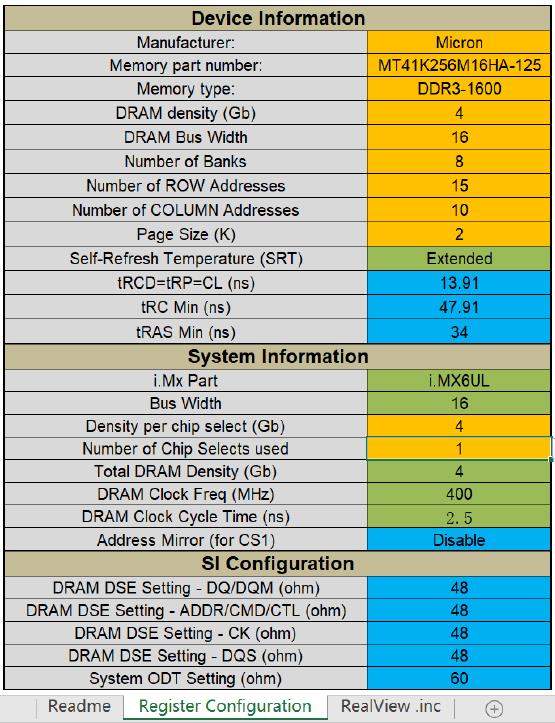

选中“Register Configuration”选项卡,如图23.5.2.4 所示:

图23.5.2.4 就是具体的配置界面,主要分为三部分:

①、Device Information

DDR3 芯片设备信息设置,此部分需要根据所使用的DDR3 芯片来设置,具体的设置项如下:

Manufacturer:DDR3 芯片厂商,默认为镁光(Micron),这个没有意义,比如我们用的nanya的DDR3,但是此配置文件也是可以使用的。

Memory part number:DDR3 芯片型号,可以不用设置,没有实际意义。

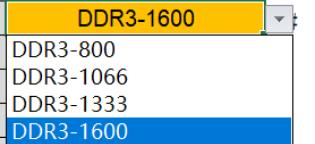

Memory type:DDR3 类型,有DDR3-800、DDR3-1066、DDR3-1333 和DDR3-1600,在此选项右侧有个下拉箭头,点击下拉箭头即可查看所有的可选选项,如图23.5.2.5 所示:

从图23.5.2.5 可以看出,最大只能选择DDR3-1600,没有DDR3-1866 选项,因此我们就只能选择DDR3-1600。

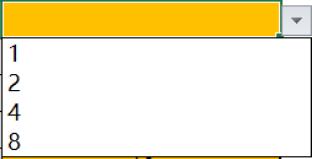

DRAM density(Gb):DDR3 容量,根据实际情况选择,同样右边有个下拉箭头,打开下拉箭头即可看到所有可选的容量,如图23.5.2.6 所示:

从图23.5.2.6 可以看出,可选的容量为1、2、4 和8Gb,如果使用的512MB 的DDR3 就应该选择4,如果使用的256MB 的DDR3 就应该选择2。

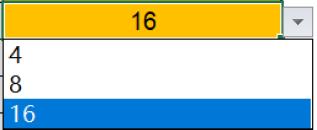

DRAM Bus width:DDR3 位宽,可选的选项如图23.5.2.7 所示:

正点原子ALPHA 开发板所有的DDR3 都是16 位宽,因此选择16。

Number of Banks:DDR3 内部BANK 数量,对于DDR3 来说内部都是8 个BANK,因此固定为8。

Number of ROW Addresses:行地址宽度,可选11~16 位,这个要具体所使用的DDR3 芯片来定,如果是EMMC 核心板(DDR3 型号为NT5CC256M16EP-EK),那么行地址为15 位。如果是NAND 核心板(DDR3 型号为NT5CC128M16JR-EK),行地址就为14 位。

Number COLUMN Addresses:列地址宽度,可选9~12 位,EMMC 核心板和NAND 核心板的DDR3 列地址都为10 位。

Page Size(K):DDR3 页大小,可选1 和2,NT5CC256M16EP-EK 和NT5CC128M16JR-EK的页大小都为2KB,因此选择2。

Self-Refresh Temperature(SRT):固定为Extended,不需要修改。

tRCD=tRP=CL(ns):DDR3 的tRCD-tRP-CL 时间参数,要查阅所使用的DDR3 芯片手册,NT5CC256M16EP-EK 和NT5CC128M16JR-EK 都为13.91ns,因此在后面填写13.91。

tRC Min(ns):DDR3 的tRC 时间参数,NT5CC256M16EP-EK 和NT5CC128M16JR-EK 都为47.91ns,因此在后面填写47.91。

tRAS Min(ns):DDR3 的tRAS 时间参数,NT5CC256M16EP-EK 和NT5CC128M16JR-EK都为34ns,因此在后面填写34。

②、System Information

此部分设置I.MX6UL/6ULL 相关属性,具体的设置项如下:

i.Mx Part:固定为i.MX6UL。

Bus Width:总线宽度,16 位宽。

Density per Chip select(Gb):每个片选对应的DDR3 容量,可选1~16,根据实际所使用的DDR3 芯片来填写,512MB 的话就选择4,256MB 的话就选择2。

Number of Chip Select used:使用几个片选信号?可选择1 或2,正点原子所有的核心板都只使用了一个片选信号,因此选择1。

Total DRAM Density(Gb):整个DDR3 的容量,单位为Gb,如果是512MB 的话就是4,如果是256MB 的话就是2。

DRAM Clock Freq(MHz):DDR3 工作频率,设置为400MHz。

DRAM Clock Cycle Time(ns):DDR3 工作频率对应的周期,单位为ns,如果工作在400MHz,那么周期就是2.5ns。

Address Mirror(for CS1):地址镜像,仅CS1 有效,此处选择关闭,也就是“Disable”,此选项我们不需要修改。

③、SI Configuratin

此部分是信号完整性方面的配置,主要是一些信号线的阻抗设置,这个要咨询硬件工程师,这里我们直接使用NXP 的默认设置即可。

关于DDR3 的配置我们就讲解到这里,如果是EMMC 核心板(DDR3 型号为

NT5CC256M16EP-EK),那么配置如图23.5.2.8 所示:

NAND 核心板配置(DDR3 型号为NT5CC128M16JR-EK)配置如图23.5.2.9 所示:

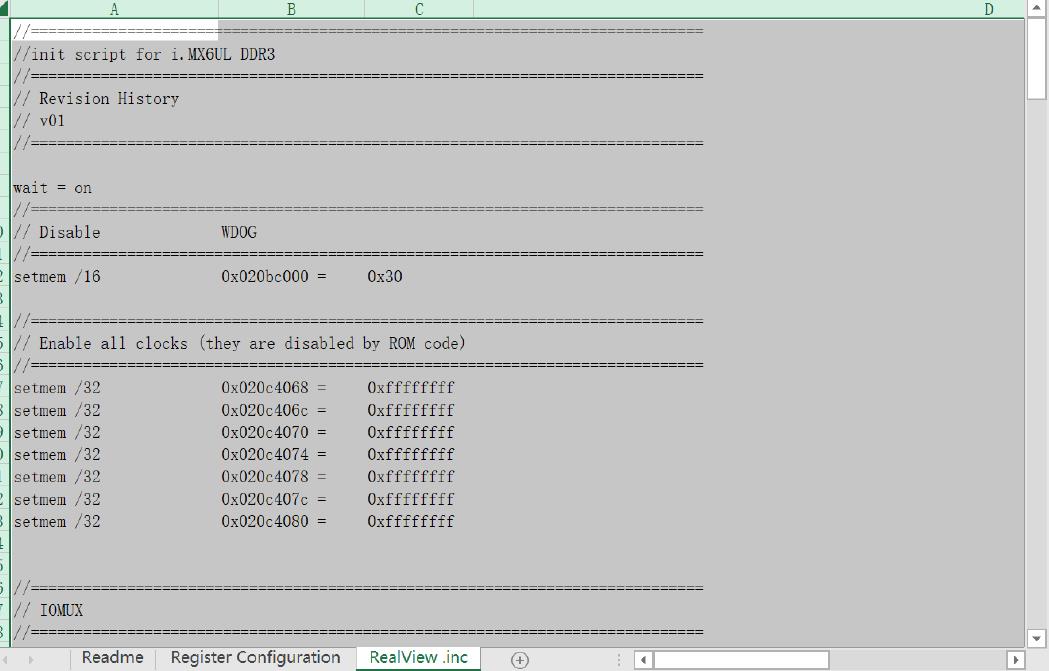

后面我就以EMMC 核心板为例讲解了,配置完成以后点击RealView.inc 选项卡,如图23.5.2.10 所示:

图23.5.2.10 中的RealView.inc 就是生成的配置脚本,全部是“寄存器地址=寄存器值”这种形式。RealView.inc 不能直接用,我们需要新建一个以.inc 结尾的文件,名字自定义,比如我名为“ALIENTEK_512MB”的.inc 文件,如图23.5.2.11 所示:

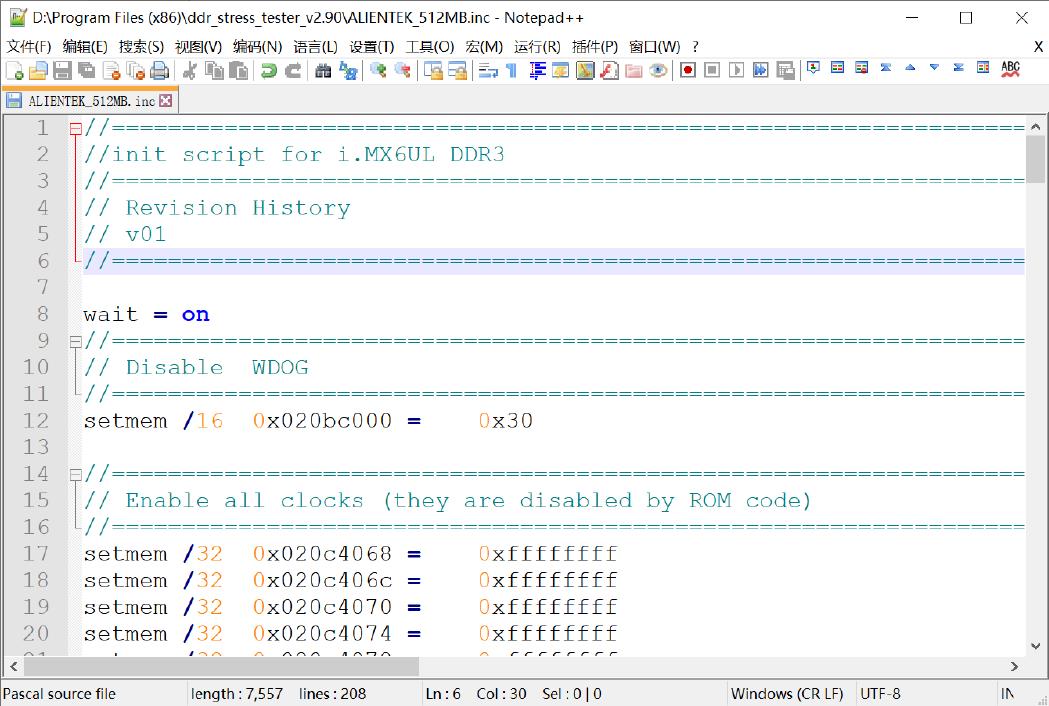

用notepad++打开ALIENTEK_512MB.inc 文件,然后将图23.5.2.10 中RealView.inc 里面的所有内容全部拷贝到ALIENTEK_512MB.inc 文件中,完成以后如图23.5.2.12 所示:

至此,DDR3 配置就全部完成,DDR3 的配置文件ALIENTEK_512MB.inc 已经得到了,接下来就是使用此配置文件对正点原子ALPHA 开发板的DDR3 进行校准并进行超频测试。

DDR3L 校准

首先要用DDR_Tester.exe 软件对正点原子ALPAH 开发板的DDR3L 进行校准,因为不同的PCB 其走线不同,必须要进行校准,经过校准一会DDR3L 就会工作到最佳状态。

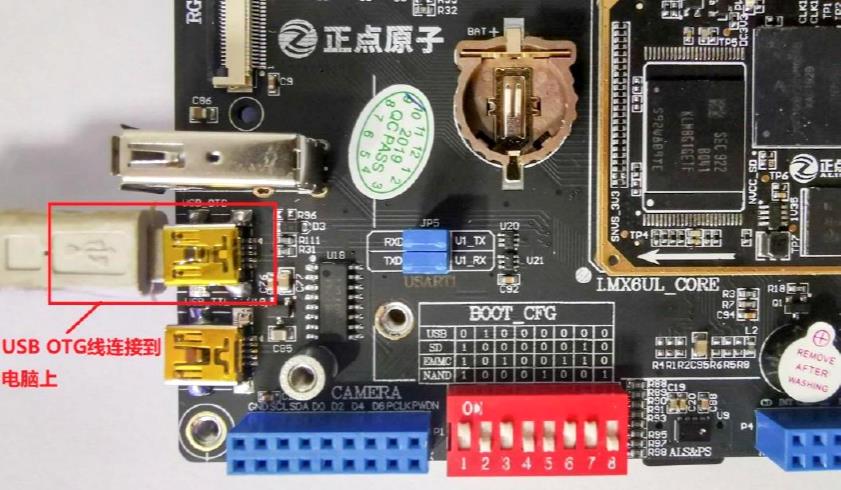

1、将开发板通过USB OTG 线连接到电脑上

DDR_Tester 软件通过USB OTG 线将测试程序下载到开发板中,因此首先需要使用USB OTG 线将开发板和电脑连接起来,如图23.5.3.1 所示:

USB OTG 线连接成功以后还需要如下两步:

①、弹出TF 卡,如果插入了TF 卡,那么一定要弹出来!!

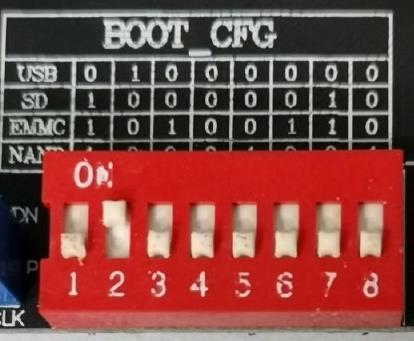

②、设置拨码开关从USB 启动,如图23.5.3.2 所示:

2、DDR_Tester 软件

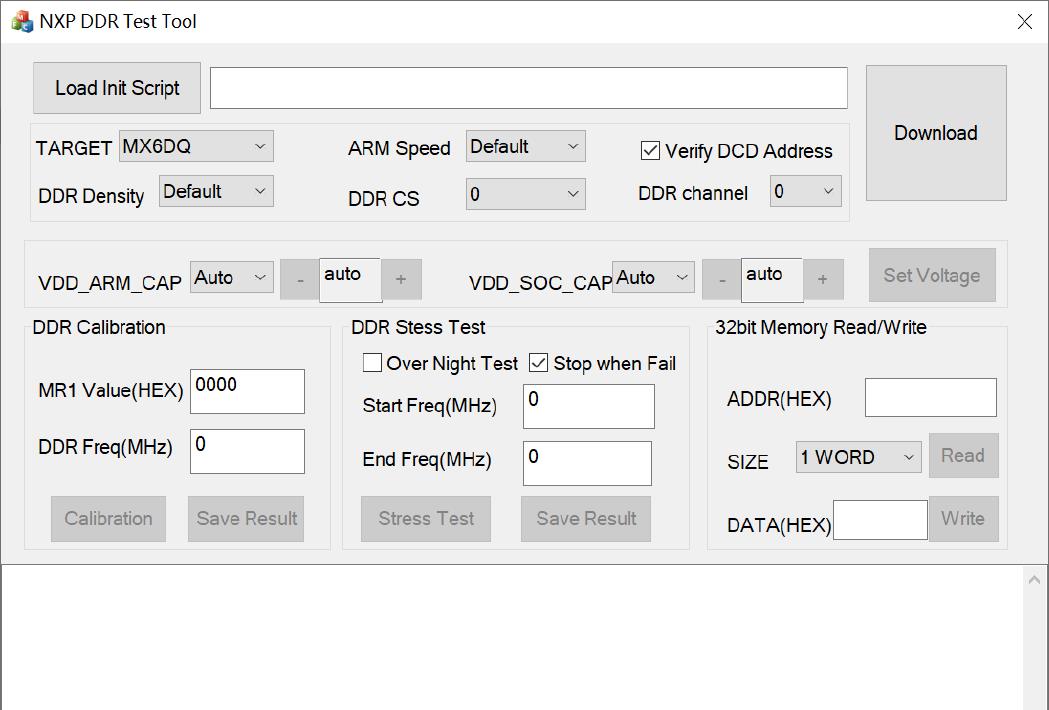

双击“DDR_Tester.exe”,打开测试软件,如图23.5.3.3 所示:

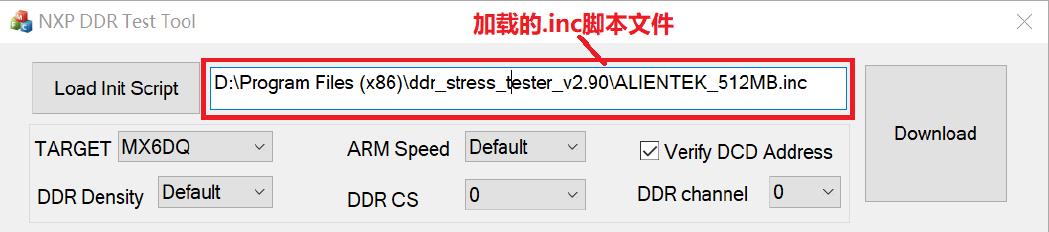

点击图23.5.3.3 中的“Load init Script ”加载前面已经生成的初始化脚本文件

ALIENTEK_512MB.inc,注意,不能有中文路径,否则加载可能会失败!完成以后如图23.5.3.4所示:

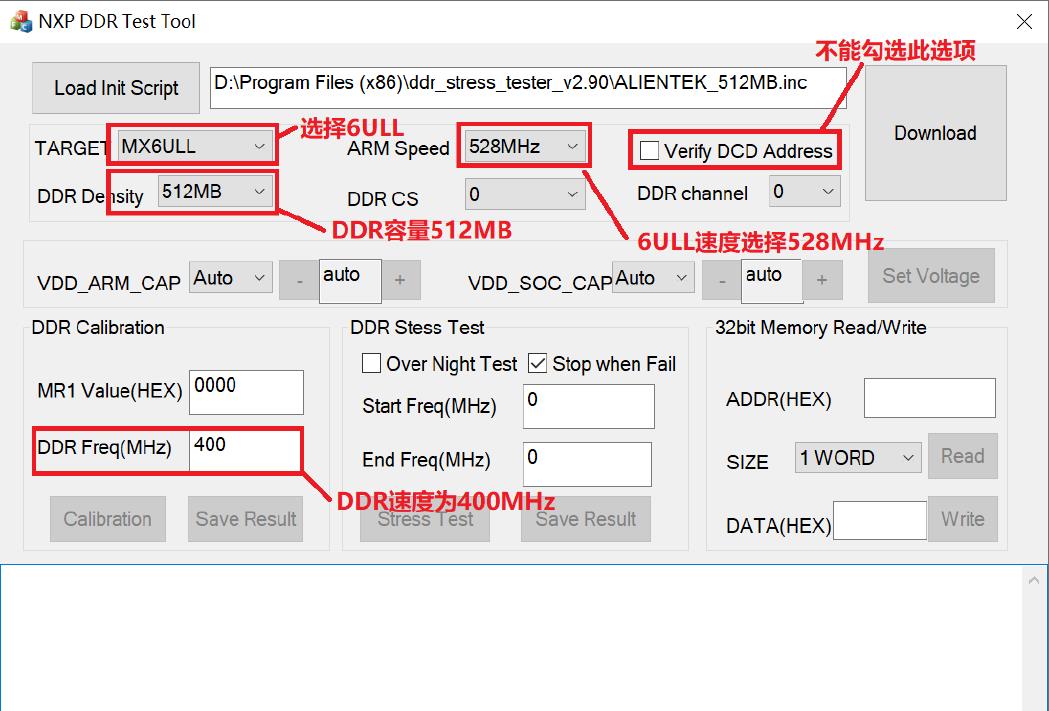

ALIENTEK_512MB.inc 文件加载成功以后还不能直接用,还需要对DDR Test Tool 软件进行设置,设置完成以后如图23.5.3.5 所示:

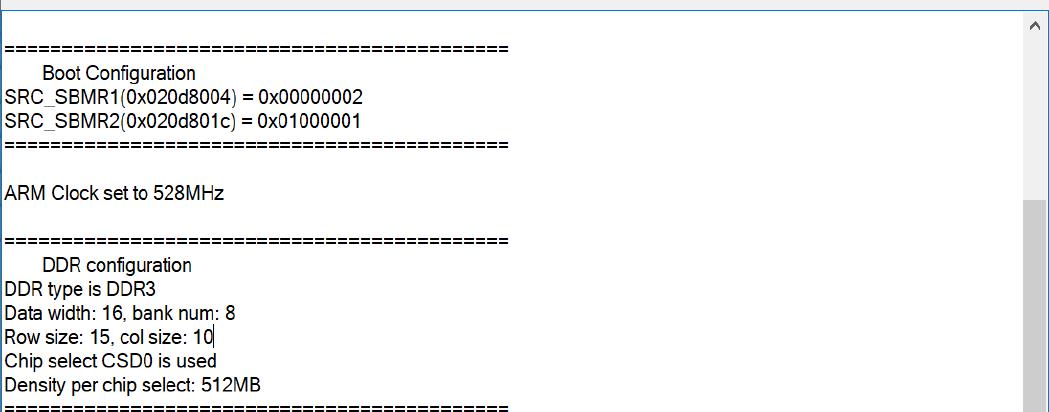

一切设置好以后点击图23.5.3.5 中右上方大大的“Download”按钮,将测试代码下载到开发板中(具体下载到哪里笔者也不清楚,估计是I.MX6ULL 内部的OCRAM),下载完成以后DDR Test Tool 下方的信息窗口就会输出一些内容,如图23.5.3.6 所示:

图23.5.3.6 输出了一些关于板子的信息,比如SOC 型号、工作频率、DDR 配置信息等等。

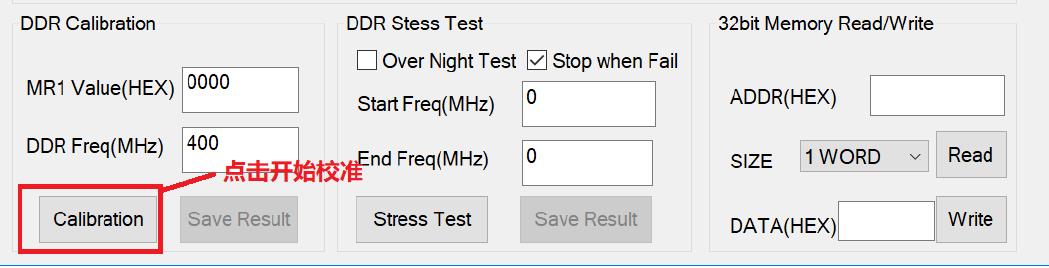

DDR Test Tool 工具有三个测试项:DDR Calibration、DDR Stess Test 和32bit Memory Read/Write,我们首先要做校准测试,因为不同的PCB、不同的DDR3L 芯片对信号的影响不同,必须要进行校准,然后用新的校准值重新初始化DDR。点击“Calibraton”按钮,如图23.5.3.7 所示:

点击图23.5.3.7 中的“Calibration”按钮以后就会自动开始校准,最终会得到Write levelingcalibtarion、Read DQS Gating Calibration、Read calibration 和Write calibration,一共四种校准结果,校准结果如下:

1 Write leveling calibration

2 MMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x00000000

3 MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x000B000B

4

5 Read DQS Gating calibration

6 MPDGCTRL0 PHY0 (0x021b083c) = 0x0138013C

7 MPDGCTRL1 PHY0 (0x021b0840) = 0x00000000

8

9 Read calibration

10 MPRDDLCTL PHY0 (0x021b0848) = 0x40402E34

11

12 Write calibration

13 MPWRDLCTL PHY0 (0x021b0850) = 0x40403A34

所谓的校准结果其实就是得到了一些寄存器对应的值,比如MMDC_MPWLDECTRL0 寄存器地址为0X021B080C,此寄存器是PHY 写平衡延时寄存器0,经过校准以后此寄存器的值应该为0X00000000 ,以此类推。我们需要修改ALIENTEK_512MB.inc 文件,找到

MMDC_MPWLDECTRL0、MMDC_MPWLDECTRL1、MPDGCTRL0 PHY0、MPDGCTRL1 PHY0、MPRDDLCTL PHY0 和MPWRDLCTL PHY0 这6 个寄存器,然后将其值改为示例代码23.5.3.1中的校准后的值。注意,在ALIENTEK_512MB.inc 中可能找不到MMDC_MPWLDECTRL1(0x021b0810)和MPDGCTRL1 PHY0(0x021b0840)这两个寄存器,找不到就不用修改了。

ALIENTEK_512MB.inc 修改完成以后重新加载并下载到开发板中,至此DDR 校准完成,校准的目的就是得到示例代码23.5.3.1 中这6 个寄存器的值!

DDR3L 超频测试

校准完成以后就可以进行DDR3 超频测试,超频测试的目的就是为了检验DDR3 硬件设计合不合理,一般DDR3 能够超频到比标准频率高10%~ 15%的话就认为硬件没有问题,因此对于正点原子的ALPHA 开发板而言,如果DDR3 能够超频到440MHz~460MHz 那么就认为DDR3 硬件工作良好。

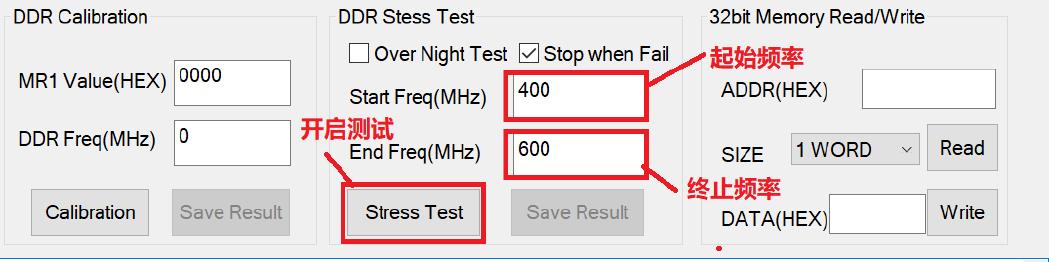

DDR Test Tool 支持DDR3 超频测试,只要指定起始频率和终止频率,那么工具就会自动开始一点点的增加频率,直到达到终止频率或者测试失败。设置如图23.5.4.1 所示:

图23.5.4.1 中设置好起始频率为400MHz,终止频率为600MHz,设置好以后点击“StressTest”开启超频测试,超频测试时间比较久,大家耐心等待测试结果即可。超频测试完成以后结果如图23.5.4.2 所示(因为硬件不同,测试结果可能有些许区别):

从图23.5.4.2 可以看出,正点原子的ALPAH 开发板EMMC 核心板DDR3 最高可以超频到556MHz,当超频到561MHz 的时候就失败了。556MHz 超过了460MHz,说明正点原子的ALPHA开发板DDR3 硬件是没有任何问题的。

DDR3L 驱动总结

ALIENTEK_512MB.inc 就是我们最终得到的DDR3L 初始化脚本,其中包括了时钟、IO 等初始化。I.MX6U 的DDR3 接口关于IO 有一些特殊的寄存器需要初始化,如表23.5.5.1 所示:

| 寄存器地址 | 寄存器名 | 寄存器值 |

|---|---|---|

| 0X020E04B4 | IOMUXC_SW_PAD_CTL_GRP_DDR_TYPE | 0X000C0000 |

| 0X020E04AC | IOMUXC_SW_PAD_CTL_GRP_DDRPKE | 0X00000000 |

| 0X020E027C | IOMUXC_SW_PAD_CTL_PAD_DRAM_SDCLK_0 | 0X00000028 |

| 0X020E0250 | IOMUXC_SW_PAD_CTL_PAD_DRAM_CAS | 0X00000028 |

| 0X020E024C | IOMUXC_SW_PAD_CTL_PAD_DRAM_RAS | 0X00000028 |

| 0X020E0490 | IOMUXC_SW_PAD_CTL_GRP_ADDDS | 0X00000028 |

| 0X020E0288 | IOMUXC_SW_PAD_CTL_PAD_DRAM_RESET | 0X00000028 |

| 0X020E0270 | IOMUXC_SW_PAD_CTL_PAD_DRAM_SDBA2 | 0X00000000 |

| 0X020E0260 | IOMUXC_SW_PAD_CTL_PAD_DRAM_SDODT0 | 0X00000028 |

| 0X020E0264 | IOMUXC_SW_PAD_CTL_PAD_DRAM_SDODT1 | 0X00000028 |

| 0X020E04A0 | IOMUXC_SW_PAD_CTL_GRP_CTLDS | 0X00000028 |

| 0X020E0494 | IOMUXC_SW_PAD_CTL_GRP_DDRMODE_CTL | 0X00020000 |

| 0X020e0280 | IOMUXC_SW_PAD_CTL_PAD_DRAM_SDQS0 | 0X00000028 |

| 0X020E0284 | IOMUXC_SW_PAD_CTL_PAD_DRAM_SDQS1 | 0X00000028 |

| 0X020E04B0 | IOMUXC_SW_PAD_CTL_GRP_DDRMODE | 0X00020000 |

| 0X020e0498 | IOMUXC_SW_PAD_CTL_GRP_B0DS | 0X00000028 |

| 0X020E04A4 | IOMUXC_SW_PAD_CTL_GRP_B1DS | 0X00000028 |

| 0X020E0244 | IOMUXC_SW_PAD_CTL_PAD_DRAM_DQM0 | 0X00000028 |

| 0X020E0248 | IOMUXC_SW_PAD_CTL_PAD_DRAM_DQM1 | 0X00000028 |

接下来看一下MMDC 外设寄存器初始化,如表23.5.5.2 所示:

| 寄存器地址 | 寄存器名 | 寄存器值 |

|---|---|---|

| 0X021B0800 | DDR_PHY_P0_MPZQHWCTRL | 0XA1390003 |

| 0X021B080C | MMDC_MPWLDECTRL0 | 0X00000000 |

| 0X021B083C | MPDGCTRL0 | 0X0138013C |

| 0X021B0848 | MPRDDLCTL | 0X40402E34 |

| 0X021B0850 | MPWRDLCTL | 0X40403A34 |

| 0X021B081C | MMDC_MPRDDQBY0DL | 0X33333333 |

| 0X021B0820 | MMDC_MPRDDQBY1DL | 0X33333333 |

| 0X021B082C | MMDC_MPWRDQBY0DL | 0XF3333333 |

| 0X021B0830 | MMDC_MPWRDQBY1DL | 0XF3333333 |

| 0X021B08C0 | MMDC_MPDCCR | 0X00921012 |

| 0X021B08B8 | DDR_PHY_P0_MPMUR0 | 0X00000800 |

| 0X021B0004 | MMDC0_MDPDC | 0X0002002D |

| 0X021B0008 | MMDC0_MDOTC | 0X1B333030 |

| 0X021B000C | MMDC0_MDCFG0 | 0X676B52F3 |

| 0X021B0010 | MMDC0_MDCFG1 | 0XB66D0B63 |

| 0X021B0014 | MMDC0_MDCFG2 | 0X01FF00DB |

| 0X021b002c | MMDC0_MDRWD | 0X000026D2 |

| 0X021b0030 | MMDC0_MDOR | 0X006B1023 |

| 0X021b0040 | MMDC_MDASP | 0X0000004F |

| 0X021b0000 | MMDC0_MDCTL | 0X84180000 |

| 0X021b0890 | MPPDCMPR2 | 0X00400a38 |

| 0X021b0020 | MMDC0_MDREF | 0X00007800 |

| 0X021b0818 | DDR_PHY_P0_MPODTCTRL | 0X00000227 |

| 0X021b0004 | MMDC0_MDPDC | 0X0002556D |

| 0X021b0404 | MMDC0_MAPSR | 0X00011006 |

关于I.MX6U 的DDR3 就讲解到这里,因为牵扯到的寄存器太多了,因此没有详细的去分析这些寄存器,大家感兴趣的可以对照着参考手册去分析各个寄存器的含义以及配置值。

以上是关于NXP(I.MX6uLL)DDR3实验——DDR3初始化校准超频测试的主要内容,如果未能解决你的问题,请参考以下文章

i.MX6ULL系统移植 | 移植NXP官方 linux 5.4 内核