002 PLL - Phase Locked Loop

Posted SilentLittleCat

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了002 PLL - Phase Locked Loop相关的知识,希望对你有一定的参考价值。

功能

- 输出一个和输入信号同频、同相位(或有固定相位差)的信号

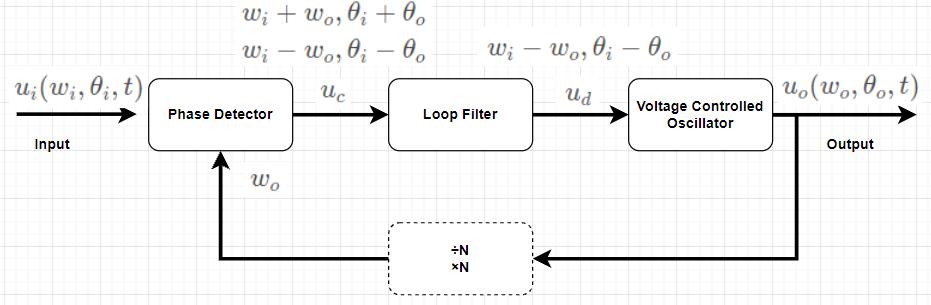

组成

- w o ÷ N = w i w_o \\div N=w_i wo÷N=wi

- w o × N = w i w_o \\times N=w_i wo×N=wi

- 负反馈是分频器(÷N)时,PLL为倍频电路

- 负反馈是倍频器(×N)时,PLL为分频电路

鉴相器(PD,Phase Detector)

- 比较输入和反馈信号的相位,输出一个和两个信号相位差相关的信号

正弦波鉴相器 - 模拟乘法器

u

i

=

U

i

s

i

n

[

w

i

t

+

θ

i

(

t

)

]

=

U

i

s

i

n

ϕ

i

u_i=U_isin[w_it+\\theta_i(t)]=U_isin{\\phi_i}

ui=Uisin[wit+θi(t)]=Uisinϕi

u

o

=

U

o

c

o

s

[

w

o

t

+

θ

o

(

t

)

]

=

U

o

c

o

s

ϕ

o

u_o=U_ocos[w_ot+\\theta_o(t)]=U_ocos{\\phi_o}

uo=Uocos[wot+θo(t)]=Uocosϕo

u

c

=

A

m

u

i

u

o

=

1

2

A

m

u

i

u

o

{

s

i

n

[

(

w

i

+

w

o

)

t

+

θ

i

(

t

)

+

θ

o

(

t

)

]

+

s

i

n

[

(

w

i

−

w

o

)

t

+

θ

i

(

t

)

−

θ

o

(

t

)

]

}

u_c=A_mu_iu_o={1 \\over 2}A_mu_iu_o\\{sin[(w_i+w_o)t+\\theta_i(t)+\\theta_o(t)]+sin[(w_i-w_o)t+\\theta_i(t)-\\theta_o(t)]\\}

uc=Amuiuo=21Amuiuo{sin[(wi+wo)t+θi(t)+θo(t)]+sin[(wi−wo)t+θi(t)−θo(t)]}

u

c

=

K

d

{

s

i

n

[

(

w

i

+

w

o

)

t

+

θ

i

(

t

)

+

θ

o

(

t

)

]

+

s

i

n

[

(

w

i

−

w

o

)

t

+

θ

i

(

t

)

−

θ

o

(

t

)

]

}

u_c=K_d\\{sin[(w_i+w_o)t+\\theta_i(t)+\\theta_o(t)]+sin[(w_i-w_o)t+\\theta_i(t)-\\theta_o(t)]\\}

uc=Kd{sin[(wi+wo)t+θi(t)+θo(t)]+sin[(wi−wo)t+θi(t)−θo(t)]}

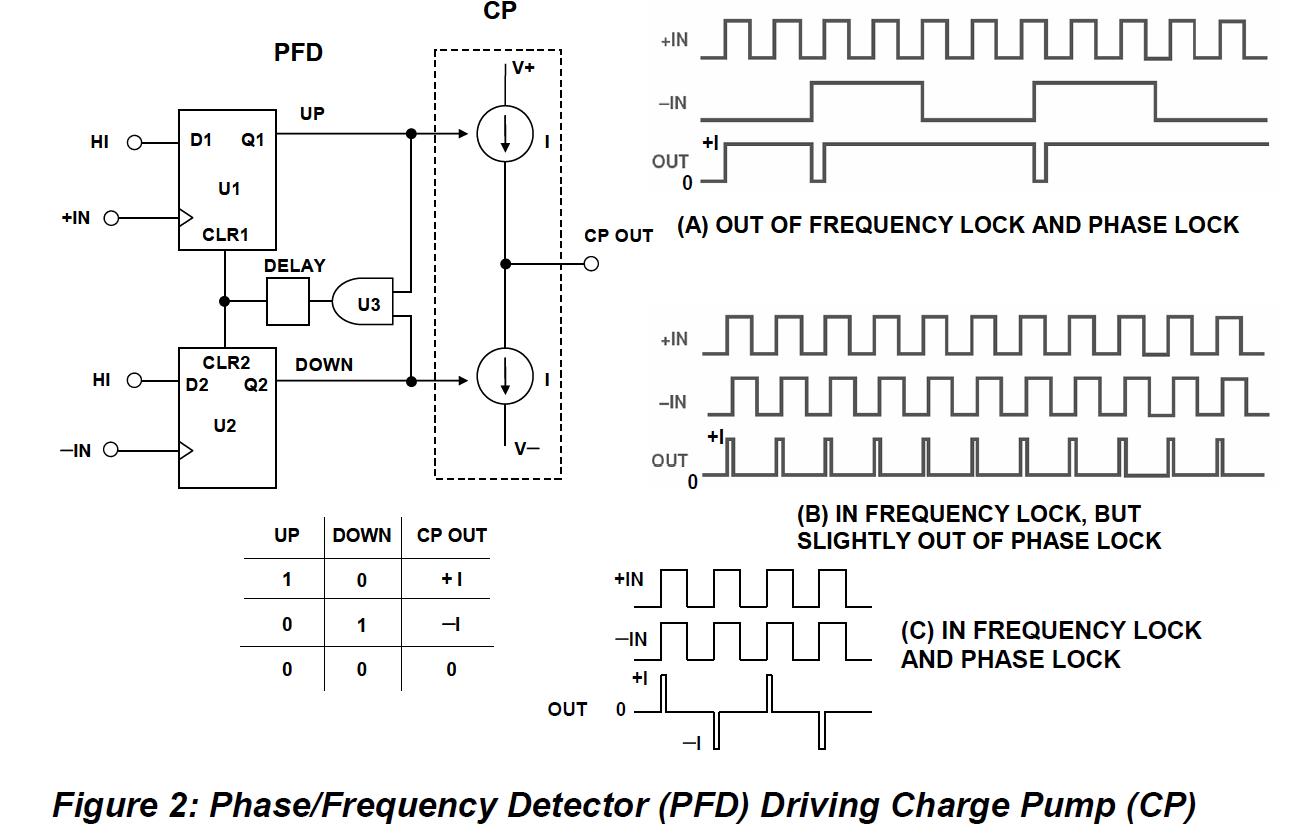

数字鉴相器

- w + I N > w − I N w_{+IN}>w_{-IN} w+IN>w−IN, O U T OUT OUT高电平比较多,CP充电,VCO调大 w − I N w_{-IN} w−IN

- w + I N < w − I N w_{+IN}<w_{-IN} w+IN<w−IN, O U T OUT OUT低电平比较多,CP放电,VCO调小 w − I N w_{-IN} w−IN

- 频率、相位锁定后,保持平衡

环路滤波器(LF,Loop Filter)

u c = K d { s i n [ ( w i + w o ) t + θ i ( t ) + θ o ( t ) ] + s i n [ ( w i − w o ) t + θ i ( t ) − θ o ( t ) ] } u_c=K_d\\{sin[(w_i+w_o)t+\\theta_i(t)+\\theta_o(t)]+sin[(w_i-w_o)t+\\theta_i(t)-\\theta_o(t)]\\} uc=Kd{sin[(wi+wo)t+θi(t)+θo(t)]+sin[(wi−wo)t+θ002 PLL - Phase Locked Loop