ADIsimPLL锁相环设计过程

Posted 豆豆学习精

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ADIsimPLL锁相环设计过程相关的知识,希望对你有一定的参考价值。

从软件的使用上开始研究:

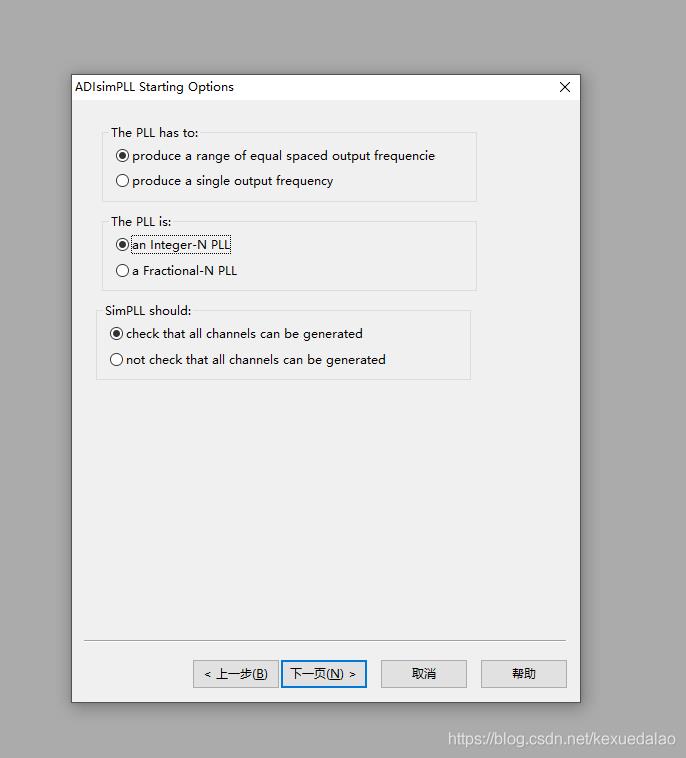

产生一个均匀的输出频率范围

产生一个单一的输出频率

整数-N-PLL

小数-N-PLL

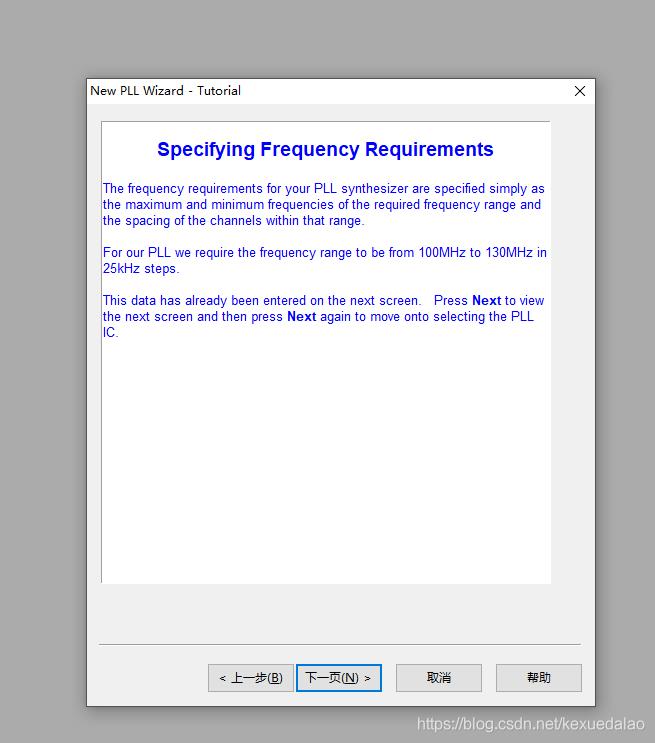

PLL合成器的频率要求被简单地指定为所需频率范围的最大和最小频率以及该范围内通道的间隔。

对于我们的锁相环,我们要求频率范围从100MHz到130MHz在25kHz步长。

这些数据已经在下一个屏幕上输入。按Next查看下一个屏幕,然后再按Next移动到选择PLL IC。

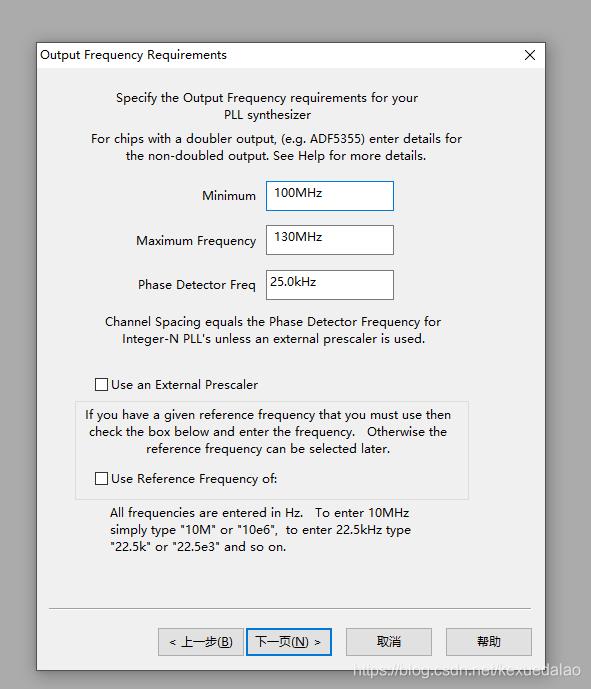

为你的PLL频率合成器指定输出频率

对于具有

以上是关于ADIsimPLL锁相环设计过程的主要内容,如果未能解决你的问题,请参考以下文章