ADS设计锁相环

Posted 豆豆学习精

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ADS设计锁相环相关的知识,希望对你有一定的参考价值。

前言:文章将讲述利用ADS2008版本去设计PLL,重点在于分析原理。

一、锁相环的基本工作原理

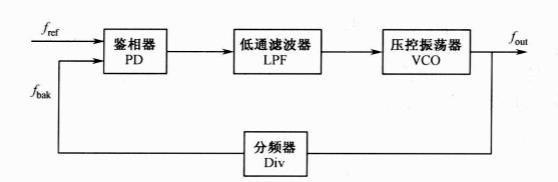

锁相环电路基本框图由4大部分组成,即压控振荡器(VCO)、鉴相器(PD)、分频器(Div)和环路滤波器(LPF),

(1)压控振荡器(VCO):

产生振荡信号。它的输出频率受直流电压控制,大多数vco的输出频率随控制电压升高而升高,即具有正斜率。

(2)分频器(Div):

对VCO的输出频率进行分频,使频率降低,以便于处理。

(3)鉴相器(PD):

对输入的参考频率fref和分频后的fbak进行相位比较,并根据fref与fbak相位差,产生(输出)对应的准DC电压。

(4)低通滤波器(LPF):

对鉴相器输出的电压进行滤波,为vco提供纯净的DC控制电压,同时为系统提供一定的稳定裕量,该低通滤波器也称为环路滤波器。

(5)原理:

PLL是一个频率/相位的自动控制系统。如果fout偏离期望的频率,则fbak与fref产生相差。此时,鉴相器会根据该相差输出对应的控制电压去迫使fout回到期望的频率;当fref变化时,鉴相器的两个输入频率会产生一定的频差,接着鉴相器输出电压会随相差的大小而改变,迫使fout变化到对应的频率,以保证fbak与fref相等。也就是说,可以通过改变fref使fout变化到希望的频率,同时fout还能够自动跟踪fref的变化,这个特点使PLL能够用作频率合成器

以上是关于ADS设计锁相环的主要内容,如果未能解决你的问题,请参考以下文章