锁相环倍频原理简要分析

Posted 嗜血的草

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了锁相环倍频原理简要分析相关的知识,希望对你有一定的参考价值。

以前学STM32的时候就知道了倍频这个概念。开发板上外接8M晶振,但是STM32主频却能跑72M,这离不开锁相环(PLL)的作用。之后在使用FPGA的时候,直接有PLL这个IP核提供给我们使用,实现自己想要的频率。但是当我们使用的时候,锁相环倍频的原理我们清楚吗?下面就来简要分析下倍频的原理。

首先,我们需要了解下锁相环的组成。锁相环是由一个鉴相器(PD)、低通滤波器(LPF)和压控振荡器(VCO)组成。结构图如下:

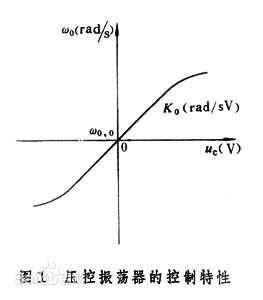

PLL需要有一个参考频率fi。输出频率为fo,参考频率与输出频率同时送入鉴相器。鉴相器的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出。当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环的名称由来。转换后的电压信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。压控振荡器(VCO)的控制特性如下:

当VCO的输入电压为0时,即输出频率fo=fi。

那么是如何实现倍频的呢?其实就是对输出fo作N分频,即fN,将分频后的频率送入鉴相器中与参考频率进行比较。当PLL进入锁定状态时,输出频率fo就实现了倍频,此时fo=N*fi。

以上是关于锁相环倍频原理简要分析的主要内容,如果未能解决你的问题,请参考以下文章